ポードの断面寸法は、コストを決める重要な要素ですが、ボード屋さんに任せきりになっていたり、何となく決めているケースをよくみかけます。

これまで数回にわたって、断面寸法について述べました。

以下も参照ください。

今回は、2回に分けて、多用されている基板パラメータを決定する近似式を検証し、それとは逆に、仕様から断面寸法を決めるツールの紹介の二つについて述べます。

このツールは、次回に紹介しますが、ツールだけはご希望の方にお渡しします。文末をご覧ください。

要求仕様

ボードの断面寸法を決めるための要求仕様(基板パラメータ)は、

(a)特性インピーダンス Z0

(b)配線密度 WとG

(c)クロストーク係数 ξ

などです。

(a)の特性インピーダンスZ0は、通常は、50Ωに選ぶことが多いです。

その理由は、

- 作りやすい、普通に作ると50Ω前後になる

- 複数のボードを接続するときに他と合わせておきたい

- 何となくきりがいい

でしょう。

測定器の50Ωとは、特殊な用途以外は関係ないと考えます。

ただ、なぜ50Ωにするのかを考えずに、何となく50Ωというのが実状でしょう。ただ、それで何も問題ありません。

CMOS以前の、TTLの時代は、そのドライバの特性から、波形伝送の上では、80Ωとか100Ωの特性インピーダンスが好都合でした。

豆知識 「TTLのZ0は100Ωが最適」を参照ください。

現在のCMOSは、トランジスタサイズを変えることにより、出力インピーダンス(オン抵抗)を容易に任意に選ぶことができるので、TTL時代のように、ドライバの特性によりボードの特性インピーダンスを選択する必然性はありません。むしろ、作りやすい50Ωに合わせたドライバを設計することが大切です。ただ、失礼ながら、ドライバメーカの意識不足により、そのようにドライバを設計していないので、オン抵抗値が最適値よりかなり小さい(駆動能力が大きい)のが実状です。したがって、Z0=50Ωのときに、波形乱れを少なくするために、ダンピング抵抗が必要になります。このことは少し残念です。

ダンピング抵抗については、何回か述べています。

以下を参照ください。

(b)は、歩留りの許す範囲でパターン幅Wを極力細く、パターン間ギャップGを極力狭く選んで、実装密度を上げることがコストの面から要求されます。

これは、極めて当然のことですが、残念ながら漫然と作られて、あまり考慮されてない例を多く見かけます。

(c)は、(b)のパターン間ギャップGの選定と相反することにもなりますが、Gをクロストークの要求仕様から決定します。Gを大きく選ぶとクロストークは小さくなります。

何となく決めるのではなく、ノイズバジェットから決めるべきと考えます。

解析ソフト(ソルバー)

断面寸法から電気的仕様を求めるには、専用のツールを用います。

筆者は、

GreenExpress V2

GreenExpress Professional

を用いていますが、残念ながら、これらの製品は終息して、入手できません。

他には、Polar Instruments社の製品がありますが、少し高価です。

回路解析ソフトに付属しているものもあるようです。

他にも、あると思いますが、あまり調べていません。

マイクロストリップ線路 = 表面層

簡単に求めるために、いくつかの近似式が提案されています。

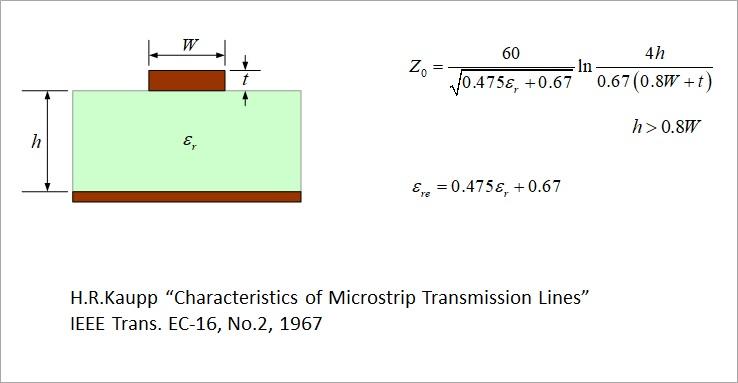

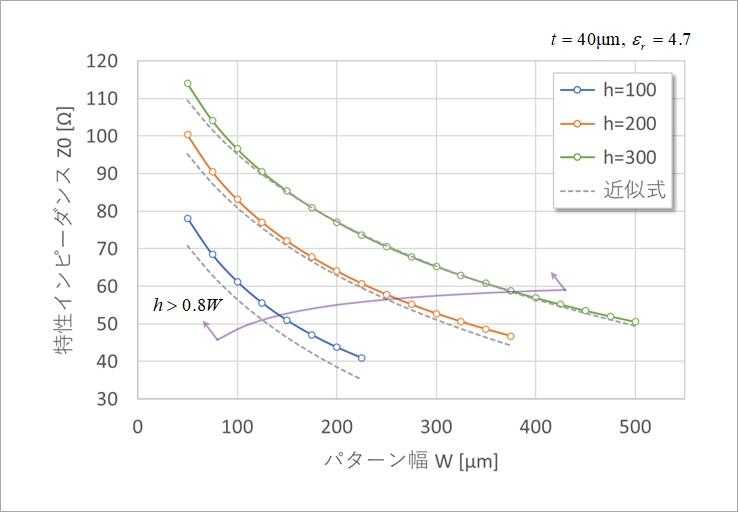

有名なのは、図1に示す、1967年のKauppの論文です。

ただ、半世紀も前なので、ボードのディメンションが現在の仕様とはかけ離れています。いくつかの前提条件がありますが、これらをきちんと考慮せずに、この近似式が独り歩きしている感じです。

以下に、この論文の内容を元に解説しますが、この論文を批判するものではなく、当時の材料や寸法に対する近似が、半世紀も用いられたことは素晴らしいことで敬意を表します。ただ、当時と寸法条件が異なる現在、きちんと見直す必要があるでしょう。

等価比誘電率

図1のεreは、マイクロストリップ線路の等価比誘電率です。

この式は、パターン幅Wや厚みtおよびグラウンドからの距離(高さ)hが含まれていません。

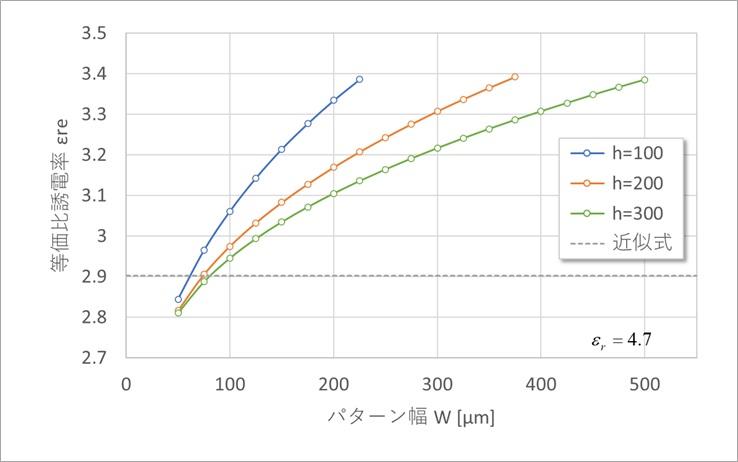

図2は、これらを変えたときの等価比誘電率を計算により求めました。εr=4.7のときに、Kauppの近似式では、εre=2.9ですが、Wとhにより、2.8から3.4まで変化します。

εreの平方根が遅延時間に影響します。平方根で効くので、数パーセントの誤差ですが、意識しておく必要があります。

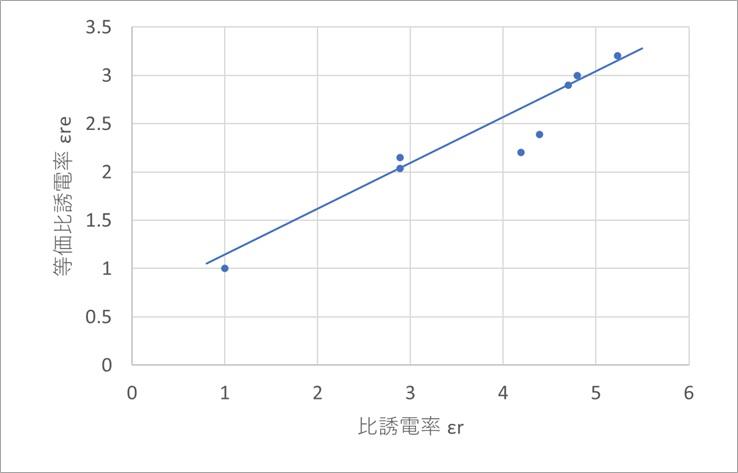

図3は、Kauppの論文に記載された等価比誘電率を求めたときのプロットと近似直線です。比誘電率が1から5.2程度のサンプルに対して直線近似しています。実際のプリント配線板で用いられる比誘電率は、4から5程度なので、この範囲では、近似式からかなり外れます。

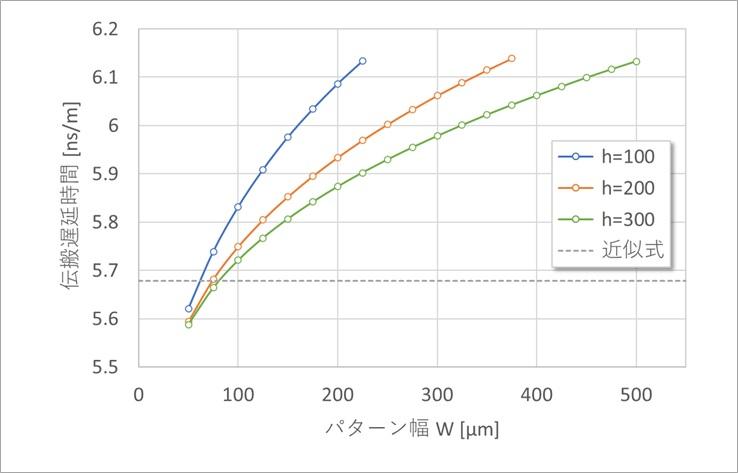

図4は、同じく伝搬遅延時間です。5.6ns/mから6.1ns/mで、10%程度の幅があります。

正確な値が必要なときにはご注意ください。

図5は、図1の近似式をプロットしたものです。h>0.8Wの条件がありますが、この条件はあまり必要ではないようです。それよりも、グラウンドからの距離(高さ)hが小さくなると誤差が増えます。

論文発表当時は、h=100μmの基板は一般的に実用化されてなかったと考えます。

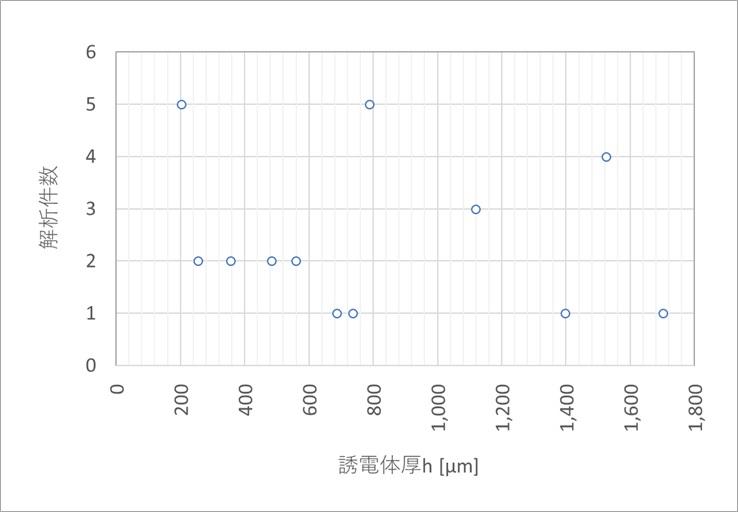

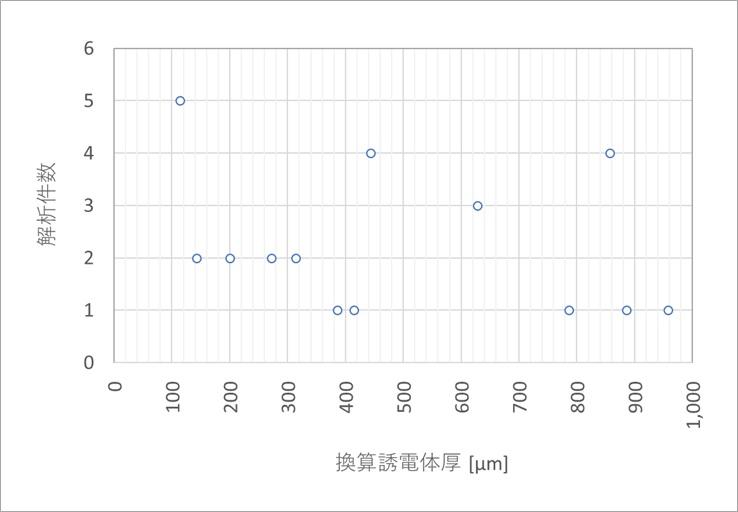

図6は、計算値を実測データと比較した際のサンプルの誘電体厚hの分布をプロットしたものです。このデータは、導体厚tが、約70μm(2.8mil)と現在使われている導体厚よりも厚いので、図7に、現在の主流の40μmに換算しました。サンプル数29に対して、誘電体厚が300μm以下のサンプル数は11しかないことに注目してください。これだけ当時と環境が変わっています。

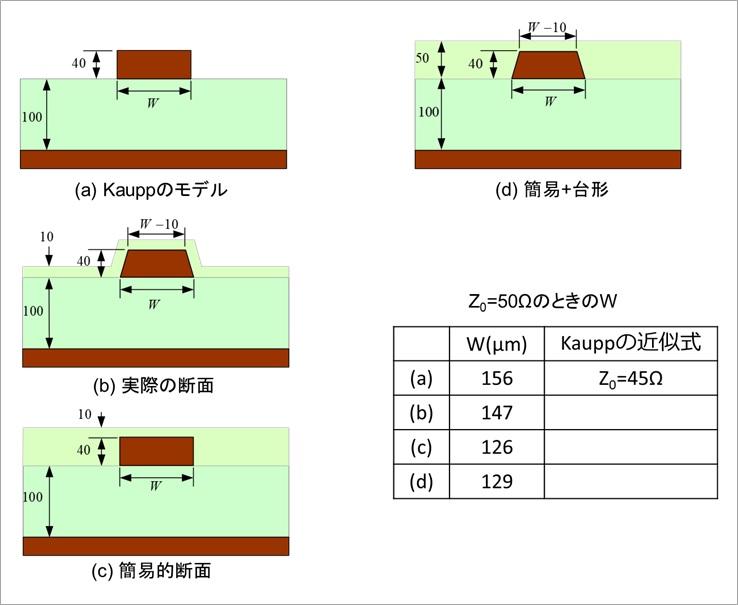

ここで、マイクロストリップ線路の断面図についてもう一度確認してみます。

Kauppの近似式は、図1の形状でした。

図8に、実際に計算に用いられるマイクロストリップ線路の断面形状を示します。

(a)は、Kauppの近似式の形状で、この近似式以外でもよく用いられるごく普通の形状です。

(b)は、ほぼ正確に表したもので、パターンは、上向きの台形で、ソルダレジストが、滑らかに被っています。ただ、解析するには多少面倒です。

(c)は、(a)と並んで近似計算でよく用いられます。解析データの入力の手間もあまりかかりません。

(d)は、(c)の改良型といったところで、パターンのエッチング効果を考慮したものです。

同図の表は、それぞれの形状に対して、特性インピーダンスZ0が50Ωのときに解析で求めた寸法を示しています。(b)の147μmに対して、いずれも10%から15%程度の誤差を含んでいます。

実際には、ボードメーカにおいて、設計値と実測データとを比較して修正するので、これらの誤差は大きな問題ではないと考えます。

以上、マイクロストリップ線路に関して考察しました。

次回は、ストリップ線路についても同様の考察を行い、必要な基板パラメータに対する断面寸法を求める筆者が作成したツールを紹介する予定です。

※このツールは、まだβ版なので公開していません。

【筆者からのメッセージ】

碓井有三のスペシャリストコラムとは?

基礎の基礎といったレベルから入って、いまさら聞けないようなテーマや初心者向けのテーマ、さらには少し高級なレベルまでを含め、できる限り分かりやすく噛み砕いて述べている連載コラムです。

もしかしたら、他にも気になるテーマがあるかも知れませんよ!