『ダンピング抵抗の値ってどのように決めるの?』では、ダンピング抵抗の値の決め方について述べました。それではダンピング抵抗はどこに入れればいいのでしょうか?もちろん、ドライバの出力の直近です。回路図に位置を指定しないと、ドライバとレシーバとの中間に置かれたり、極端な場合にはレシーバの手前に配置されたりしたケースを見たことがあります。

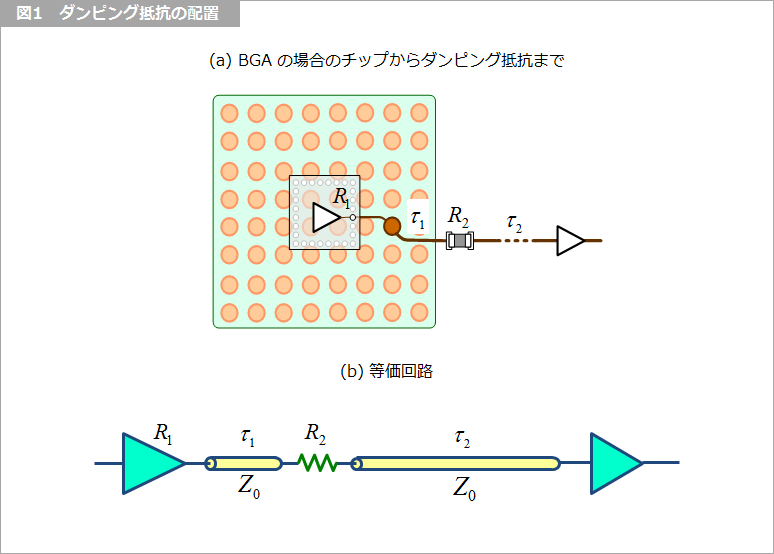

最近は BGA (Ball Grid Array) を使用することが多いので、チップの出力からダンピング抵抗まで、ある程度の配線長が存在することになります。図1 (a) のように、BGA のすぐ外にダンピング抵抗を配置したつもりでも、チップの出力からパッケージの外部ボールを経由して、チップ抵抗 R2 に到達するまでの配線長は数センチにもなることがあります。同図 (b) はその等価回路です。本来は、ドライバの出力抵抗 R1 とダンピング抵抗の直列抵抗 R1 + R2 と線路の特性インピーダンスZo とを、前回のコラムに述べたようにある程度一致させるつもりが、最初の τ1 のところで R1 と Zo とによる反射が発生してしまいます。(τ はギリシャ文字の小文字のタウ)

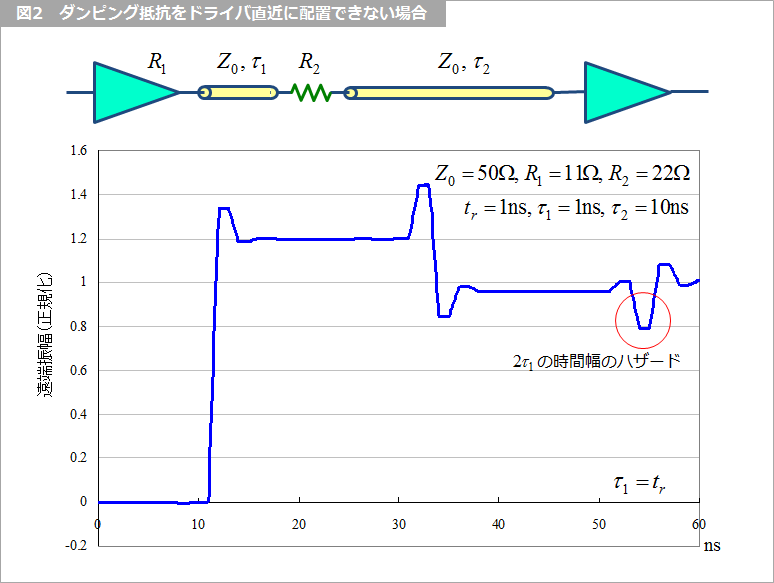

図2 はこの反射を誇張するために、τ1 を 1 ns(配線として約 15 cm)にしてどのような反射が発生するかを図示したものです。メインの反射による波形の変化時に、τ1 の 2 倍(2τ1)のパルス幅のノイズが発生します。図の例では、配線遅延の 2.5 往復、すなわち、5 × (τ1 + τ2) = 55 ns のタイミングのときのノイズが最大です。実際の配線はこれほど長くないので、もう少し早いタイミングで狭いノイズですが、感覚的なイメージとしてとらえて下さい。

この反射によるノイズは、τ1 を短くするしか低減できません。大事な信号は、できるだけ BGA の外周近くの信号を選んでください。

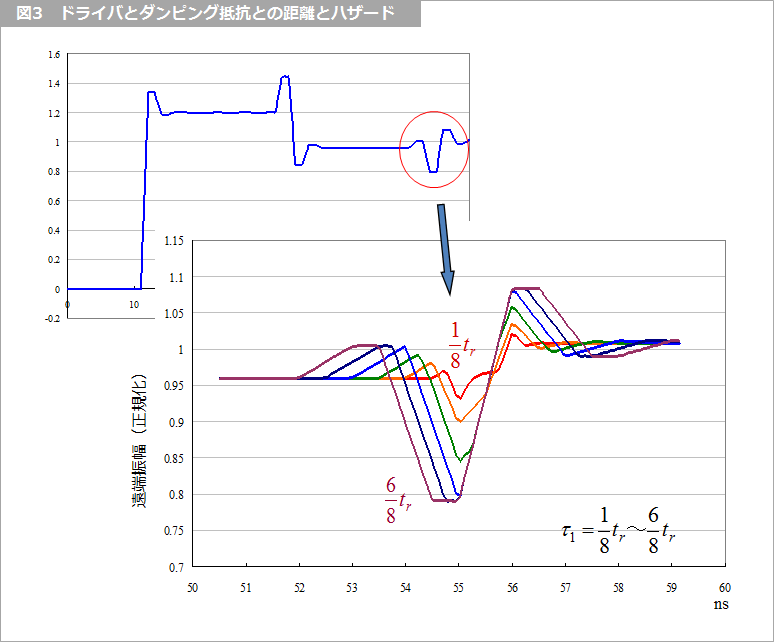

図3 に τ1 を信号の立ち上がり時間の 1/8 ずつ変化させたときの反射によるノイズを計算した結果を示します。反射ノイズの振幅は、τ1 に対して単調に増加し、信号の立ち上がり時間 tr の半分で飽和します。信号の立ち上がり時間が 500 ps ならば、その半分の 250 ps はほぼ 3 cm に相当します。図3 の例では、tr/4 のノイズの振幅は tr/2 のときの 1/3 程度です。短くすることが効果的であることが分かります。

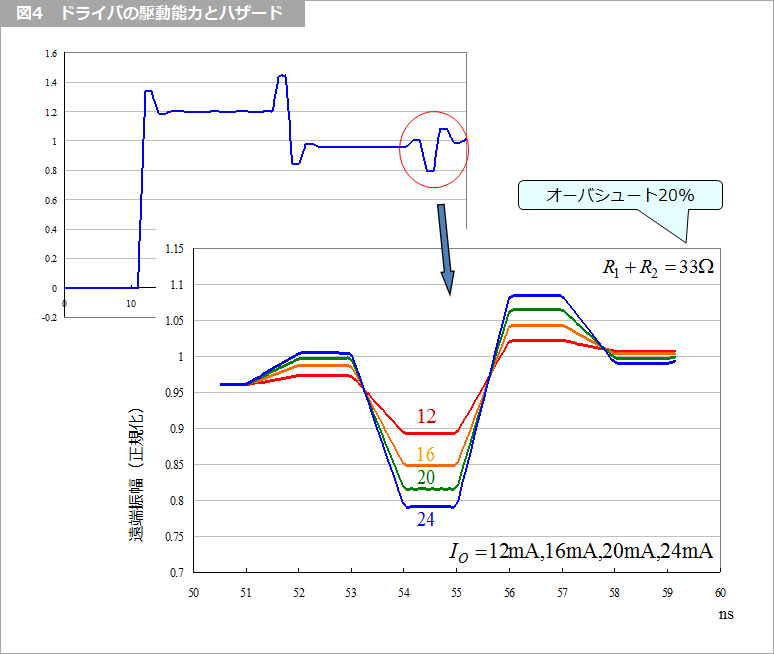

図4 は、R1 + R2 が同じ条件でも、τ1 によるノイズはドライバの元の駆動能力に依存することを示しています。24 mA ドライバは R1 = 11 Ω に相当します。出力抵抗 R1 とダンピング抵抗 R2 との直列抵抗(和)を図に示すように 33 Ω とすると、ダンピング抵抗 R2 は 22 Ω です。このときと、12 mA ドライバ(R1 = 22 Ω)に 11 Ω のダンピング抵抗を接続したものと伝送波形自体の反射の様子は同じです。ヒゲのノイズの振幅は、12 mA ドライバと 24 mA ドライバとでは倍以上の違いがあることがお分かりいただけると思います。大きな駆動能力のドライバは、ダンピング抵抗で補正しても、ダンピング抵抗までの配線長の影響を大きく受ける、ということです。

碓井有三のスペシャリストコラムとは?

基礎の基礎といったレベルから入って、いまさら聞けないようなテーマや初心者向けのテーマ、さらには少し高級なレベルまでを含め、できる限り分かりやすく噛み砕いて述べている連載コラムです。

もしかしたら、他にも気になるテーマがあるかも知れませんよ!