こんにちは。マクニカでAltera® FPGA 製品の技術サポートをしている 鷲宮タロー です。

『Altera® FPGA の PLL』で FPGA の PLL の概要を解説しましたが、ここでは PLL FPGA IP を使用するための手順について解説します。

PLL FPGA IP を使用できる FPGA ファミリーは、あらかじめ『Altera® FPGA の PLL』で確認してください。

内容

使用するツール

- Quartus® Prime Standard Edition 開発ソフトウェア

- ModelSim® - Altera® FPGA Edition

ターゲットの FPGA と開発ツールのエディションの関係については、Quartus® Prime のエディション比較 をご覧ください。

開発ソフトウェアのインストールが済んでいない方は、Altera® FPGA の Web サイトから入手できます。

詳細は、下記コンテンツをご覧ください。

Quartus® Prime 開発ソフトウェアおよび ModelSim® - Altera® FPGA Edition のダウンロード方法

Quartus® Prime 開発ソフトウェアおよび ModelSim® - Altera® FPGA Edition のインストール方法

1. PLL IP の生成

ここでは、Cyclone® V のプロジェクトを例に説明します。

ターゲットデバイスが Cyclone® V であるプロジェクトを開くか、新規にプロジェクトを作成します。

(Quartus® Prime のプロジェクト作成については、Quartus® はじめてガイド - プロジェクトの作成方法 を参照してください。)

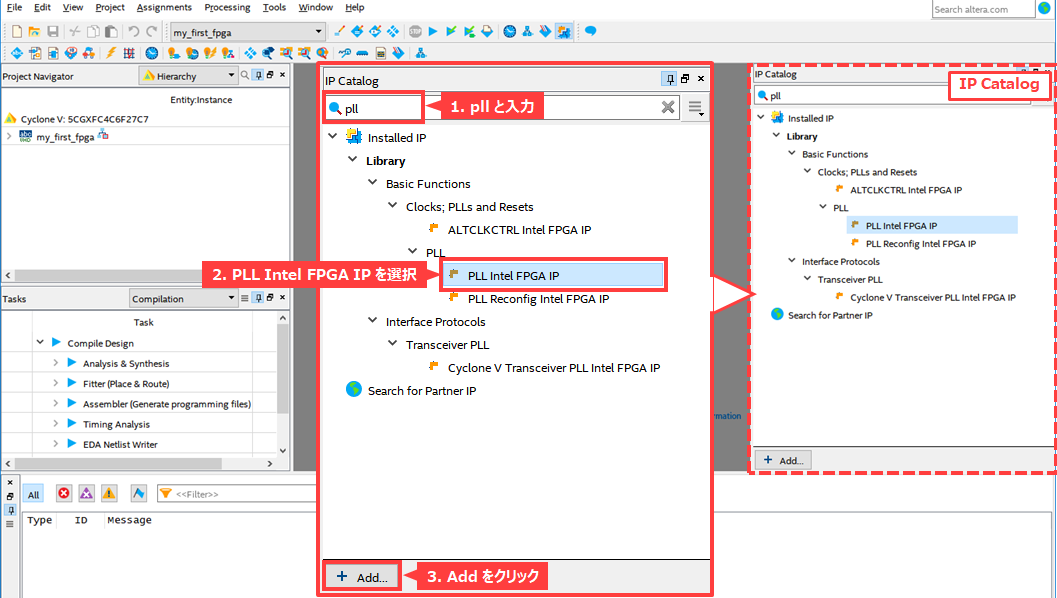

Quartus® Prime 内の IP Catalog の検索バーに pll をタイプ入力してください。

すると、PLL FPGA IP を容易に探し出すことができます。

PLL FPGA IP をハイライトした状態で、Add をクリックします。

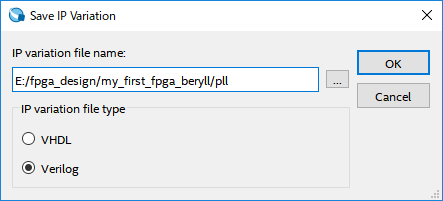

PLL FPGA IP を生成するフォルダーパス、PLL FPGA IP に付ける名前、生成する言語(VHDL or Verilog)を指定して、OK をクリックします。

生成先は、プロジェクトの作業フォルダーか、その下位フォルダーに生成することをお勧めします。

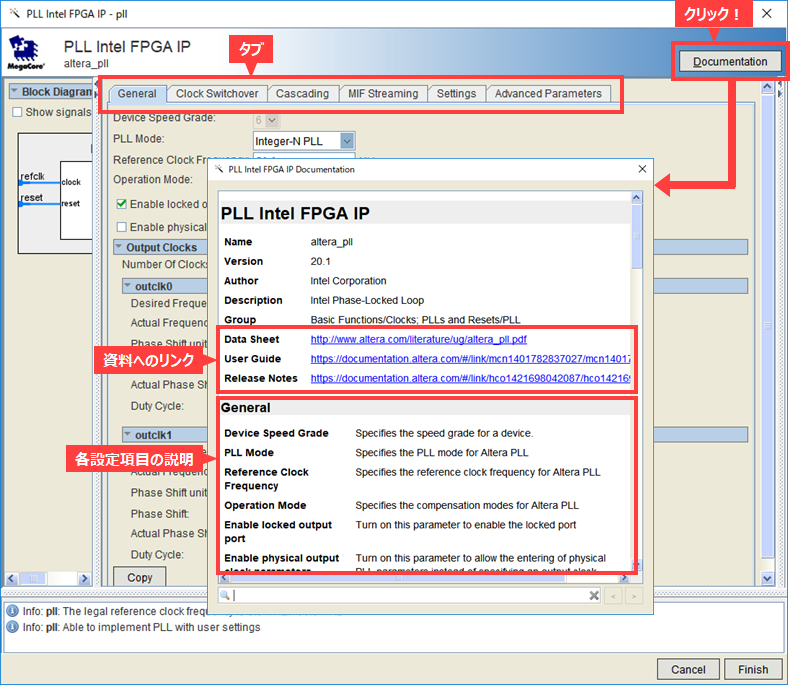

PLL FPGA IP 設定ウィンドウが起動します。

ここで、詳細なドキュメントや各設定項目の説明を見たい場合は、Documentation をクリックしてください。

各タブ内の主な設定項目について簡単に説明します。

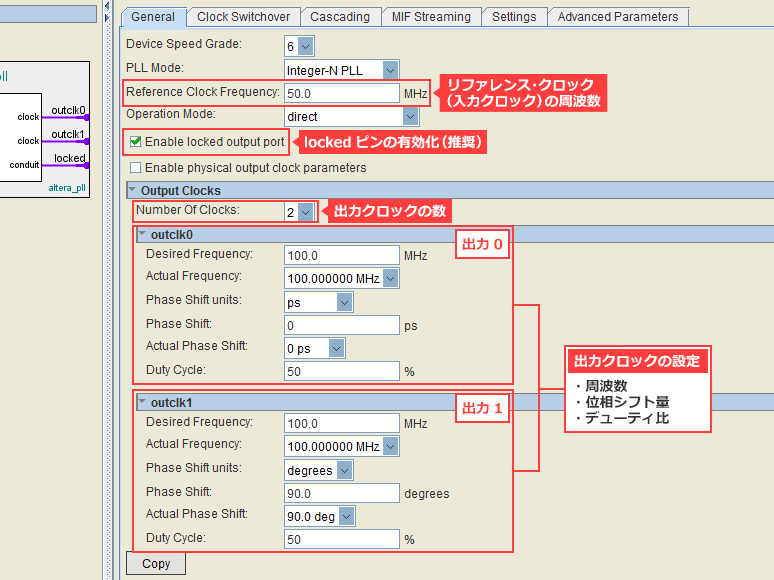

General タブ

リファレンスクロック(入力クロック)の周波数や locked ピンの有効/無効、出力クロックの数、出力クロックの設定などの一般的な設定を行います。

ここでは一例として、下表のとおり設定をすることにします。

|

項目 |

設定値 |

|

Reference Clock Frequency (入力クロックの周波数) |

50 (MHz) |

| Operation Mode | direct |

| Enable locked output port | On |

| Number Of Clocks | 2 |

| outclk0 (出力 0) | |

|

Desired Frequency (出力クロックの周波数) |

100 (MHz) |

|

Phase Shift (位相シフト値) |

0 (ps) |

| Duty Cycle | 50 (%) |

| outclk1 (出力 1) | |

|

Desired Frequency (出力クロックの周波数) |

100 (MHz) |

|

Phase Shift (位相シフト値) |

90 (degrees) |

| Duty Cycle | 50 (%) |

以下のタブについては、概要を説明します。各項目の詳細は、先ほど紹介した資料へのリンクからユーザーガイドをご覧ください。

Clock Switchover タブ

FPGA のシリーズによっては 2入力で切り替える機能をサポートしており、その設定を行います。

Cascading タブ

FPGA のシリーズによっては PLL のカスケード接続をサポートしており、その設定を行います。

MIF Streaming タブ

PLL の設定データが格納された MIF ファイルを使用したダイナミック・フェーズ・シフト(Dynamic Phase Shift)機能の設定を行います。

なお、Cyclone® V は、この機能をサポートしていません。

Settings タブ

PLL の自動リセットや PLL バンド幅プリセット、ダイナミック・リコンフィギュレーション(Dynamic Reconfiguration)、ダイナミック・フェーズ・シフト、ダイナミック・フェーズ・アライメント(DPA)の設定を行います。

Advanced Parameters タブ

PLL の M/N/C カウンタの値や VCO 周波数など、PLL のパラメーター名とパラメーター値を確認できます。

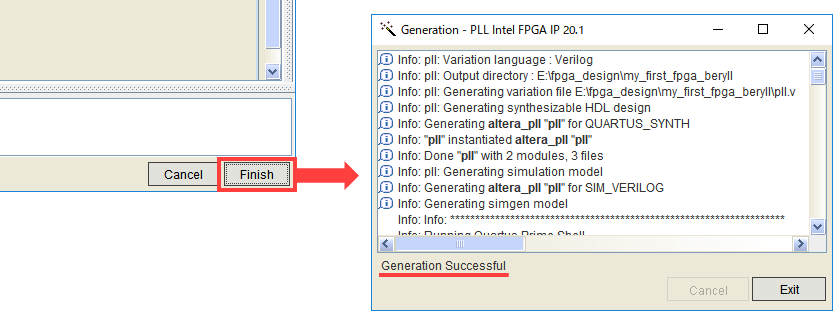

各種設定を終えたら Finish をクリックし、IP を生成します。

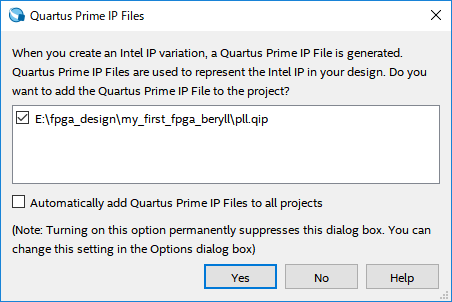

"Generation Successful" を確認後、Exit をクリックすると、下図のウィンドウが表示されます。

生成した IP デザインを、現在開いているプロジェクトへ追加登録する場合は、Yes をクリックしてください。(No をクリックした場合は、手動で追加設定してください。)

これで、PLL FPGA IP の生成が完了しました。

みなさんが設計中のユーザー回路と接続して、論理設計を進めましょう。

もし、PLL FPGA IP の設定を変更する場合は、こちらの FAQ をご覧ください。

【FAQ】 IP 編集画面の起動方法

必要なパラメーターを編集したら、再度 PLL FPGA IP を生成してください。

2. ユーザー回路との接続

PLL FPGA IP が生成されたら、ユーザーロジックと接続します。

Verilog-HDL や VHDL に慣れていない方は、こちらを参考にしてください。このページ内の下位モジュール(ブロック)の呼び出しをご覧ください。

はじめてみよう!Verilog-HDL <演習問題つき>

はじめてみよう!VHDL <演習問題つき>

スケマティック (回路図) で設計している方は、IP 生成時に回路図エディター用のシンボルも生成されているので、回路図エディター上でユーザーが作成した IP シンボルを呼び出して接続してください。

ただし、スケマティックは 3rd パーティーツールのシミュレーターで RTL シミュレーションができません。やはり、HDL で設計することをお勧めします。

<裏ワザ>

HDL 記述に慣れていない方は、Quartus® Prime の回路図エディターで回路図から HLD へ変換する機能を使ってみてください。

変換する方法は、下記ページにあるドキュメントを参考にしてください。

Quartus® はじめてガイド - 回路図エディタの使い方

上位階層のデザイン・ファイルの作成が終わったら、

Quartus® Prime のメニューから Processing > Start > Start Analysis & Synthesis を選択し論理合成してみましょう。

正常に完了しましたか?

回路図から変換した場合、プロジェクト内に回路図ファイル(BDF ファイル)と変換後の HDL ファイル(Verilog-HDL なら V ファイル、VHDL なら VHD ファイル)の両方が登録されていると正常に論理合成ができません。(Project メニュー > Add/Remove Files in Project から、使用しないデザインファイルを削除してください。)

3. シミュレーションで確認

それでは、RTL シミュレーションで確認してみましょう。

今回は ModelSim® - Altera® FPGA Edition を使用します。

シミュレーションで確認するにはテストベンチが必要ですが、テストベンチはユーザーが作成します。

テストベンチの記述方法については、こちらをご覧ください。

はじめてみよう!テストベンチ

テストベンチができたら、シミュレーションする準備ができたということになります。

ModelSim® を手動で操作し シミュレーション実行することもできますが、ここでは便利な方法を紹介します。参考にしてください。

NativeLink 機能を使用したシミュレーション

FPGA のファンクション・シミュレーションは NativeLink で解決しよう

ModelSim® 向けシミュレーション用スクリプトファイルを生成・実行してみよう

msel_setup.tcl を使用したシミュレーション

以上、鷲宮タローが PLL FPGA IP の作成からシミュレーションまでの手順をご紹介しました。

おすすめ記事/資料はこちら

PLL の分周 / 逓倍(ていばい)

PLL の応用(スペクトラム拡散で EMI を減らそう!)

PLL のループ帯域幅とスペクトラム拡散のビミョーな関係

Altera® FPGA の PLL

IP 関連の記事や資料 一覧

Altera® FPGA の開発フロー / トップページ