こんにちは。

マクニカでインテル® FPGA 製品の技術サポートをしている インテル・F・ハナコ です。

Quartus® Prime Standard Edition または Lite Edition を使用した場合、FPGA のファンクション・シミュレーションは NativeLink による実行が簡単でおすすめだと以前ご案内しました。

その場合、イタレーションの操作が毎回 Quartus Prime のメニューから実行することになり、少々面倒に感じるユーザーさんもいるはずです。

そんなときは、

NativeLink シミュレーション用のスクリプトだけを使用して、ModelSim(※) から実行してみてはいかがでしょうか。

※ ModelSim – Intel FPGA Edition、ModelSim – Intel FPGA Starter Edition を含む

今回は、シミュレーション用のスクリプトファイル生成方法と、ModelSim での使用方法をご紹介します。

ハナコのおすすめポイント♪

この方法は、デザインに使用している全てのユーザーデザインファイルと、IP のシミュレーション用ライブラリを取りまとめたスクリプトが自動で生成できます。

NativeLink のように ModelSim が自動的に起動し実行されることはなく、スクリプトファイルだけが生成されます。

各 IP 用に個別で生成されたシミュレーション用スクリプトをユーザーが手動で切り貼りする必要がないため、

シミュレーション・ツールが読み込むべきソースおよびライブラリの欠落を防止できますよ。

対象環境

| Quartus Prime |

Quartus Prime Standard Edition Quartus Prime Lite Edition (※ Quartus Prime Pro Editionはこちらのコンテンツをご覧ください。) |

| シミュレーション・ツール(注1) |

ModelSim PE / ModelSim SE / Questa ModelSim - Intel FPGA Edition (Starter Edition を含む) |

注1: 各ツールの対応バージョンは、ご利用になるバージョンの Quartus Prime のリリースノートをご確認ください。

注2: スケマティックのデザイン (.bdf) は、すべて HDL に変換する必要があります。

<参考 FAQ> Q: 回路図を含んだデザインを ModelSim でシミュレーションしたいのですが、うまくいきません。

事前準備

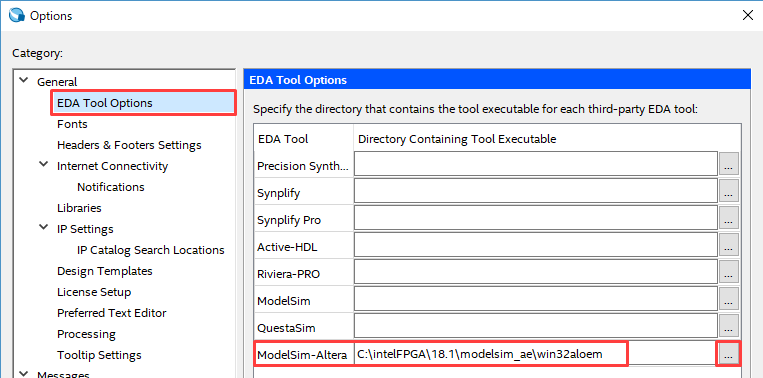

1) EDA ツールの環境設定

① Quartus Prime の Tools メニュー ➤ Options ➤ General 下にある EDA Tool Options をクリックします。

② 使用するシミュレーション・ツール名の行、右横のブラウザボタンをクリックし、シミュレーション・ツールの実行プログラムが保存されている

フォルダーの絶対パスを指定します。

例えば、ModelSim - Intel FPGA Edition (for Windows) の場合は、modelsim.exe が保存されている win32aloem フォルダーを指定します。

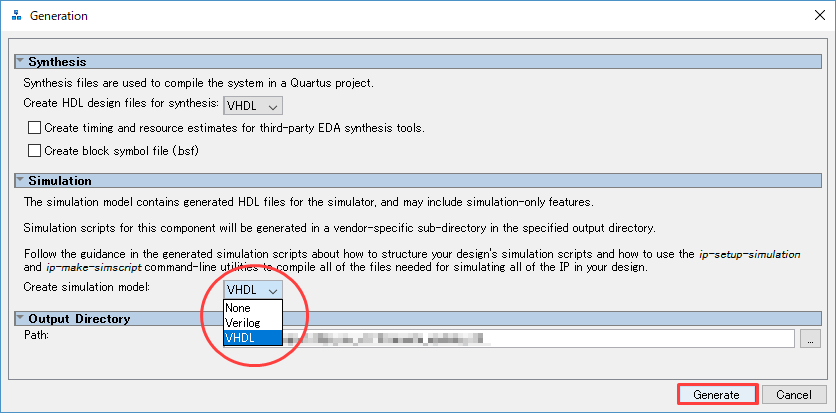

2) IP のシミュレーション・モデルをの生成

デザイン内に Platform Designer で作成したモジュール、あるいは IP Catalog で呼び出した IP が "Platform Designer ベースで起動されるもの" の場合には、Generate 時に "シミュレーション・モデル生成オプション" があるので、言語を選択してから Generate を実行してください。(選択していないと、シミュレーションをするための関連ファイルは生成されず、シミュレーションが実行できません。)

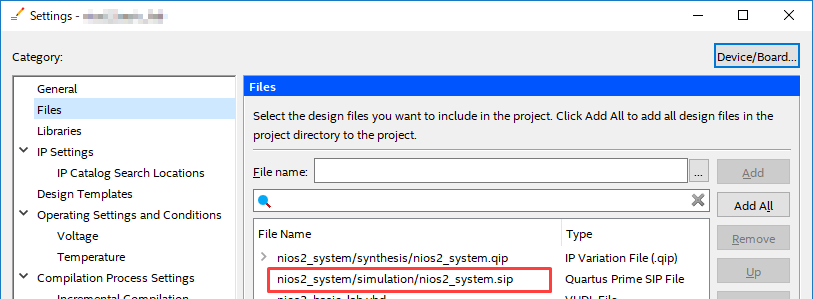

3) プロジェクトにデザイン・ファイルをすべて登録

Quartus Prime のコンパイルに必要なデザイン(ユーザー・デザイン、IP デザイン)を、下記メニューにより、すべてプロジェクトへ登録してください。

Project メニュー ➤ Add/Remove Files in Project

その他、IP や Platform Designer で作成したモジュールがデザインに含まれている場合は、生成フォルダー内にある <ip_name>.qip と同様に、<ip_name>.sip ファイルを、必ず登録してください。

<関連 FAQ> .sip ファイルとはどのようなファイルですか?

.sip ファイルの生成場所は、IP Catalog / Platform Designer のどちらでモジュールを作成したかで異なります。

なお、IP Catalog で作成する IP によっては、シミュレーション・モデルや .sip を専用に生成しないものもあります(例えば、ALTLVDS_RX/TX、ALTPLL、RAM: 2-PORTなど)。その場合には、論理合成用のデザイン・ファイルだけをプロジェクトに登録してください。

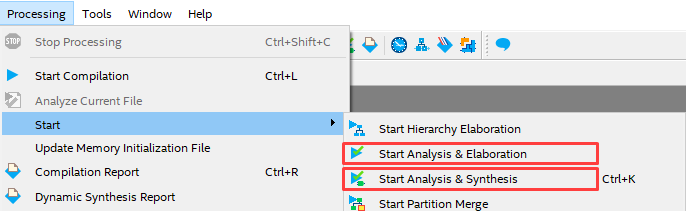

4) Analysis & Elaboration を実行

スクリプトファイルを生成するには (NativeLink 実行の一つの工程であるため)、Analysis & Elaboration あるいは Analysis & Synthesis を実行しなければなりません。

これにより、Quartus Prime のプロジェクトで必要な IP モジュールを含むデザイン・ファイル一式のラインナップと所在 (保存パス) が、情報として吸い上げられ、後のスクリプトファイルに反映されます。

Processing メニュー ➤ Start ➤ Start Analysis & Elaboration (あるいは Start Analysis & Synthesis)

5) EDA ツール設定とテストベンチの登録

EDA Tools Settings と NativeLink Settings を設定します。

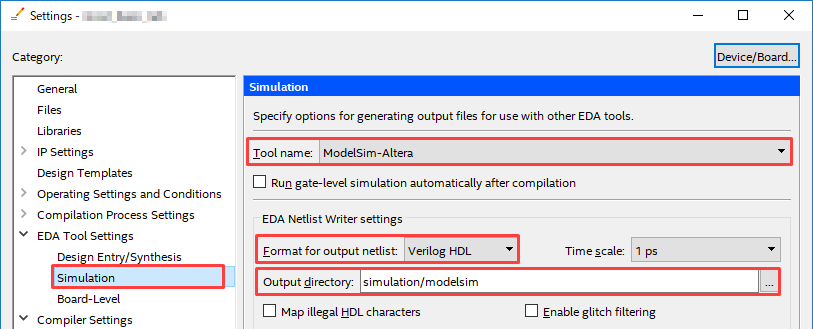

① Assignments ➤ Settings ➤ EDA Tool Settings ➤ Simulationを選択し、Tool name においてシミュレーションに使用するツール名を選択します。

※ ModelSim - Intel FPGA Edition は、ModelSim-Altera を選択してください。

② EDA Netlist Writer settings 枠内において、以下を設定します。

・ Format for output netlist : Verilog HDL (ハナコ's ポイント♪ を参照)

・ Output directory : simulation/modelsim (デフォルトのまま)

ハナコ’s ポイント♪

IP 作成時のシミュレーション・モデルやテストベンチが VHDL であっても、ここのオプションは Verilog HDL の選択をオススメします。

この選択言語は、NativeLink 実行用スクリプトの vsim -L コマンドに影響します。

近年の IP は シミュレーション・モデルの言語選択を VHDL で指定しても、下位モデルは SystemVeriog で構成されていることが多く、

必然的に Verilog 用のシミュレーション・ライブラリが必要になります。その場合、vsim -L コマンドで Verilog 用のライブラリを漏れなく

指定する必要があるため、VHDL でモデルを生成してもFormat for output netlist は Verilog HDL をご利用ください。

なお、VHDL 用のシミュレーション・ライブラリは、IP 作成時に生成されたソースに直接宣言が記述されているため、vsim -L コマンドで

指定しなくても対応されます。

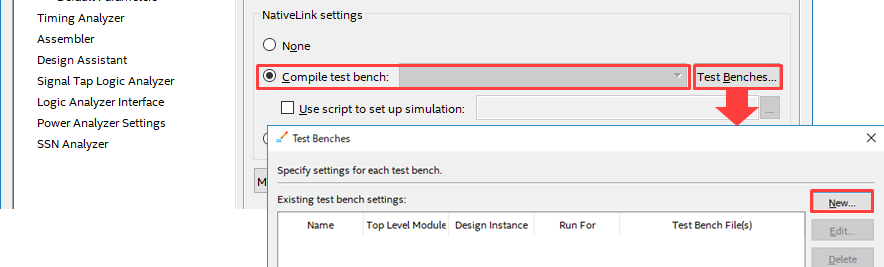

③ NativeLink settings 枠内にて、テストベンチを登録します。

Compile test bench を選択し、Test Benches ボタンをクリックします。その後、Test Benches ウィンドウの New ボタンをクリックします。

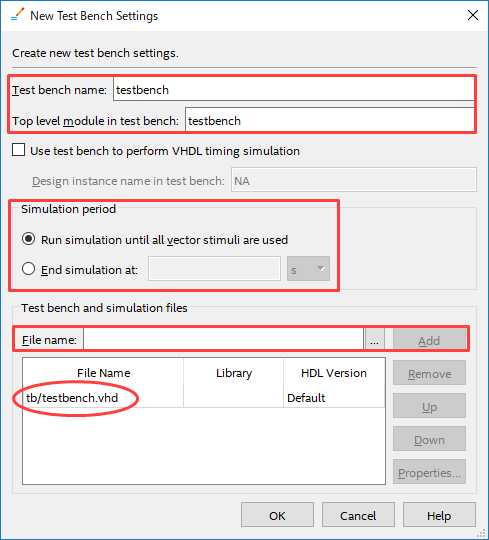

New Test Benches Settings ダイアログボックスにおいて、下記項目を設定します。

・ Test bench name : テストベンチのモジュール名を入力 (下段の Top Level module in test bench 欄も同時入力)

・ Simulation period : シミュレーション実行の終了時間を設定

・ File name : ブラウズボタをクリックし、テストベンチ・ファイルを選択。Add ボタンで登録。

各ウィンドウを OK で閉じ、Settings ウィンドウへ戻ります。

(※ Setting 画面は閉じずに、次の操作へ移行してください。)

スクリプトファイルを生成

ModelSim 向けのシミュレーション用スクリプトファイルを、Quartus Prime に生成させます。

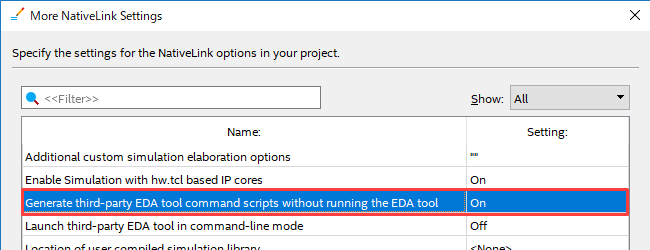

① More NativeLink Settings ボタンをクリックし、ツール起動無し(スクリプト生成のみ)の NativeLink を実行させるオプションを有効にします。

Generate third-party EDA tool command scripts without running the EDA tool = On

② スクリプトファイルを生成します。

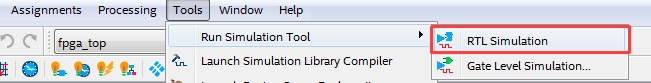

Tools メニュー ➤ Run Simulation Tool ➤ RTL Simulation をクリックします。

実行後、Messages ウィンドウの System タブに、以下の Information メッセージが表示されます。

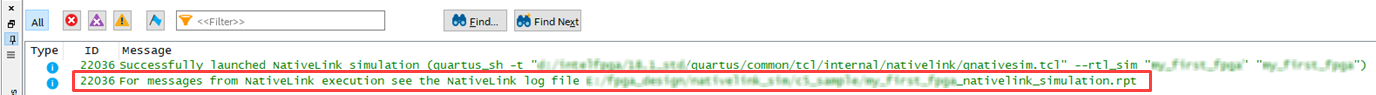

ID: 22036

For messages from NativeLink execution see the NativeLink log file <作業フォルダーのパス>/<プロジェクト名>_nativelink_simulation.rpt

メッセージに示された <プロジェクト名>_nativelink_simulation.rpt ファイルをテキスト・エディタで開き、ログの末尾に

以下のメッセージが確認できたら成功です!

Info: NativeLink simulation flow was successful

EDA Tool Settings ➤ Simulation において指定した内容に応じて、下記いずれかの do ファイルが生成されています。

| Format for output netlist で指定した言語 | Output directory に生成されたスクリプトファイル |

| Verilog HDL | <project_name>_run_ msim_rtl_verilog.do |

| VHDL | <project_name>_run_ msim_rtl_vhdl.do |

[Note]

ファイル名に言語名が含まれていますが、スクリプトの内容には関係ありません。

FPGA デザイン・ファイル、およびテストベンチ・ファイルの言語フォーマットに応じて、ModelSim - IFE のコマンドが自動的に適用されます。

例えば、VHDL と Verilog のデザインが混在したプロジェクトの場合、VHDL ソースのコンパイルは vcom コマンドで実行し、

Verilog ソースのコンパイルは vlog コマンドで実行するようにスクリプトが自動で構成されます。(頭いい~♪)

これで、スクリプトファイルは完成です!!

スクリプトファイルを ModelSim で実行

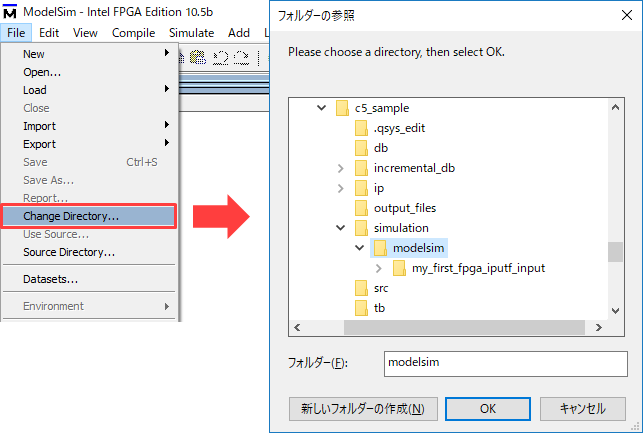

① ModelSim を起動し、File メニュー ➤ Change Directory (あるいは cd コマンド)により、

スクリプトファイルが生成されたフォルダーへ移動します。

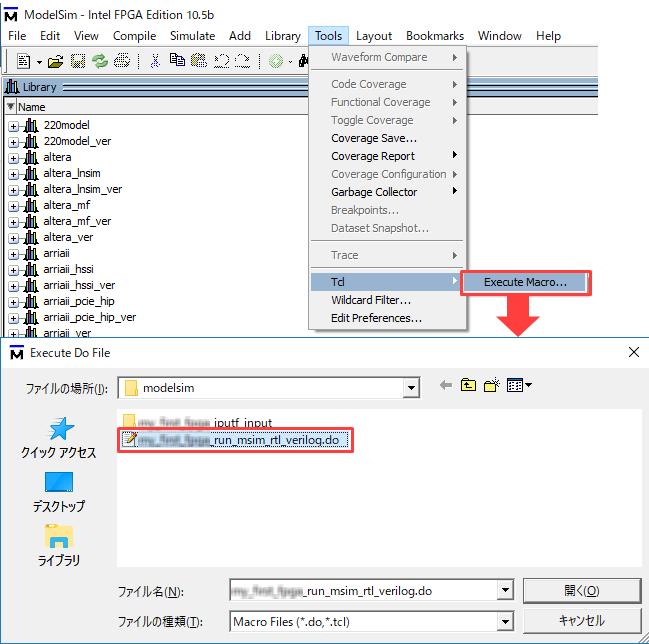

② Tools メニュー ➤ Tcl > Execute Macro… より、スクリプトファイルを選択して実行します。

Transcript ウィンドウを使ってコマンド実行する場合は “do コマンド” です。

例 do <project_name>_run_ msim_rtl_verilog.do

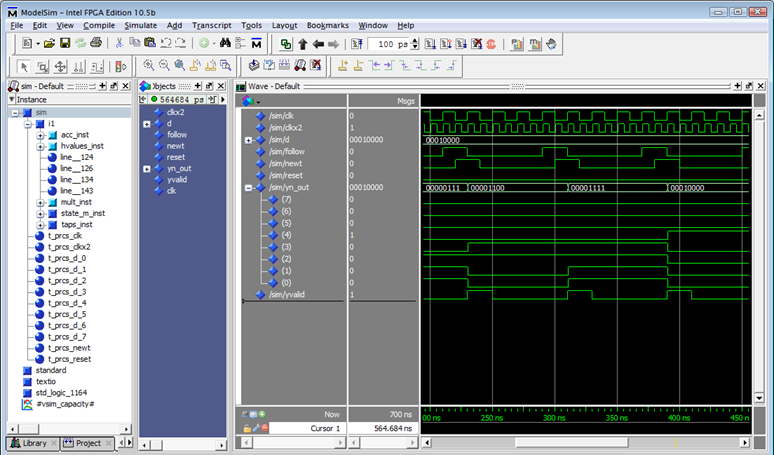

③ 自動的にシミュレーションが実行されます。

スクリプトに記載されたコマンドにより、

・ソースやライブラリ、シミュレーション・モデルのコンパイル実行(vcom/vlog コマンド)

・ロード実行(vsim コマンド)

・観測する信号を Wave ウィンドウに追加(add コマンド)

・シミュレーション実行(run コマンド)

などが実行されます。

④ Wave ウィンドウに表示された波形を検証してください。

スクリプトファイルの説明

Quartus Prime が RTL Simulation (Tools メニュー ➤ Run Simulation Tool) により生成した

<project_name>_run_ msim_rtl_verilog.do / <project_name>_run_ msim_rtl_vhdl.do ファイルで使用しているコマンドを一部紹介します。

|

コマンド |

概要および例 |

| vlib |

ライブラリを作成する 例: vlib rtl_work |

| vmap |

論理ライブラリ名とファイルシステム上のライブラリのパスをマッピングする 例: vmap work rtl_work |

| vlog |

Verilog および SystemVerilog ファイルをライブラリにコンパイルする 例: vlog -work work ./sample.v |

| vcom |

VHDL ファイルをライブラリにコンパイルする 例: vcom -work work ./sample.vhd |

| vsim |

デザインをロードする 例: vsim work.sample_tb |

| add wave |

選択した信号を Wave ウィンドウへ追加する 例: add wave * |

| view |

指定のウィンドウを表示する 例: view structure |

| run |

シミュレーションを実行する 例: run 500ms |

生成されたスクリプトファイルのコマンドを追加あるいは編集して使用することも可能です。

コメントアウトは、行の先頭に # をつけてください。

コマンド、およびコマンドのオプションの詳細は、ModelSim、Questa の 「Command Reference Manual」 を参照してください。

おすすめ記事/資料はこちら

FPGA のファンクション・シミュレーションは NativeLink で解決しよう

Quartus® Prime Pro Edition で生成した IP を含むデザインを ModelSim でファンクション・シミュレーションする方法