こんにちは。

マクニカで Altera® FPGA 製品の技術サポートをしている アルテラ ハナコ です。

Altera® FPGA 向けの IP を含むデザインを EDA シミュレーターを用いて RTL レベルのファンクション・シミュレーションする場合は、Quartus® Prime の NativeLink シミュレーション によるフローをお勧めしていますが、Quartus Prime Pro Edition では NativeLink シミュレーションがサポートされていません。

| 表1. Quartus Prime における NativeLink シミュレーションのサポート状況 | |

| Quartus Prime Pro Edition |

× |

| Quartus Prime Standard Edition |

〇 |

| Quartus Prime Lite Edition |

〇 |

デザインに IP が含まれている場合、Altera® FPGA 用のシミュレーション・モデル (ライブラリー) の他に IP 用のシミュレーション・モデル (ライブラリー) のセットアップが必要なため、容易には実行できません。

そこで!ここでは

Quartus Prime Pro Edition ユーザー向けに、IP を含むデザインを RTL レベルのファンクション・シミュレーションを実行する方法をご紹介します。

今回は、Questa* - Altera® FPGA Edition (以下、Questa - IFE という。Starter Edition を含む) および Questa、ModelSim をシミュレーション・ツールに用いてご紹介します。

その他の EDA シミュレーターについては、下記ドキュメントをご覧ください。

Quartus Prime Pro Edition User Guide: Third-party Simulation

|

こちらのフローもご活用ください。詳細は、下記コンテンツをご覧ください。 Quartus® Prime Pro Edition の Run Simulation 機能で簡単に RTL シミュレーションする方法 |

対象のソフトウェア環境

| 対応する Quartus Prime のエディション | Quartus Prime Pro Edition |

|

このコンテンツで取り扱う シミュレーション・ツール(注1) |

Questa - Altera® FPGA Edition (Starter Edition を含む) (※2) または Questa、ModelSim |

※1: 各 EDA ツールの対応バージョンは、ご利用になる Quartus Prime バージョンのリリースノートをご確認ください。

※2: Pro Edition 対応のものをご利用ください。

IP のシミュレーション・モデルを生成

IP を RTL レベル・シミュレーションするためには、IP 用のシミュレーション・モデルを生成しておく必要があります。

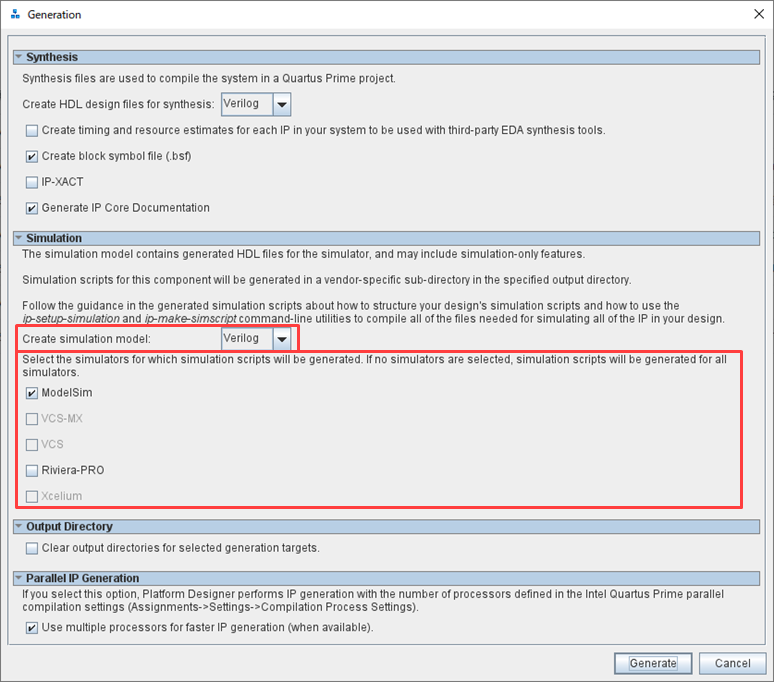

IP Catalog または Platform Designer で IP を作成する際に、Generate HDL 実行時にポップアップされる Generation ダイアログボックスにおいて、”Create simulation model オプション“ で言語を指定し、シミュレーション実行用スクリプトを生成させるために対応ツールを選択します。

その後 Generate (または Generate HDL) ボタンをクリックすると、その IP 用にシミュレーション・ツール向けのファンクション・モデルとスクリプトファイルが生成されます。

作業フロー

以下は、Quartus Prime Pro Edition で生成した IPを含むデザインを

Questa – IFE (または Questa、ModelSim) で RTL レベル・シミュレーションする作業の流れです。

なお、Quartus Prime プロジェクトは作成済みであり、デザインも完成していることが前提です。

1. デザインを Quartus Prime プロジェクトに登録

2. IP 用シミュレーション・スクリプトを生成

3. ユーザーデザインを含めたシミュレーション・スクリプトを作成

4. シミュレーション実行

1. デザインを Quartus Prime プロジェクトに登録

Quartus Prime プロジェクトに、Quartus Prime がコンパイル時に必要なデザインファイルを登録します。

IP デザインは、*.ip ファイルを登録します。

Project メニュー > Add/Remove Files in Project

2. IP 用シミュレーション・スクリプトを生成

以下のメニューから、Quartus Prime のプロジェクトに登録されたすべての IP 向けのシミュレーション用スクリプトを生成します。

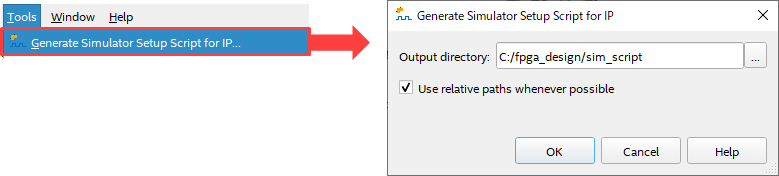

Tool メニュー > Generate Simulator Setup Script for IP

現在開いている Quartus Prime プロジェクト・フォルダーのパスがデフォルトで表示されます。

ファイル管理のために、スクリプトファイルは別フォルダーを用意し そこへ生成させることをおススメします。

(上図は、Quartus Prime プロジェクト C:/fpga_design 内に sim_script フォルダーを作成し生成するよう指定しています。)

3. ユーザーデザインを含めたシミュレーション・スクリプトを作成

① ステップ2で生成したフォルダー内の mentor フォルダーにある msim_setup.tcl をテキストエディタ―で開きます。

# # TOP-LEVEL TEMPLATE - BEGIN

から

# # TOP-LEVEL TEMPLATE – END

までの行をすべてコピーし、新規テキストファイルにペーストします。

その後 ファイル名を mentor.do (ファイル名は任意) として、msim_setup.tcl と同じフォルダーに保存します。

② 各行の最初の2文字(#とスペース)を削除します。

③ スクリプトの内容を、フォルダー環境に合わせて編集します。

コマンドを上から解説します。

set QSYS_SIMDIR <script generation output directory>

Quartus Prime が生成した IP シミュレーション用スクリプトのフォルダー・パス(絶対パスまたは相対パス)を指定します。

つまり Generate Simulator Setup Script for IP で指定したパスです。

今回の例では sim_script フォルダーが該当します。

例) set QSYS_SIMDIR ./

ハナコ’s ポイント♪①

相対パスで設定する場合、基準フォルダーは Questa - IFE の作業フォルダーであり、デフォルトでは Generate Simulator Setup Script for IP で指定したフォルダーが Questa - IFE の作業フォルダーになることが想定されています。もし Questa - IFE の作業フォルダーを別フォルダーにする場合は、QSYS_SIMDIR は Questa - IFE の作業フォルダーを基準に考え Generate Simulator Setup Script for IP で指定したパスに設定します。相対パスで指定する際は、この点に注意してください。

source $QSYS_SIMDIR/mentor/msim_setup.tcl

IP のシミュレーション用スクリプトを読み込ませます。

編集の必要はありません。

set USER_DEFINED_COMPILE_OPTIONS <compilation options>

set USER_DEFINED_VHDL_COMPILE_OPTIONS <compilation options for VHDL>

set USER_DEFINED_VERILOG_COMPILE_OPTIONS <compilation options for Verilog>

必要に応じてコンパイル・オプションを設定します。

今回は使用しないため、行の先頭に # を入力し、コメントアウトします。

dev_com

Altera® FPGA 用のスタンダードなシミュレーション・モデルをコンパイルします。

編集の必要はありません。

このコマンドは Altera Edition ではない Questa や ModelSim で実行されます。

Questa - IFE ユーザーは不要な実行コマンドですが、Quetsa - IFE であることが自動判別され 実行されませんので

コメントアウトの必要はありません。

com

IP のシミュレーション・モデルをコンパイルします。

編集の必要はありません。

vlog <compilation options> <design and testbench files>

コマンドを追加して、IP デザイン以外のすべてのユーザー・デザインファイルとテストベンチ・ファイルをコンパイルします。

vlog コマンドは Verilog HDL ソースのコンパイル・コマンドです。

VHDL ユーザーは vcom に編集します。

例) vcom <compilation options> <design and testbench files>

<compilation options> : 必要に応じてコンパイル時にオプションが設定できます。

例えば、以下のように

言語のバージョンや、コンパイル結果を格納するフォルダーおよびライブラリ名を指定できます。

vcom -2008 -work work ../simple_counter.vhd

vlog -vlog01compat -work work ../simple_counter.v

オプションの詳細は、各シミュレーターツールの Command Reference Manual の Commands のチャプターにおいて

vlog または vcom をご覧ください。

<design and testbench files>: コンパイルするファイルのパス(絶対パスまたは相対パス)を指定します。

ハナコのつぶやき ①

Command Reference Manual は、Questa - IFE のインストールフォルダーに保存されています。

例) \\<tool_install_dir>\docs\pdfdocs\questa_sim_ref.pdf

set TOP_LEVEL_NAME <simulation top>

最上位のテストベンチ・モジュール/エンティティ名を設定します。

このコマンドは、最上位をエラボレートするために elab / elab_debug コマンドで使用されます。

例) set TOP_LEVEL_NAME top_sim

set USER_DEFINED_ELAB_OPTIONS <elaboration options>

必要に応じてエラボレーション・オプションを設定します。

今回は使用しないため、行の先頭に # を入力し、コメントアウトします。

elab_debug

vsim コマンドが -voptargs=+acc (最適化されたデザインのオブジェクトへの可視性を有効にするオプション) を適用した形で実行されます。

もし最適化をさせない場合は、下記コマンドを使用してください。

elab

VHDL ユーザーは、elab_debug または elab コマンドの後に -t オプションを追加することにより Resolution を指定することができます。

例) elab_debug -t 1ps

Resolution 何も指定しない場合は ns で処理されます。

Verilog HDL ユーザーは、テストベンチに記載した Resolution に依存します。

ハナコ’s ポイント♪②

シミュレーション結果を波形として表示させるため、run コマンドの前に add wave コマンドを追記します。

テストベンチ上のすべてのポートを登録する場合は、* (アスタリスク)で OK!

例) add wave *

run -a

シミュレーションを実行します。

-a は -all と同等です。テストベンチで指定した時間を実行します。

もし時間指定をする場合は、run コマンドの後に スペースと時間および単位 を指定します。

例) run 500ms

exit -code 0

今回は GUI で操作しているため必要ありません。行の先頭に # を入力し、コメントアウトします。

編集後、do ファイルを保存します。

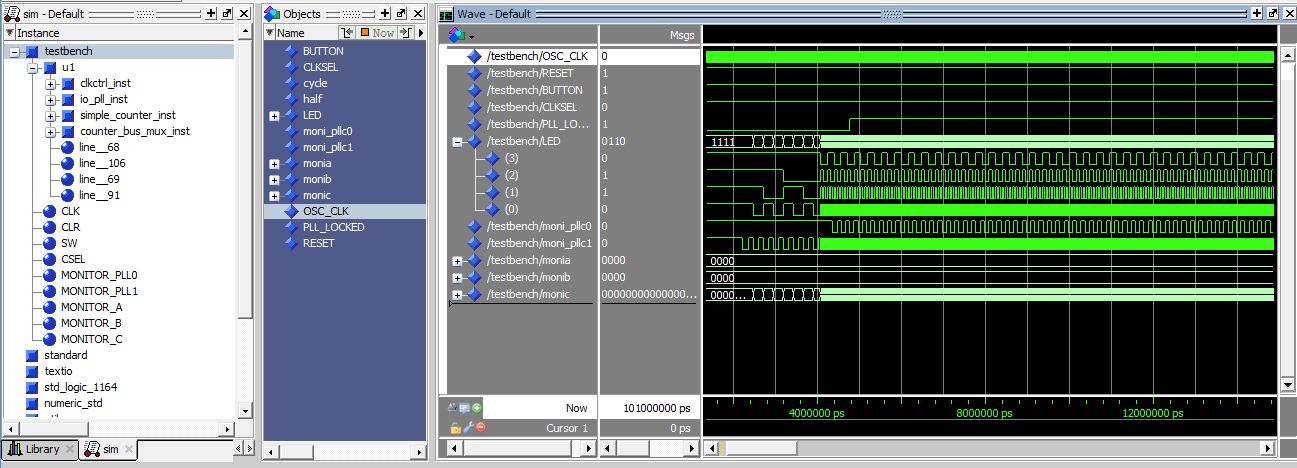

4. シミュレーションを実行

① Questa - IFE を起動します。

② File メニュー > Change Directory により、シミュレーション用の作業フォルダーを指定します。

このコンテンツでは C:/fpga_design/sim_script です。

③ Tools メニュー > Tcl > Execute Macro を選択し、ステップ3 で作成した do ファイルをダブルクリックで選択します。

④ スクリプトの内容が実行され、Wave ウィンドウにシミュレーション結果が波形として表示されます。

ハナコのつぶやき ②

シミュレーション実行後にデザイン(テストベンチや IPを含む)が変更されたら、ソースコードを再コンパイルし、シミュレーションを再実行する必要があります。その際はステップ 3 で作成した do ファイル内の再実行不要なコマンドの先頭に # を入力しコメントアウトして、再利用してください。(例えば、dev_com など)

これにより、重複作業がなくなり、わずかですが作業工数を軽減することができますよ。

以上を参考に、Pro Edition でも簡単にファンクション・シミュレーションをしちゃいましょう!