こんにちは。めんどくさがり屋の頭領です。

業務を短縮できないか裏ワザに対するアンテナをはっています。

Quartus® II を使って回路をデザインした後は、 ModelSim® などの HDL シミュレータで RTL シミュレーションをするのが常套手段。

(正しい設計の手順はコチラ)

しかし、シミュレーションを実行するには test bench file というものが必要になる。

テストベンチって何だ??

テストベンチはひとことで言うと、

「Verilog HDL もしくは VHDL を使って対象の回路に入力信号を与え、出力される信号を観察する」

というもの。

プロジェクト内では回路の最上位に位置するが、あくまでテストベンチなので論理合成の対象とならない。

しかし、HDL を使っての記述では、クロックやリセット信号を含むすべての入力信号に値を設定する必要があるので、1から全部書くのはちょっと面倒…。

そんなめんどくさがり屋に朗報!

通りすがりの ある優しい先輩が「裏ワザ」を教えてくれたのだ!

今日はそれをご紹介!!

材料は、デザイン・ファイルのみ! (Verilog HDL もしくは VHDL)

道具は、パソコンと Quartus II を用意。

今回は裏ワザ調理法をわかりやすくお伝えするため、シンプルなデザインで紹介します。

module sample

(

input clk, reset,

output reg [3:0] count

);

always @ (posedge clk or negedge reset)

begin

if (!reset)

count <= 0;

else

count <= count + 1'b1;

end

endmodule

では、調理開始♪

1. 最上位階層のデザインを Start Analysis & Synthesis (Processing メニュー > Start) して論理合成する。

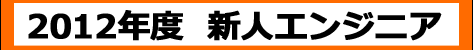

2. テストベンチを生成するため、EDA Tool Settings において、シミュレーションを実施するツール、生成するテストベンチの言語、Time scale を選択する。

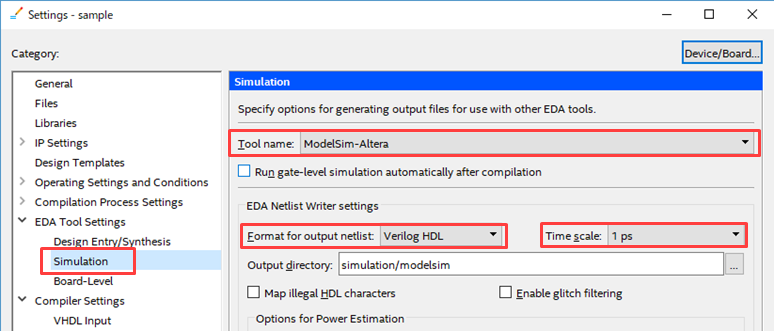

3. Processing > Start > Start Test Bench Template Writer を実行する。

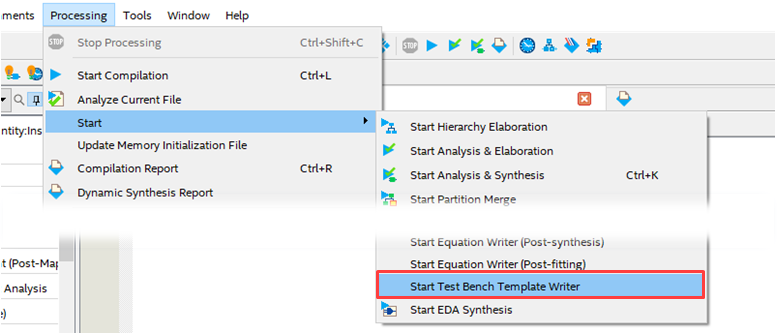

3. 完了したら、メッセージ・ウィンドウに "EDA Netlist Writer was successful." と表示されているのを確認する。

たったこれだけ!!

3分クッキングよりも早くできちゃった!!

※ 論理合成及びテストベンチ生成にかかる時間はお客様のデザインによります。

できあがったテストベンチ・ファイルは、2. で指定したディレクトリ /simulation / modelsim に入っているので、

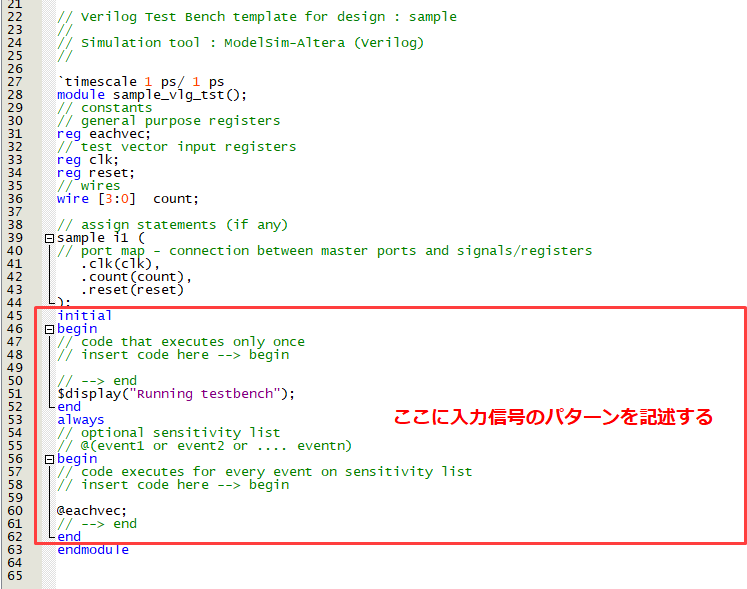

それを Quartus II のテキスト・エディタで開いて、いざ完成したファイルをお披露目。

なんと!最上位階層のデザインからテストベンチに必要な情報を抜粋し、自動的に反映されているではないか!!

このように、自分が作ったデザインの入出力がポート接続されてあるので、

あとは入力信号をどういうものにするのかを記述すれば良い状態になっている。

つまり、テストパターンを入力するのみの状態である。

今回はシンプルな Verilog HDL ファイルに対してのみだったが、

論理合成さえできていれば、もっと複雑なデザインのテストベンチも生成できる。

つまり、デザインが大きければ大きいほど楽ができるということだ!

納期に追われるエンジニアにとって、時間短縮できるこの機能はうってつけ!

これからも色んな機能を知って、仕事の効率化を追及していこう。

やっぱり「面倒くさがり屋」って楽するために色々な手段を考えるから、業務改善を常に考えていて… と、

自分を正当化する頭領だった。