こんにちは。

マクニカで Altera® FPGA 製品の技術サポートをしている アルテラ ハナコ です。

NativeLink とは

Quartus® Prime から EDA ツールを実行させることを NativeLink (ネイティブリンク) と言います。

例えば、Quartus® Prime のメニューをクリックすると、<Questa - AFE が起動し、シミュレーションに必要なコンパイルやロードが実行され、シミュレーション結果を波形ウィンドウに表示>、ここまでが自動的に実行されます。

Questa - AFE の GUI オペレーションがわからない人でもシミュレーションが実施できるだけでなく、オペレーションの作業効率を上げたい人にも 非常にオススメのフローです。

ハナコのつぶやき

IP Catalog や Platform Designer で作成した IP (Intellectual Property) モジュールがデザインに含まれている場合、

シミュレーション・ツールに対してどのシミュレーション・ライブラリーを使えば良いのかわかりますか?

そんな心配を払拭してくれるのが、NativeLink シミュレーション!

この方法なら、IP モジュールをファンクション・シミュレーションするために必要なシミュレーション・ライブラリーをすべて自動的に読み込んでくれるんです。

種類の異なる IP モジュールを複数使用しているデザインは、特に便利ですよ。

NativeLink のサポート環境

NativeLink が使用できる環境を以下に示します。

| 表1. NativeLink サポート環境(注1) | |

| 対応する Quartus Prime |

Quartus® Prime Standard Edition / Quartus® Prime Lite Edition ※ Pro Edition はサポート対象外 (Pro Edition はこちらのコンテンツをご覧ください。) |

|

サポートする |

Aldec Active-HDL / Riviera-PRO Cadence Xcelium* Logic Simulation Siemens EDA Questa Sim Siemens EDA Questa - Altera® FPGA Edition Synopsys VCS |

注1: スケマティックのデザイン (.bdf) は、すべて HDL に変換する必要があります。

<参考 FAQ> Q: 回路図を含んだデザインを ModelSim でシミュレーションしたいのですが、うまくいきません。

注2: 各 EDA ツールの対応バージョンは、ご利用になる Quartus® Prime の各バージョン向けリリースノートをご確認ください。

環境を設定する

NativeLink を実行するための環境をセットアップします。

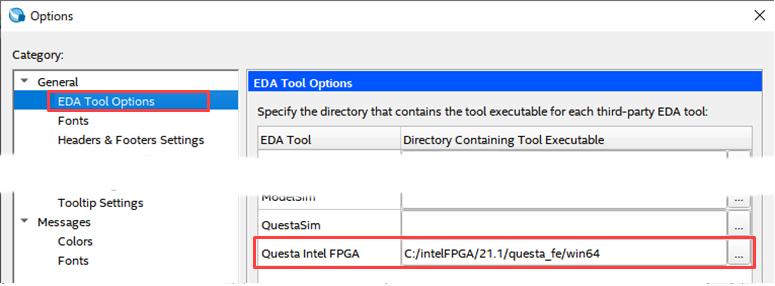

- Quartus® Prime の Tools メニュー ➤ Options ➤ General 下にある EDA Tool Options をクリックします。

- Questa Altera FPGA 行 右端の [...] ボタンをクリックし、実行プログラムが保存されているフォルダーの絶対パスを指定します。

Windows OS であれば questasim.exe が保存されている win64 フォルダーを指定してください。

作業フロー

- Quartus® Prime プロジェクトに、Quartus® Prime でのコンパイルに必要なデザインを全て登録します。

Project メニュー ➤ Add/Remove Files in Project

※ IP を含むデザインの場合には、ハナコ’s ポイント♪① / ハナコ’s ポイント♪② を必ず確認してください。

※ IP を含まないデザインの場合は、2. へ進んでください。

ハナコ's ポイント♪ ①

Platform Designer で作成した IP が含まれる場合は

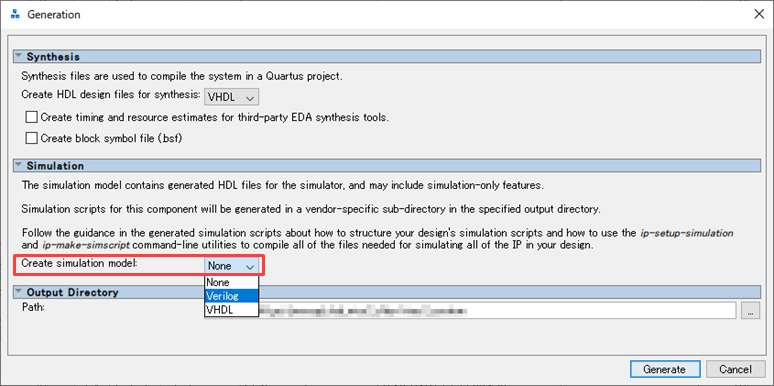

Generate HDL 実行時にポップアップされる Generation ダイアログボックス内の "Create simulation model オプション" を有効にしてください。

生成する言語を選択後に Generate (または Generate HDL) ボタンをクリックすると、シミュレーション・ツール向けのファンクション・モデルも生成されます。

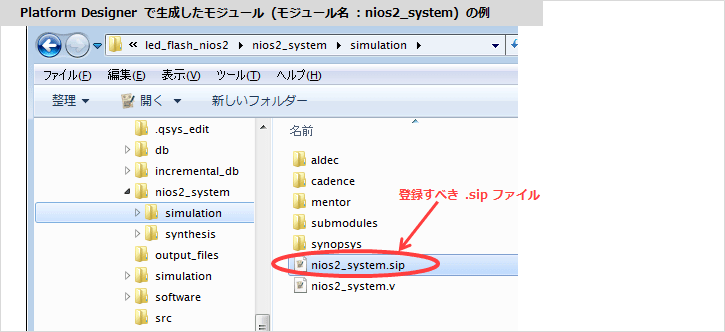

ハナコ's ポイント♪ ②

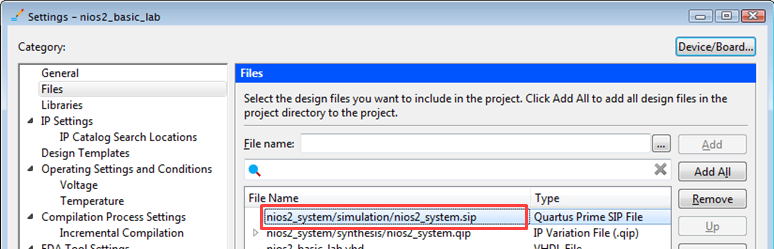

"Platform Designer で作成した IP モジュール"、あるいは "IP Catalog から選択し Platform Designer の GUI ベースで作成した IP モジュール" が

デザインに含まれる場合には、Quartus® Prime の下記メニューにより <ip_name>.qip と同様に <ip_name>.sip を必ず登録してください。

Project メニュー ➤ Add/Remove Files in Project

※ "IP Catalog から IP を選択し、MegaWizard Plug-In Manager ベースの GUI で作成される IP モジュール" は、*.sip ファイルを生成しません。

*.qip ファイルのみプロジェクトに登録してください。

<関連 FAQ> .sip ファイルとはどのようなファイルですか?

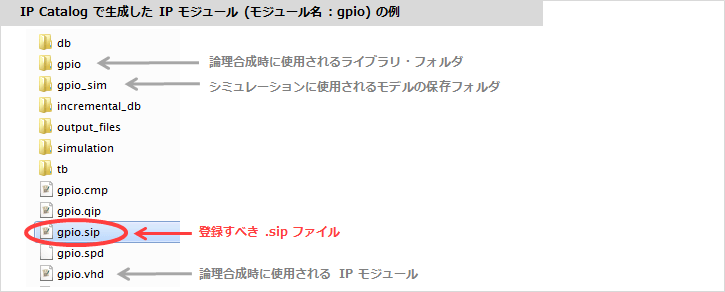

.sip ファイルの生成場所は、IP Catalog / Platform Designer のどちらで IP モジュールを作成したかで異なります。

【IP Catalog で作成した IP モジュール】

<ip_name>.v (または .vhd) が生成されたフォルダ内に .sip ファイルが生成されます。

(※ <ip_name>_sim フォルダと同階層のフォルダにあります。)

<ip_name>. フォルダ ➤ simulation フォルダ内に .sip ファイルが生成されます。

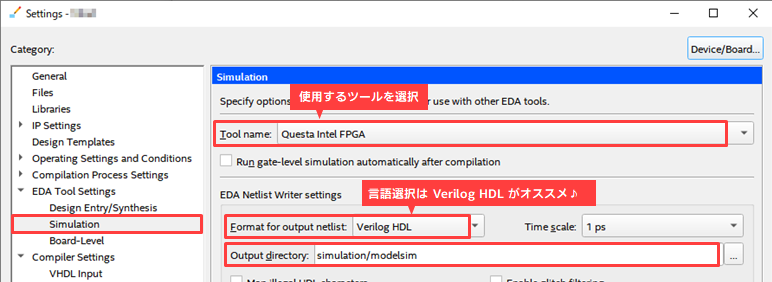

2. Assignments ➤ Settings ➤ EDA Tool Settings ➤ Simulationを選択し、EDA Netlist Writer settings 内の下記項目を設定します。

・ Tool name : Questa Altera FPGA (※ Starter Edition もこちらを選択)

・ Format for output netlist : Verilog HDL (参考: ハナコ's ポイント♪③)

・ Output directory : simulation/modelsim (デフォルトのままを推奨)

ハナコ's ポイント♪ ③

IP 作成時のシミュレーション・モデルやテストベンチが VHDL であっても、ここのオプションは Verilog HDL の選択をオススメします。

この選択言語は、NativeLink 実行用スクリプトの vsim -L コマンドに影響します。

近年の IP は シミュレーション・モデルの言語選択を VHDL で指定しても、下位モデルは SystemVeriog で構成されていることが多く、必然的に Verilog HDL 用のシミュレーション・ライブラリーが必要になります。その場合、vsim -L コマンドで Verilog HDL 用のライブラリーを漏れなく指定する必要があるため、VHDL でモデルを生成しても Format for output netlist は Verilog HDL をご利用ください。

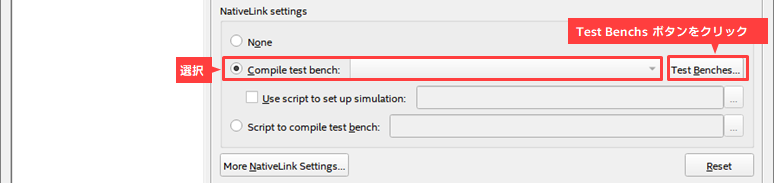

3. NativeLink settings 内にて、テストベンチを登録します。

Compile test bench を選択し、Test Benches ボタンをクリックします。

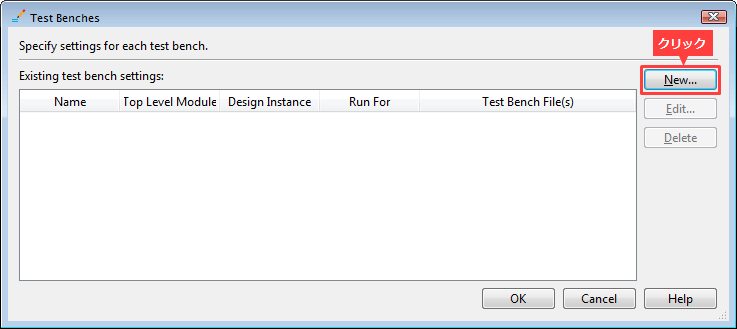

Test Benches ウィンドウの New ボタンをクリックします。

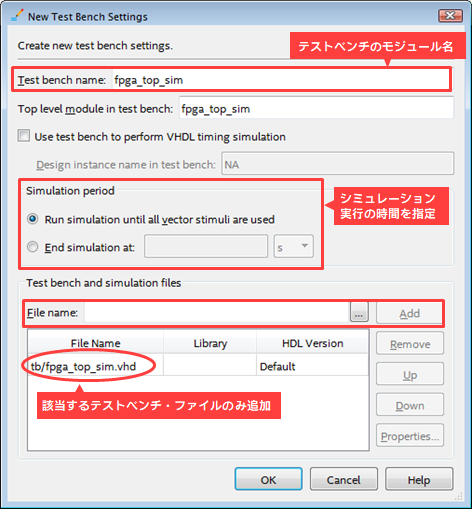

New Test Benches Settings ダイアログボックスにおいて、下記項目を設定します。

・ Test bench name : テストベンチのモジュール名を入力 (下段の Top Level module in test bench 欄も同時入力)

・ Simulation period : シミュレーション実行の終了時間を設定

・ File name : 右端の [...] ボタンをクリックし、テストベンチ・ファイルを選択。Add ボタンで登録。

各ウィンドウを OK で閉じ、Settings ウィンドウへ戻ります。

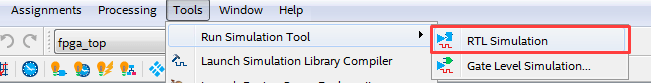

4. NativeLink でファンクション・シミュレーションを実行!

Tools メニュー ➤ Run Simulation Tool ➤ RTL Simulation をクリックします。

※ RTL Simulation 実行には、事前に Analysis & Elaboration または Analysis & Synthesis、あるいは Fitter のプロセスが実行されている必要があります。

ただし、Start Compilation (Processing メニュー) は実行しないでください。EDA Netlist Writer が自動的に実行されてしまい

正常な RTL Simulation 用のスクリプトが生成されません。

(フルコンパイルを実行してしまった場合は、再度 Analysis & Elaboration または Analysis & Synthesis、あるいは Fitter を実行後に

RTL Simulation を行ってください。)

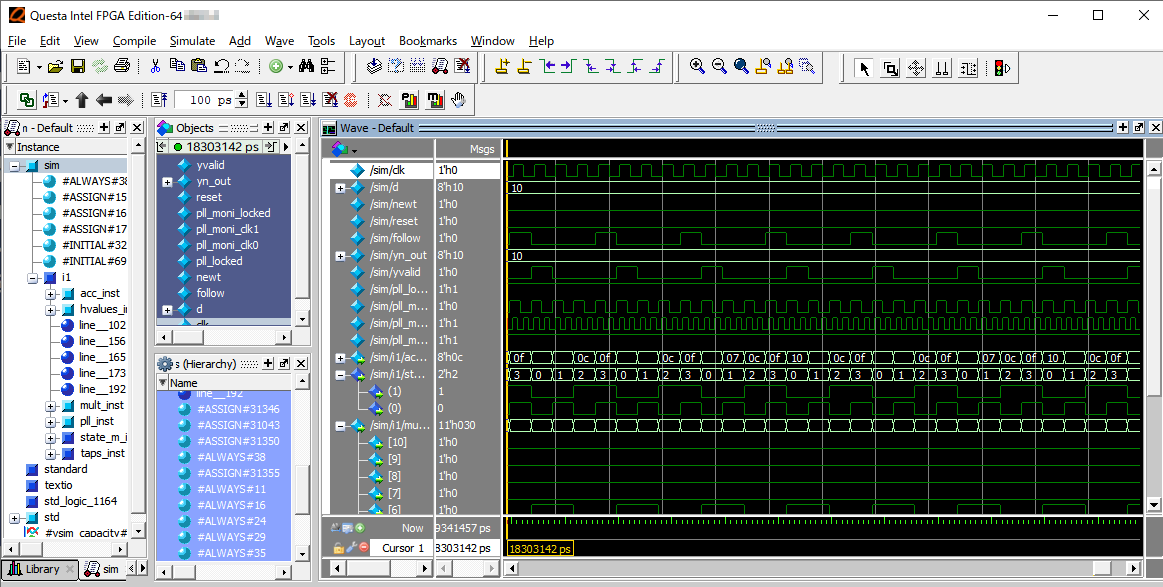

Questa - AFE におけるコンパイル、ライブラリーの適用、ロード、Wave ウィンドウへの信号追加、そしてシミュレーション実行。これらすべてのオペレーションが自動的に実施され、Wave ウィンドウに波形が表示されます。

ユーザーは Wave ウィンドウを確認するだけ!なんて効率が良いことでしょう♪

みなさんも是非、ファンクション・シミュレーションは NativeLink で実施してみてください。

おすすめ記事/資料はこちら

Quartus® Prime Pro Edition で生成した IP を含むデザインを Questa* - Altera® FPGA Edition でファンクション・シミュレーションする方法

シミュレーションで Altera® FPGA の内部信号をモニターしよう <Questa* - Altera® FPGA Edition 編>

シミュレーションで Altera® FPGA の内部信号をモニターしよう <テストベンチ記述編>