デザインの論理検証の重要性とテストベンチ

FPGA 開発のデザイン (論理回路) 設計は、Verilog-HDL や VHDL といったハードウェア記述言語 (HDL) が主流になっていることは皆さんもご存じのことと思います。

コンパイルや実機デバッグの前には、HDL で設計したデザインが正しく動作するかを確認するための検証作業が必要です。デザインの論理的な検証はシミュレーションを実施することになりますが、シミュレーションをするにはデザインへの入力条件 (テスト条件) を記述した "テストベンチ" がデザインとは別に必要です。そして、そのテストベンチも主に設計者がデザインと同様に HDL で記述することになります。

テストベンチを作る前には、どのような検証を行うかを考える必要があり、検証対象のデザインがどのような動作をするべきかを知っていなければなりません。それらをきちんと把握した上で、テストベンチを作成してください。

ここでは、はじめての方にもわかるようなテストベンチの作成に最低限必要となりそうな内容に絞って、記述例も交えて説明していきます。

なお 参考として、以下のページから演習用のデータをダウンロードできます。

テストベンチとデザイン (回路) の関係

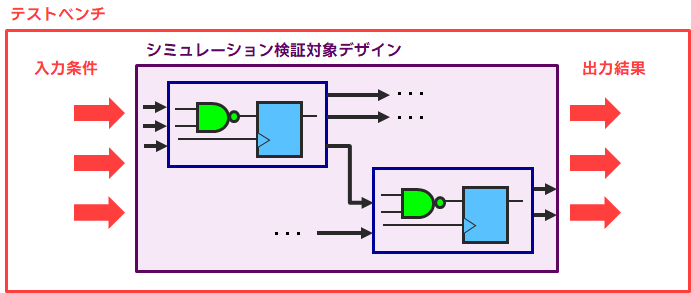

FPGA 内にデザイン (論理回路) を設計するには、主に階層設計手法が用いられます。テストベンチは階層的にいうと、FPGA デザインの 検証対象デザイン (主に最上位階層) よりも上位の階層に位置します。テストベンチ内で 検証対象デザインに対する入力条件 (クロック入力やリセット入力、その他の入力など) を HDL で記述し、下位階層に位置する FPGA デザインの検証対象デザインに入力させます。入力させた信号が作成したデザインを経由し、結果が出力され、その結果をシミュレーターで確認することで作成したデザインの動作が正しいかどうかを判断します。

ここからは、Verilog-HDL と VHDL のそれぞれにおける具体的なテストベンチの記述方法を解説します。

なお、テストベンチのモジュール名およびエンティティ名は任意です。検証対象デザイン名の末尾に _tb や _sim をつけているケースを多く見かけますが、これは決してルールではありません。自由に名前を決めてもらって大丈夫です。

コーヒー・ブレイク:シミュレーター

設計したデザインをシミュレーションするには、シミュレーターが必要です。アルテラ FPGA ユーザー向けには、ModelSim-Altera Edition をオススメします。ModelSim-Altera Edition の使い方については、公開中の資料をご覧ください。

コーヒー・ブレイク:NativeLink 機能の活用

アルテラの FPGA/CPLD 開発ツールの Quartus Prime / QuartusII 開発ソフトウェアは、EDA シミュレーターを Quartus Prime / Quartus II 上から実行させてシミュレーション結果を表示させるところまで自動実行させることができます。

この NativeLink 機能を使用することで、シミュレーターの起動やコンパイル、デザインのロードなどの作業をわざわざ手動で実行する手間が省けます。ただし、事前にテストベンチを作成しておく必要があるので、それをお忘れなく...

FPGA のファンクション・シミュレーションは NativeLink で解決しよう

※ EDA:電子機器や半導体など電子系の設計作業を自動化し、支援するためのソフトウェア、ハードウェアおよび手法の総称。