FPGA 開発においてコンパイルを実行する前に、作成した論理回路 (デザイン) が期待通りの動作になっているかを確認することは

重要なことです。

ハードウェア言語 (HDL) による設計が主流である現在では、論理シミュレーションも言語でおこないます。

シミュレーションには入力パターン情報が欠かせませんが、その入力パターンも設計者が HDL で記述し、それを "テストベンチ" と呼んでいます。

ここでは、テストベンチの超基本的な記述について紹介します。

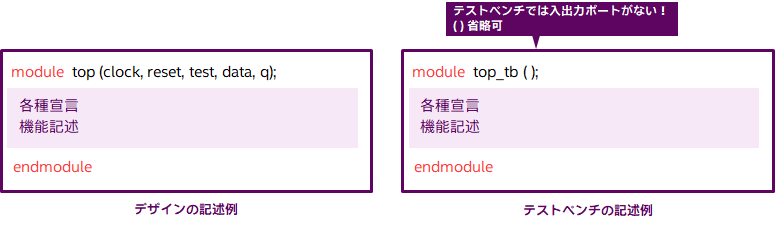

モジュールの書式

Verilog-HDL の場合、テストベンチを作成する時もデザインを作成するときと同じように module <モジュール名> から始めます。しかし、一般的にテストベンチには入出力ポートが存在しないため、モジュール名の後にポート・リストを記述する必要はありません。また、入出力ポートの宣言も必要ありません。したがって、各種宣言や機能記述のところには検証対象となるデザインへ入力する信号の入力条件を HDL で記述していきます。

モジュールの書式(詳細) & 信号の宣言

「各種宣言と機能記述」をもう少し細かくすると、「信号の宣言」と「下位階層(シミュレーション対象モジュール)の呼び出し」、「下位階層(シミュレーション対象モジュール)への入力条件の記述」に分けることができます。「信号の宣言」のところは、先ほども触れたようにテストベンチには入出力ポートが存在しないので、input や output、inout を使用したポートの属性を宣言する必要はありません。テストベンチではテスト入力として使う信号のデータ型をレジスタ宣言(reg 宣言)し、反対に検証対象の出力ポートに接続するテストベンチで値を与えない信号のデータ型はワイヤー宣言(wire宣言)します。

例)

reg clock, reset, test;

reg [7:0] data;

wire [7:0] q;

下位階層(シミュレーション対象モジュール)の呼び出し

「下位階層(シミュレーション対象モジュール)の呼び出し」のところは、デザインで一般的に使用する下位階層の呼び出しの記述とまったく同じです。

下記は、シミュレーション対象モジュールのインスタンス名を “u1” とした例です。

例)

top u1 (

.clock (clock),

.reset (reset),

.test (test),

.data (data),

.q (q)

);

下位階層(シミュレーション対象モジュール)への入力条件の記述

次に「下位階層(シミュレーション対象モジュール)への入力条件の記述」について解説します。ここでは おもに、

- 常にレベルが固定している信号の記述

- 一定間隔で値がインクリメントする信号の記述

- 非定期的に ‘1’(Hレベル)と‘0’(Lレベル)を繰り返す信号の記述

- 定期的に‘1’(Hレベル)と‘0’(Lレベル)を繰り返す信号の記述

について説明します。これらをマスターすれば、テストベンチを自分で書けるようになります。

なお、ここで紹介した以外の記述方法もありますので、後々勉強して習得してください。

1. 常にレベルが固定している信号の記述

シミュレーションの開始には、initial 文 を記述します。記載した式が1度だけ実行されます。シミュレーション実行中にレベルの変化がない信号は、initial 文 に続いて信号名とレベルを記述すれば良いです。

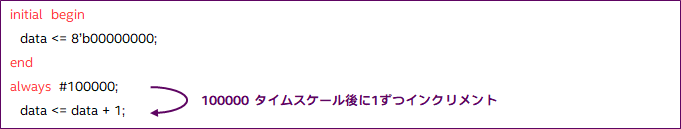

2. 一定間隔で値がインクリメントする信号の記述

まず、initialbegin の後に初期値を記述します。その後 always 文 を使って一定間隔でインクリメンタルする式を記述します。

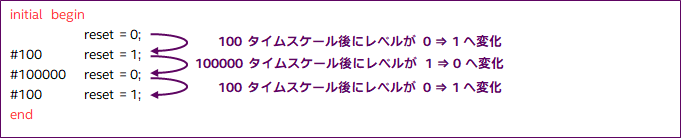

3. 非定期的に ‘1’(H レベル)と ‘0’(L レベル)を繰り返す信号の記述

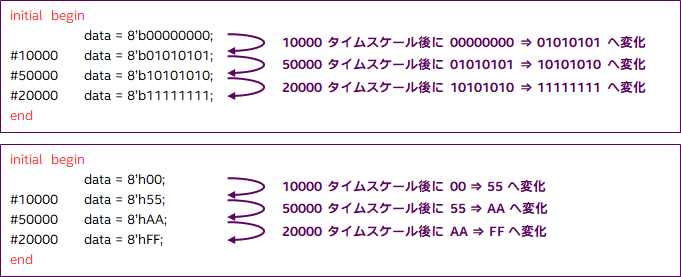

非定期的にレベルが変化する信号は、1つの initial 文 に begin~end を使って、その間に複数の式を記述します。

バスなどの複数ビットがまとまった信号は、以下のように記述します。8ビットの信号であれば、8’b の後に各ビットのレベルを記述します。b は 2進数 の意味です。h を使って 16進数 表示も可能です。

4. 定期的に ‘1’(H レベル)と ‘0’(L レベル)を繰り返す信号の記述

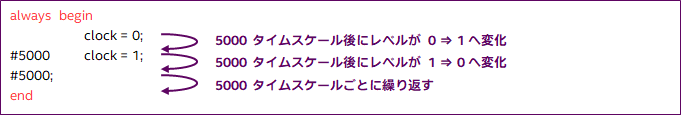

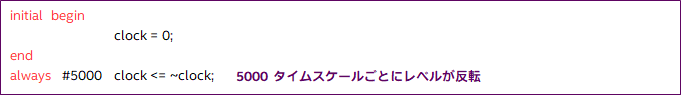

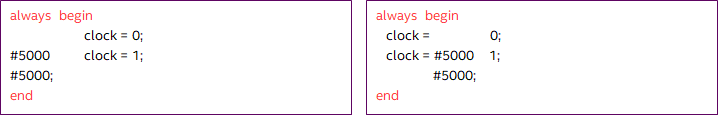

クロックのように定期的に‘1’(Hレベル)と‘0’(Lレベル)を繰り返す信号を記述する時は、先ほどのような方法で永遠に記述する必要はなく、以下のように記述します。ここでは、2つの記述方法を紹介します。どちらも同じ入力条件になります。

- 方法1

- 方法2

サンプル・デザイン

以下のページから、演習データを参考としてダウンロードできます。このサンプルではテストベンチの記述も使われているので、参考にしてください。

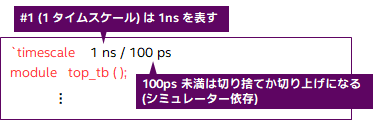

コーヒー・ブレイク:`timescale

テストベンチの冒頭に `timescale の記述を見かけたことはありませんか?これはシミュレーション時刻の単位を指定するための記述です。

単位(fs,ps,ns, us, ms,s)を添えて記述します。`timescale の記述は、通常はテストベンチにのみに記述します。

`timescale <1タイムスケールあたりの実時間>/ <丸めの精度>

それから、式の中におけるシミュレーション時刻を記述する位置については、下記のどちらでも大丈夫です。

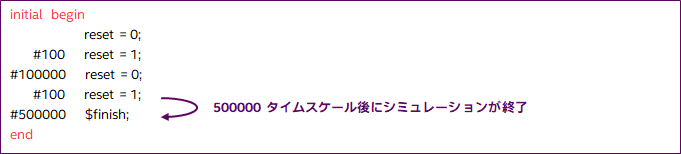

コーヒー・ブレイク:$finish

テストベンチ中の式に $finish という記述を見かけます。これは、この行まで実行されるとシミュレーションが終了するというものです。この $finish がないと、シミュレーションが終了しません。時間指定してシミュレーションすれば $finish がなくても終わりますが、時間指定なしでシミュレーションを実行した場合は、この $finish を見付けてそこまで到達したら終了させます。どこか1か所で良いので、この $finish を入れましょう!