概要

『Verilog-HDL 入門編トライアル・コース』は、マクニカグループの株式会社アルティマ (現 (株)マクニカ アルティマカンパニー) と株式会社エルセナで 2016年3月まで開催していたワークショップです。

定期開催の終了に伴い、リニューアルして同じ内容を Web ページに掲載することになりました。

本ワークショップの対象者とコンセプト、アジェンダは、以下の通りです。

| 対象者 | Verilog-HDL によるデジタル論理回路設計が初めての人 |

| コンセプト | Verilog-HDL の概要を理解して、基本的な記述方法を習得する |

| アジェンダ |

言語設計の概要 ・ assign 文による組み合わせ回路 ・ always 文による組み合わせ回路 ・ always 文による順序回路 ・ 下位モジュールの呼び出し |

マテリアル

ここでは、マテリアル各種を提供しています。

テキストや演習マニュアル、演習データをダウンロードすれば、自分のペースで学習できます。

| テキスト |

クリックして閲覧 またはダウンロード |

説明が簡潔にまとめられたテキストです。 補足説明も話し言葉で書かれているので、非常にわかりやすいです。 |

| 演習マニュアル |

クリックして閲覧 またはダウンロード |

テキストの内容をもとに演習をやることで、理解度が増します。下記演習データと共にご利用ください。 この演習をおこなうには、Questa または ModelSim (共に Intel FPGA Edition を含む) が必要です。 このマニュアルは ModelSim-Altera Edition をベースに作成されていますが、Questa と GUI メニューが同じなためツールを置き換えてご利用いただけます。 Intel FPGA Starter Edition は無償で使用することができます。(Questa-Intel FPGA Starter Edition は無償用のライセンス取得と設定が必須 : こちらを参照) |

| 演習データ |

クリックしてダウンロード |

zip ファイルを解凍すると exe ファイルが生成されます。その exe ファイルを実行して、任意のフォルダーに展開してください。 デフォルトは C:\lab\verilog_lab に展開される仕様です。 |

テストベンチ(シミュレーションするならテストベンチが必要!)

<デザインの論理検証の重要性とテストベンチ>

FPGA 開発のデザイン (論理回路) 設計は、Verilog-HDL や VHDL といったハードウェア記述言語 (HDL) が主流になっていることは皆さんもご存じのことと思います。

コンパイルや実機デバッグの前には、HDL で設計したデザインが正しく動作するかを確認するための検証作業が必要です。デザインの論理的な検証はシミュレーションを実施することになりますが、シミュレーションをするにはデザインへの入力条件 (テスト条件) を記述した "テストベンチ" がデザインとは別に必要です。そして、そのテストベンチも主に設計者がデザインと同様に HDL で記述することになります。

テストベンチを作る前には、どのような検証をおこなうかを考える必要があり、検証対象のデザインがどのような動作をするべきかを知っていなければなりません。それらをきちんと把握した上で、テストベンチを作成してください。

ここでは、はじめての方にもわかるようなテストベンチの作成に最低限必要となりそうな内容に絞って、記述例も交えて説明していきます。

<テストベンチとデザイン (回路) の関係>

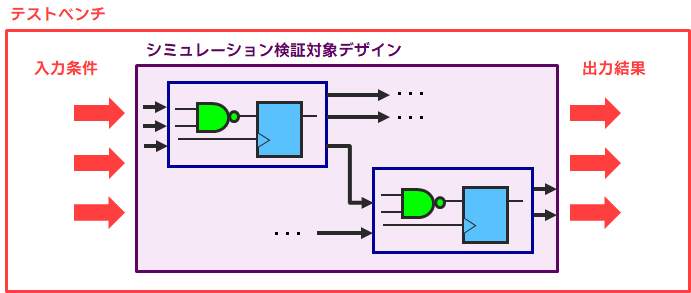

FPGA 内にデザイン (論理回路) を設計するには、主に階層設計手法が用いられます。テストベンチは階層的にいうと、FPGA デザインの 検証対象デザイン (主に最上位階層) よりも上位の階層に位置します。テストベンチ内で 検証対象デザインに対する入力条件 (クロック入力やリセット入力、その他の入力など) を HDL で記述し、下位階層に位置する FPGA デザインの検証対象デザインに入力させます。入力させた信号が作成したデザインを経由し、結果が出力され、その結果をシミュレーターで確認することで作成したデザインの動作が正しいかどうかを判断します。

Verilog-HDL の基本的なテストベンチの記述方法は、下記ページで解説しています。

はじめてみよう!テストベンチ ~Verilog-HDL 編~

コーヒー・ブレイク:シミュレーター

設計したデザインをシミュレーションするには、シミュレーターが必要です。

インテル FPGA ユーザーには Questa - Intel® FPGA Edition をオススメします。

下記ドキュメントは Questa - Intel® FPGA Edition の前身ツールである ModelSim-Altera で構成されていますが、ツールのオペレーションは同じですので、そのままご参考いただけます。

ModelSim-Altera Edition - RTL シミュレーション(Verilog-HDL)

なお、Quartus® Prime Standard Edition には "NativeLink シミュレーション" と言うシミュレーション手法があります。

詳細は次のコンテンツをご覧ください。