こんにちは。

マクニカで Altera® FPGA 製品の技術サポートをしている アルテラ ハナコ です。

Questa* - Altera® FPGA Edition などでファンクション・シミュレーションを実施する際に、Altera® FPGA のピンレベルで信号を参照 (モニター) することはもちろんですが、同時に FPGA の内部信号も参照したいですよね?

シミュレーションで FPGA の内部信号を Wave ウィンドウに表示させるには、以下の方法があります。

[A] テストベンチに記述して表示する

[B] Questa* - Altera® FPGA Edition の GUI 操作で表示する (リンクはこちら)

今回は [A] テストベンチに記述して表示する方法(つまり、FPGA の内部信号を Wave ウィンドウに表示させるテストベンチの書き方)をご紹介します。

サンプル・デザイン

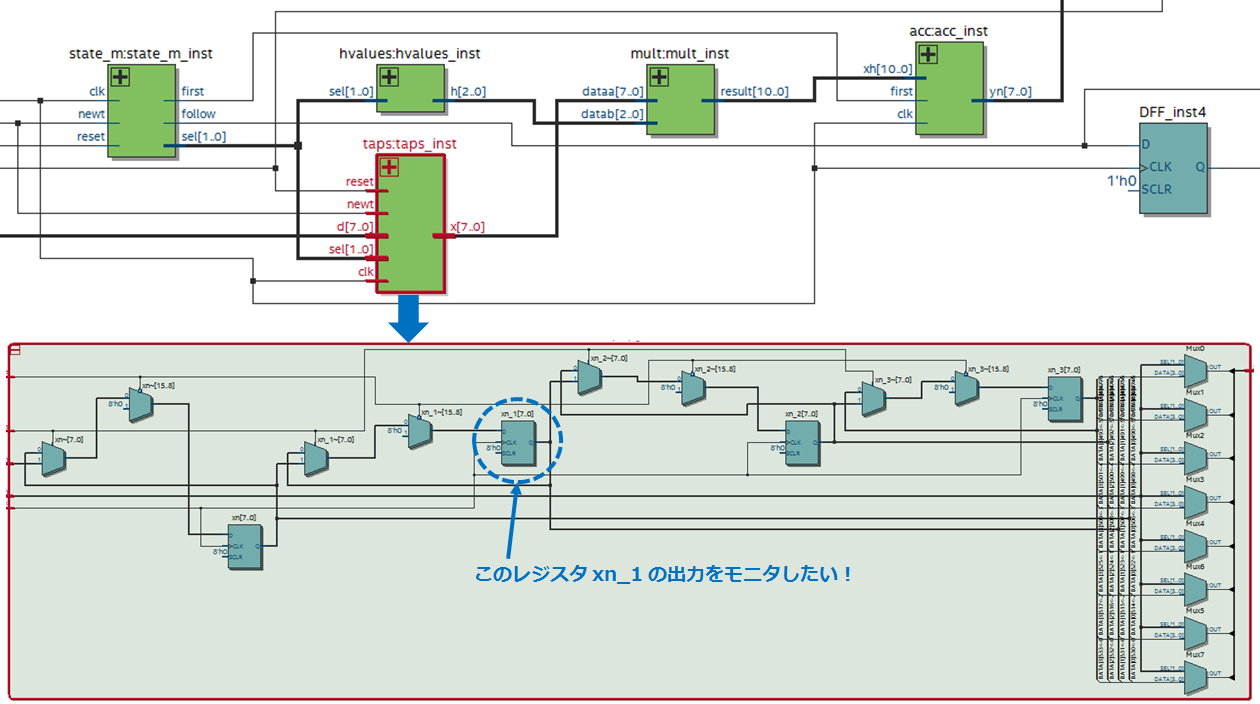

下図は、あるサンプル・デザインを Quartus® Prime の RTL Viewer で表示したものです。

このデザインの下位モジュールに taps (インスタンス名: taps_inst) があります。

今回は、taps の内部のレジスタ xn_1 (7bit) の出力を参照する場合を例に挙げてご案内します。

なお、テストベンチにおける FPGA の最上位モジュールのインスタンス名は、fpga としています。

テストベンチの書き方

デザインの内部信号をモニターするためのテストベンチの書き方は、言語によって異なります。

Verilog HDL ユーザーは こちら をご覧ください。

VHDL ユーザーは こちら をご覧ください。

下位階層に Verilog HDL と VHDL が混在していても、今回の手法で参照可能です。

Verilog HDL の書き方

Verilog HDL には、下位階層モジュールの内部信号を参照する記述方法が一般的に存在します。

内部信号を参照するためのローカル信号を wire で宣言し、目的の信号までの階層パスを “.” (ドット)で区切ります。

階層パスはインスタンス名を使って指定します。

例えば、taps:taps_inst 内のレジスタ xn_1 の出力を参照したい場合には、以下のように記述します。

wire [7:0] moni = fpga.taps_inst.xn_1;※ moni は参照する内部信号の接続先となる信号名で、名称はユーザーの任意です。

VHDL の書き方

VHDL には、Verilog HDL のような内部参照の文法がありません。

でも Questa*(Questa* - Altera® FPGA Edition を含む)では、Signal Spy 機能 で対応できちゃうんです!

VHDL では、テストベンチに 以下の util パッケージ(modelsim_lib ライブラリー)を追記します。

library modelsim_lib;

use modelsim_lib.util.all;そして、内部信号を参照するためのローカル信号を signal 宣言で追加し、process 文を用いて init_signal_spy で指定します。

init_signal_spy (src_object, dest_object,verbose);src_object: 参照する信号の階層パス

dest_object: 参照する信号の接続先の信号名の階層パス

verbose: メッセージ出力; 1、出力しない;0

階層パスはインスタンス名を使って指定します。

例えば、taps:taps_inst 内のレジスタ xn_1 の出力を参照したい場合には、以下のように記述します。

※ moni は参照する内部信号の接続先となる信号名で、名称はユーザーの任意です。

architecture bench of top_tb is

・・・

signal moni : std_logic_vector (7 downto 0);

・・・

begin

・・・

monitor : process

begin

init_signal_spy("/fpga/taps_inst/xn_1", "/moni", 0);

wait;

end process monitor;

・・・

今回は、デザインの内部信号をモニタするテストベンチの書き方をご紹介しました。

この記述で、シミュレーションの作業効率がアップしますよ~。お試しあれ!

おすすめ記事/資料はこちら

シミュレーションで Altera® FPGA の内部信号をモニタしよう (Questa*-Altera® FPGA Edition の操作方法)

Altera® FPGA のファンクション・シミュレーションは NativeLink で解決しよう