こんにちは。マクニカで Altera® FPGA 製品の技術サポートをしている 鷲宮タロー です。

最近の FPGA には標準で Phase Locked Loop (PLL) が搭載されていて、多くのユーザーがFPGA 内蔵の PLL を使っていると思います。

異なる周波数のクロックを簡単に生成することができて便利ですが、なんとなく使っているユーザーも多くいるのではないでしょうか?

そこで、このページでは今さら聞けない基本原理からアーキテクチャー、IP の生成などの基本的な内容について説明していきたいと思います。

何から手を付ければいいのか?と疑問に思ったら、ぜひこの記事を読み進めてください。

なお、この記事では特に断りのない限り汎用的に使う PLL を対象としており、トランシーバー用の PLL は含みません。

内容

・ PLL のロケーション

・ クロック・ネットワーク

・ ピン・アサインメントのコツ

● IP の生成

・ Altera IOPLL

・ Altera PLL

・ ALTPLL

PLL の基本原理

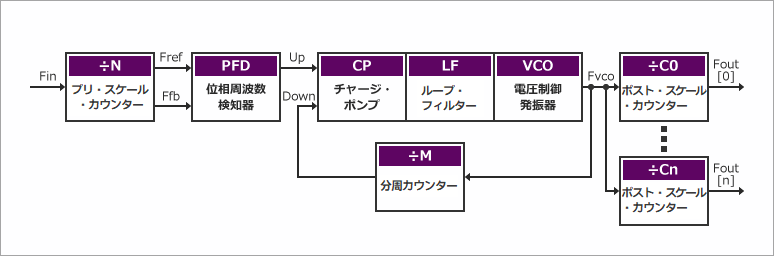

PLL の基本的な原理は、概ね下図のとおりです。(FPGA のシリーズやファミリーによって、細かいアーキテクチャーは異なります。)

そして、PLL 内の各ブロックを簡単にまとめたものが、下の表です。

| 略 称 | ブロック名 | 説 明 |

| PFD | 位相周波数検知器 | フィードバック・クロック(Ffb)と入力リファレンス・クロック(Fref)の立ち上がりエッジを比較します。PFD は VCO が高い周波数で動作する必要があるか、低い周波数で動作する必要があるかを決定する Up 信号または Down 信号を生成します。 |

| CP | チャージ・ポンプ | チャージ・ポンプが Up 信号を受信すると、電流はループ・フィルターに駆動されます。Down 信号を受信すると、電流はループ・フィルターから引き出されます。 |

| LF | ループ・フィルター | Up 信号と Down 信号を PFD から VCO のバイアスに使用する電圧に変換します。また、LF はチャージ・ポンプからグリッチをフィルターし、電圧のオーバ・シュートを防ぎます。これにより、VCO のジッターを最小限に抑えます。 |

| VCO | 電圧制御発振器 | VCO の動作速度は、チャージ・ポンプからの電圧によって決まります。VCO の周波数(Fvco)を入力基準周波数(Fref)よりも高くするために、分周カウンター(M)がフィードバック・ループに挿入されます。 VCO の周波数は、次の式を用いて算出します。 Fvco = Fref * M = Fin * M/N 式中の Fin は PLL への入力クロック周波数であり、N はプリ・スケール・カウンターです。VCO 周波数は重要なパラメーターであり、PLL の適切な動作を確実にするために、Quartus® Prime はデザインのクロック出力および位相シフト要件に基づいて、VCO 周波数を推奨される範囲内に自動的に設定します。 |

| ÷M / ÷N | 分周カウンター / プリ・スケール・カウンター | VCO の周波数(Fvco)を入力基準クロックよりも高くするために、分周カウンター(÷M)がフィードバック・ループに挿入されます。VCO の周波数(Fvco)は入力基準クロック(Fref)の m 倍に等しくなり、入力基準クロック(Fref)は入力クロック(Fin)をプリ・スケール・カウンター(÷N)で割った数値に等しくなります。 |

| ÷Cn | ポスト・スケール・カウンター | VCO 出力は、複数のポストスケール・カウンター(C[n:0] )を供給することができます。これらのポスト・スケール・カウンターにより、PLL が多数の調和関係にある周波数を生成することが可能になります。 |

PLL へのリセットが解除されると、リファレンス・クロックをもとに設定された周波数のクロックを生成するために動き出します。

PFD(位相周波数検知器)では Fref と Ffb の位相や周波数を比較して、これらが等しくなるまで Up / Down 信号を出力し続けます。

そして、等しくなると いわゆるロック状態となり、安定したクロックが出力されます。

(ロック状態は locked 信号でモニターできます。基本原理の図では、locked ピンは省略しています。)

FPGA のアーキテクチャー

それでは、PLL は FPGA のどこに搭載されているのでしょうか?

それはデバイス・ファミリーによって異なります。

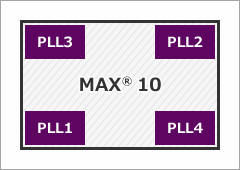

ここでは、MAX® 10 を例に説明します。

MAX® 10 はラインナップやパッケージにより、PLL の搭載数が 2個(PLL1 と PLL2)と 4個(PLL1 と PLL2、PLL3、PLL4)のデバイスが存在します。

そして 図のように、パッケージの四隅に搭載されています。

クロック・ネットワーク

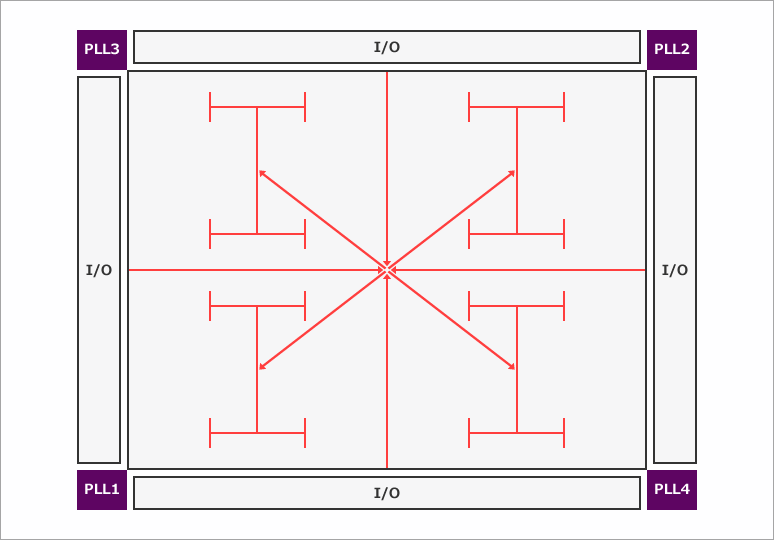

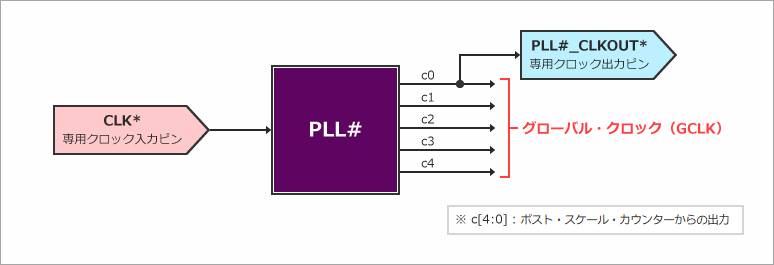

MAX® 10 には、デバイス全体に張り巡らされたグローバル・クロック(GCLK)が存在します。

このグローバル・クロックは、スキューが小さくなるように予め調整されているので、クロックやリセットのようのファンアウトの多い信号に最適です。

Quartus® Prime はコンパイル時にファンアウトの多い信号を自動的にグローバル・クロックに割り当ててくれるので、通常はユーザーが意識する必要はありません。

グローバル・クロックに割り当てたい信号がある場合は、ユーザーが Quartus® Prime で制約することもできます。

大規模なデバイスではグローバル・クロックの他に、デバイスを 4分割したエリア内に張り巡らされたリージョナル・クロック(RCLK)が存在するデバイスもあります。

クロックのピン・アサインメントのコツ

PLL への入力クロック(リファレンス・クロック)用のピンや PLL で生成したクロックを FPGA から出力させたい時のピンは、デバイス・ファミリーによって推奨ピンが存在します。

- FPGA 外部からのクロックを PLL のリファレンス・クロックにする場合、専用クロック入力ピン(Dedicated Clock Pin/CLK*)の使用を推奨します

- PLL 出力クロックは、FPGA 内部のグローバル・クロック(GCLK)と専用クロック出力ピンに接続できます

- FPGA 外部にクロックを出力させたい場合は、専用クロック出力ピン(PLL External Clock Output/PLL#_CLKOUT*)の使用を推奨します

- PLL のロケーションにより、使用できる専用クロック・ピンが決まっています

詳しい情報は、MAX® 10 のドキュメントに書かれています。

MAX® 10 の PLL やクロック・ネットワーク ※ MAX 10 Dedicated Clock Input Pin Connectivity to PLL を参照

MAX® 10 ピン接続ガイドライン

MAX® 10 では、PLL 出力クロックを FPGA 外部に出力させたい場合、c0 出力を推奨しています。

c0 以外でもコンパイルが通れば実現は可能ですが、やはり専用配線を使うことをお勧めします。

他のデバイスの詳細は、ターゲット FPGA のピン接続ガイドラインを参照してください。

ピン接続ガイドライン

また、各デバイスファミリーにおける PLL やクロック・ネットワークについては、Altera® FPGA のドキュメントをご覧ください。

Stratix® シリーズ

Stratix® 10 の PLL やクロック・ネットワーク

Stratix® V の PLL やクロック・ネットワーク ※ Clock Networks and PLLs in Stratix V Devices 参照

Arria® シリーズ

Arria® 10 の PLL やクロック・ネットワーク ※ Clock Networks and PLLs in Arria 10 Devices 参照

Arria® V の PLL やクロック・ネットワーク ※ Clock Networks and PLLs in Arria V Devices 参照

Cyclone® シリーズ

Cyclone® 10 GX の PLL やクロック・ネットワーク ※ Clock Networks and PLLs in Cyclone 10 GX Devices 参照

Cyclone® 10 LP の PLL やクロック・ネットワーク ※ Clock Networks and PLLs in Cyclone 10 LP Devices 参照

Cyclone® V の PLL やクロック・ネットワーク ※ Clock Networks and PLLs in Cyclone V Devices 参照

Cyclone® IV の PLL やクロック・ネットワーク ※ Clock Networks and PLLs in Cyclone V Devices 参照

MAX® シリーズ

MAX® 10 の PLL やクロック・ネットワーク

※ MAX® V や MAX® II などの CPLD には、PLL が搭載されていません。

IP の生成

Altera® FPGA のデバイス・ファミリーによって PLL のアーキテクチャーが異なるので、選択する IP が異なります。

PLL を FPGA デザインに実装するには、Quartus® Prime の IP Catalog や、Platform Designer システム統合ツール内の IP Catalog から、対応する PLL の IP を選択します。

(Quartus® Prime のプロジェクトを開いた状態であれば、ターゲットの FPGA に対応する PLL IP のみ選択できます。)

| デバイス | Altera IOPLL | Altera PLL | ALTPLL |

| Stratix® 10 | ✔ | ||

| Stratix® V | ✔ | ||

| Arria® 10 | ✔ | ||

| Arria® V | ✔ | ||

| Cyclone® 10 GX | ✔ | ||

| Cyclone® 10 LP | ✔ | ||

| Cyclone® V | ✔ | ||

| Cyclone® IV | ✔ | ||

| MAX® 10 | ✔ |

それぞれの PLL の設定については、別記事で紹介します。

- Altera® FPGA の PLL - IOPLL Altera FPGA IP 編

- Altera® FPGA の PLL - PLL Altera FPGA IP 編

- Altera® FPGA の PLL - ALTPLL 編