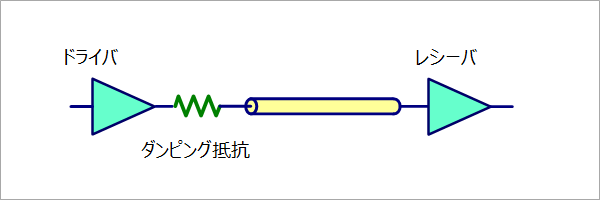

信号伝送では、図1 に示すように、ドライバとレシーバとを 1対1 で接続することが一般的です。この場合には、ドライバの駆動能力を適切に選択するか、最適なダンピング抵抗を用いることによって、波形乱れを避けることができます。

ダンピング抵抗については、『ダンピング抵抗の値ってどのように決めるの?』や『もっと簡単に決めるダンピング抵抗の値』をご覧ください。

多くの配線の中には、1対1 ではなくて、信号を分岐することがあります。この信号の分岐がシグナルインテグリティの面では最も厄介です。

信号の分岐を分類すると、以下のようになります。

(1) 同じ信号を複数個所に分配する

(2) バス接続(メモリモジュール)

(3) 意図しない分岐

(1) の例-1 配線の途中からの分岐

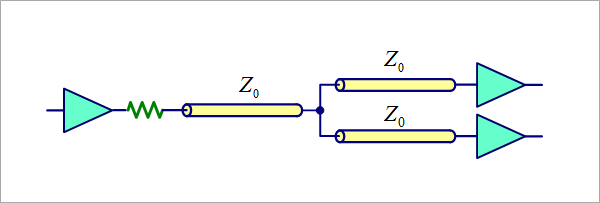

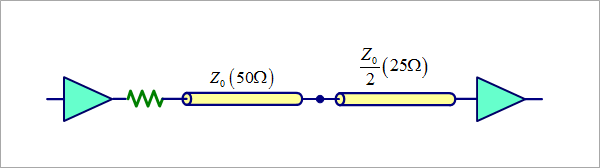

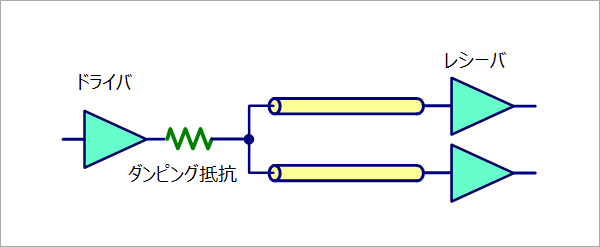

図2は、ドライバから 1本の線路で信号を送り、途中から 2本に分けた例です。図3 は 図2 の回路の等価回路です。

2本の線路が並列に接続されるので、並列接続された部分は特性インピーダンスが半分になることと等価です。線路の特性インピーダンスを、Z0=50Ω とすると、50Ω から 25Ω になる個所で反射が生じます。この接続点における反射係数が、(25-50)/(25+50)=-1/3 なので、かなり大きな反射です。

反射係数については, 『豆知識:反射係数』を参照ください。

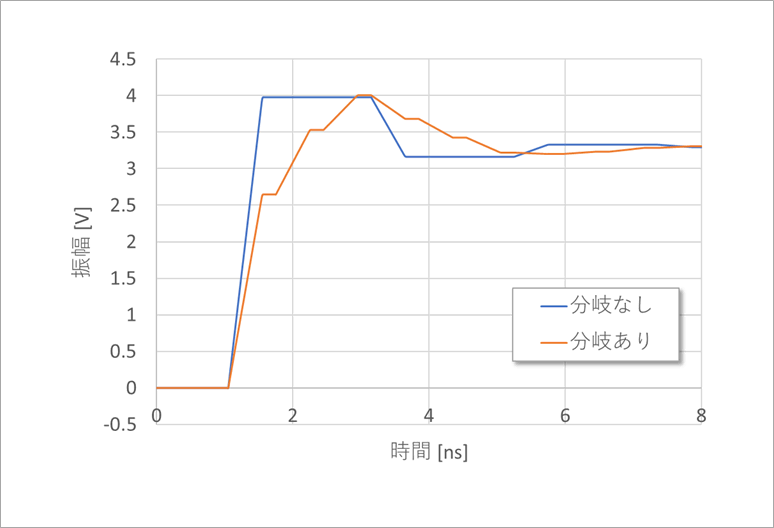

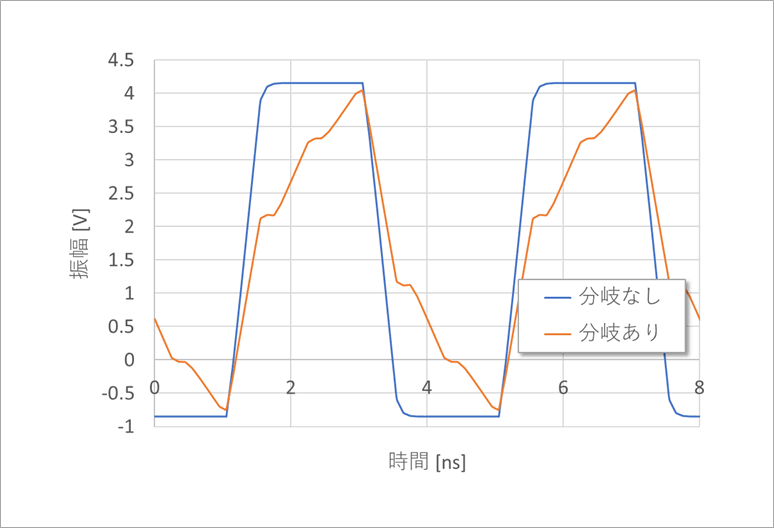

図4 は、分岐がない場合と分岐があるときの遠端の波形です。この程度の波形乱れなら何とか許容できる範囲のように見えます。

図4 は、信号がローからハイに変化する、いわゆる、ステップ波形の応答を示しています。しかし、実際には、パルス幅が狭いことが多く、例えば、ローが 2ns、ハイが 2ns の繰り返し波形の場合には 図5 のようになり、立ち上がりの段がスレッショールド付近に近づくので注意が必要です。パルス幅や周期を変えると、繰り返し波形も変化します。

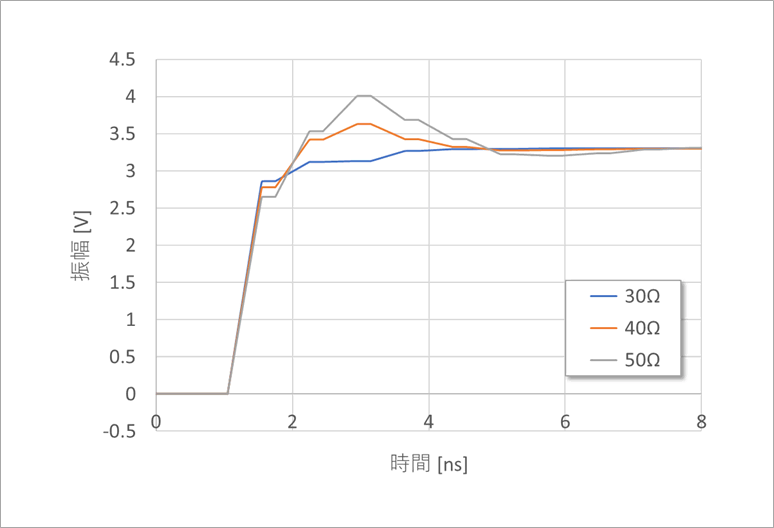

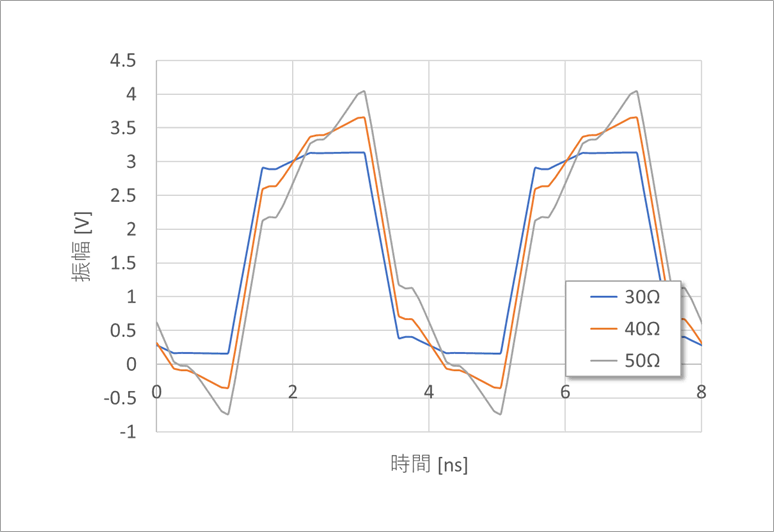

この形態で、なるべく反射を減らしたいなら、ドライバ側の線路のパターン幅を広くして、特性インピーダンスを低くします。図6 がステップ応答で、図7 が繰り返し波形です。両図は、ドライバ側を 30Ω~50Ω、その先を 50Ω 2本に分岐した例です。30Ω のときに、ステップ波形も繰り返し波形もほぼ波形乱れがなくなります。

理想的には、途中で分岐せずに、図8 に示すように、ドライバの出力から 1対2 となるように送ります。ダンピング抵抗を含めたドライバの駆動能力は、1対1 のときより大きく選びます。

例えば、特性インピーダンスが 50Ω の 1対1 伝送のときに、12mA ドライバに、18Ω のダンピング抵抗を追加すると、オーバシュートが 10% になります。ダンピング抵抗の求め方は、『もっと簡単に決めるダンピング抵抗の値』を参考にしてください。

図8 の場合には、ダンピング抵抗を 0(ゼロ)にします。12mA ドライバの出力抵抗は 22Ω、特性インピーダンスは、50Ω の 2本並列で 25Ω なので、オーバシュートは 6% 程度となります。

途中からの分岐、ドライバの出力からの分岐、いずれの場合も、分岐後の配線長(厳密には遅延時間 脚注1)を等しくする必要があります。いわゆる等長(厳密には等遅延)配線です。

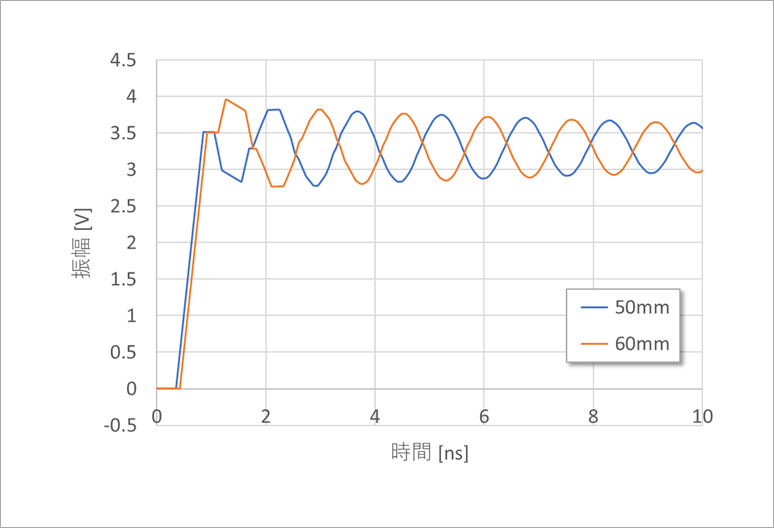

図9 に、図8 の等遅延が守れなかった場合の波形を示します。2本の線路長が 50mm と 60mm の場合です。多重反射を繰り返し、反射がいつまでも収束しません。

(1) の例-2 クロック信号の分配

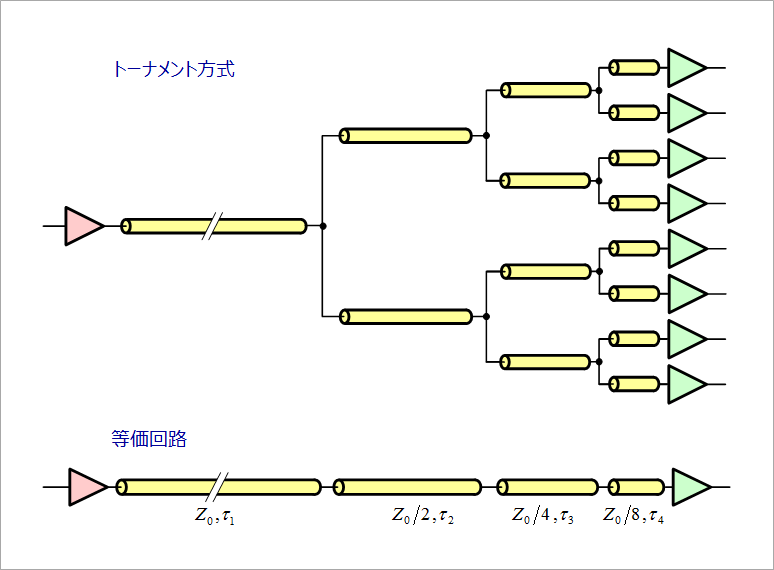

ある程度の波形の乱れを許容するなら、図10 に示すように、1対2、2対4、4対8 のように段階的に分配する方式が以前から用いられてきました。時計回りに 90度回転させると、高校野球のトーナメントのような形になるので、トーナメント方式といいます。DDR2 までのメモリのクロック分配もこの方式です。

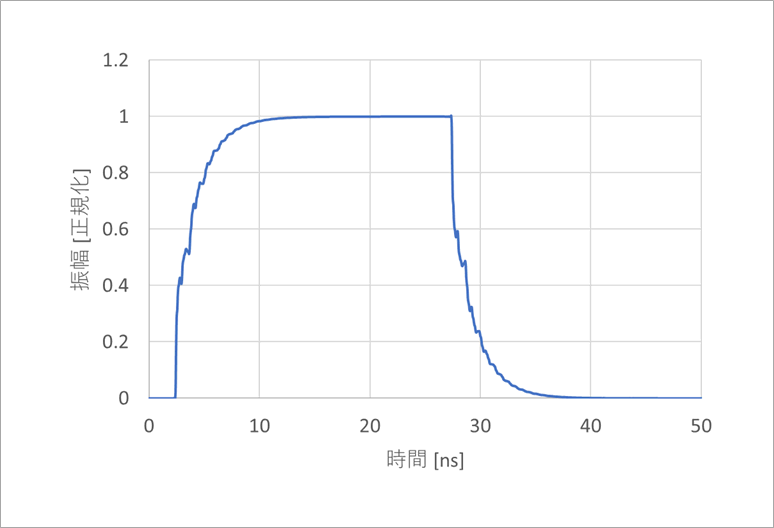

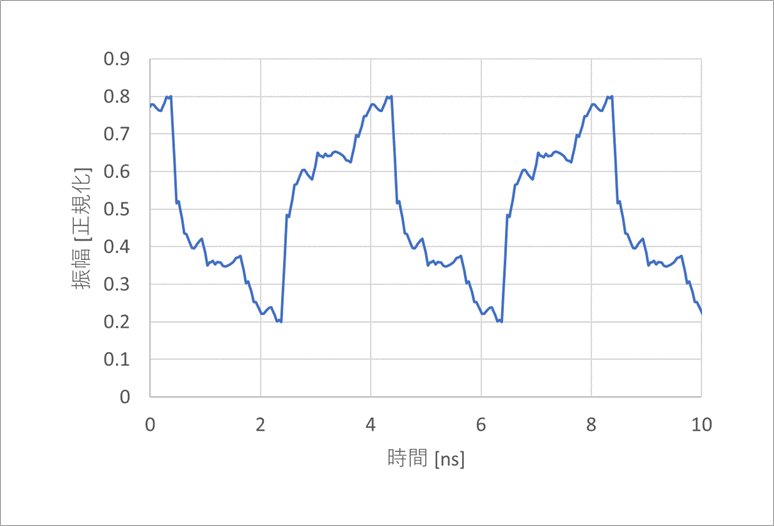

また、LSI 内部は、一般に反射を考慮しないので、このクロック分配が用いられています。例-1 では、並列接続により、特性インピーダンスが 50Ω から 25Ω に変化しましたが、3段階に分岐すると、等価的に、50Ω、25Ω、12.5Ω、6.25Ω と変化するので、波形は大きく乱れます。図11 がパルス幅が広い場合で、図12 が狭い場合です。反射の繰り返しで、振幅も確保できません。

(2) バス接続(メモリモジュール)

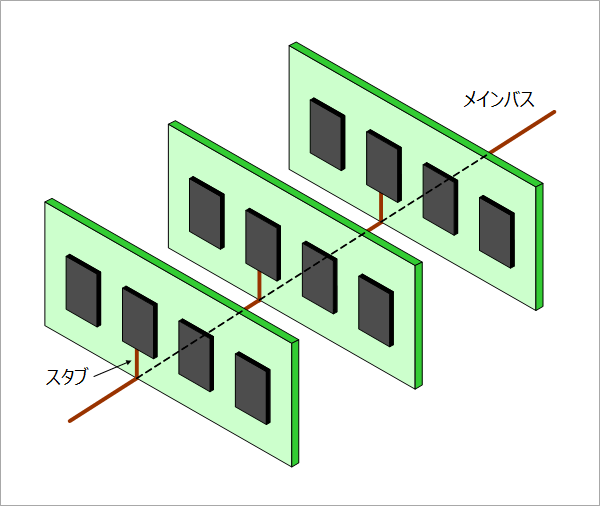

メモリモジュールは、図13 に示すように、マザーポード上のバス配線から、短い配線でメモリモジュール上のメモリ素子に接続します。この接続は、メモリとの接続部がスタブとなって、多重反射を繰り返します。この反射を回避するために、バス配線とスタブとの接続部に抵抗を挿入します。この方式を、スタブ直列終端方式(SSTL:Stub Series Termination Logic)といいます。詳しくは、『豆知識:SSTL~その1』および『豆知識:SSTL~その2』を参照ください。

(3) 意図しない分岐

設計者が分岐とは意識してない分岐です。

例えば、『終端抵抗とは?~その3』の 図1 のように、終端抵抗を接続したときの例です。終端抵抗は、最遠端に接続する必要がありますが、IC のパッケージサイズが大きいと、終端の場所と最遠端のダイの入力までの配線がスタブとなります。解決策などについては、上記コラムを参照ください。

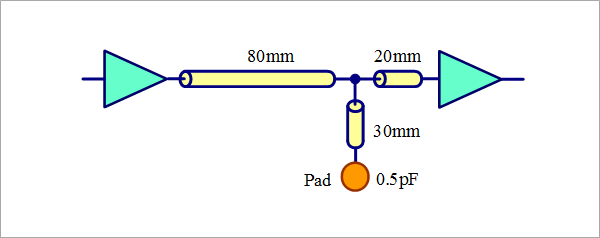

IC パッケージが大きくなり、特に、BGA の場合には、IC のピンの波形を観測することが難しくなりました。そのため、観測したいパターンの途中から、図14 のように、配線を引っ張り出して観測用のパッドを設けることがあります。

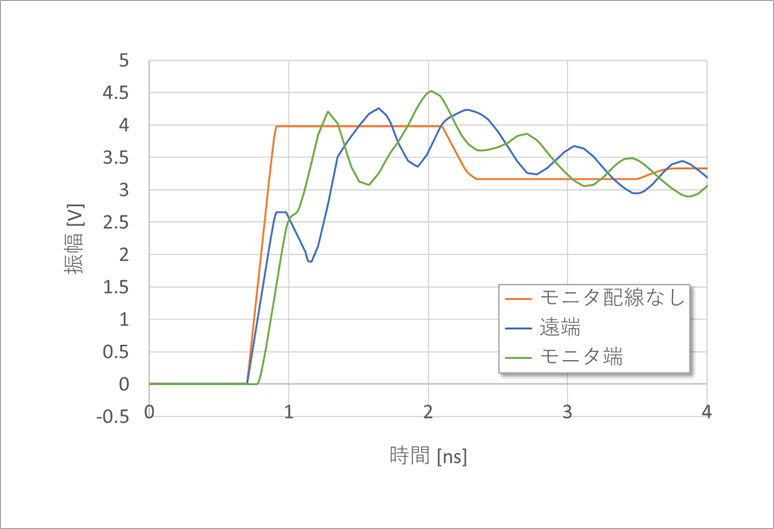

図15 は、この観測用配線の影響を示します。影響を顕在化させるために、信号の立ち上がりを 200ps とし、この観測用の配線を長めの 3cm としましたが、高速信号の場合には、観測用に余分な配線を追加することは避ける必要があります。必要があればシミュレーションを併用してください。

脚注1

プリント配線板のパターンの遅延時間は、表面層と中間層とで異なります。表面層は、6.5ns/m 程度、中間層は、7.3ns/m 程度です。

碓井有三のスペシャリストコラムとは?

基礎の基礎といったレベルから入って、いまさら聞けないようなテーマや初心者向けのテーマ、さらには少し高級なレベルまでを含め、できる限り分かりやすく噛み砕いて述べている連載コラムです。

もしかしたら、他にも気になるテーマがあるかも知れませんよ!