VIH は入力電圧がこの値以上になるとハイと認識する電圧、VIL はこの値以下をローと認識する電圧です。VOH と VOL は出力電圧のハイとローであることは、あえて述べるまでもありません。

ロジック IC の特性

現在のほとんどのロジック IC は CMOS ですが、CMOS の前は TTL でした。この CMOS と TTL とで、特に出力電圧の VOH と VOL の意味と位置づけが異なるので、CMOS 世代の方にはなぜこんな値に規定されているのか疑問に思うことがあると思います。

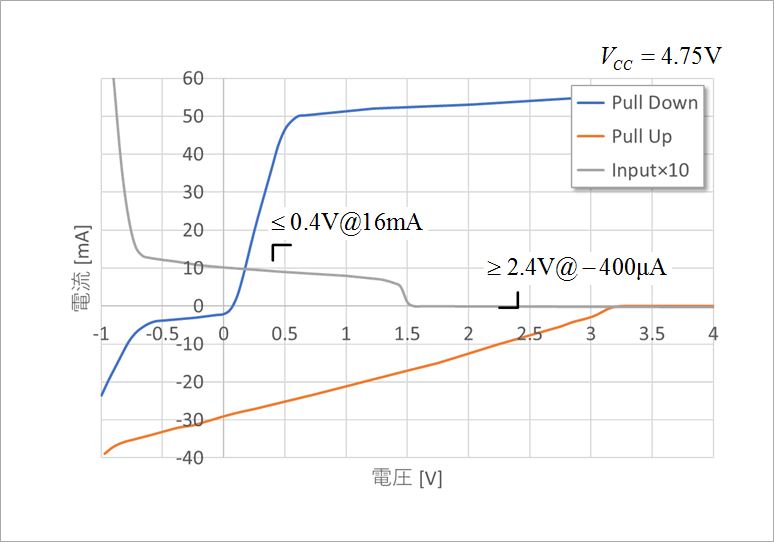

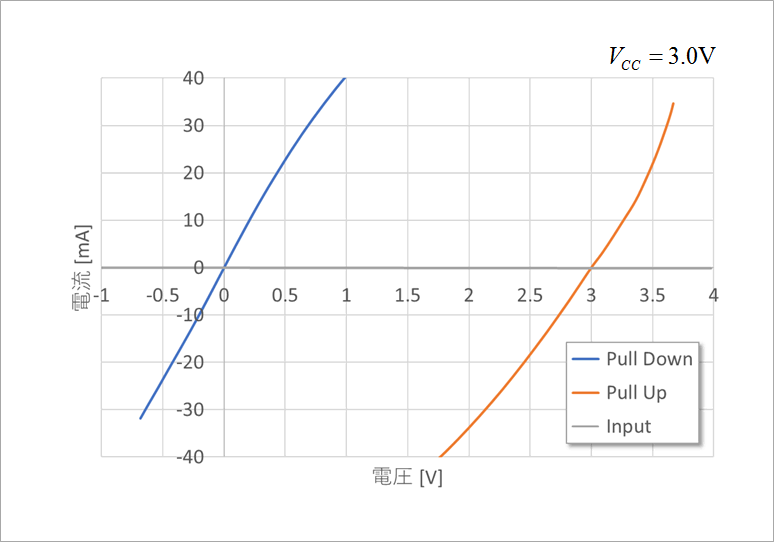

図1 と 図2 に、TTL と CMOS の入出力の静特性を示します。図1 は第1世代の 7400 で、図2 は典型的な 16mA ドライバの CMOS の入出力特性です。図1 と 図2 において、Pull Down はロー側の特性、Pull Up はハイ側の特性です。一般的に、これらの特性は ibis から求めることができますが、TTL の時代にはまだ ibis が登場してなかったので、TTL の ibis は入手することができません。(新しいシリーズの 74F や 74AS は入手が可能です。)

入力特性については詳細を後述しますが、TTL は 10個分の特性を 図1 に示します。CMOS は入力電流がほぼゼロなので、横軸に重なっています。(太い横軸に見えるのは、電流がほぼゼロの直線です。)

入出力レベル

TTL 時代に決められた入出力のレベルは、

- VIH/VIL=2.0V/0.8V

- VOH/VOL=2.4V/0.4V

で、どちらも 0.4V のマージンがあります。この 0.4V は DC のマージンで、これにグラウンドノイズや電源ノイズ、クロストークノイズなどのノイズを考慮する、すなわちノイズバジェットを設定していきます。

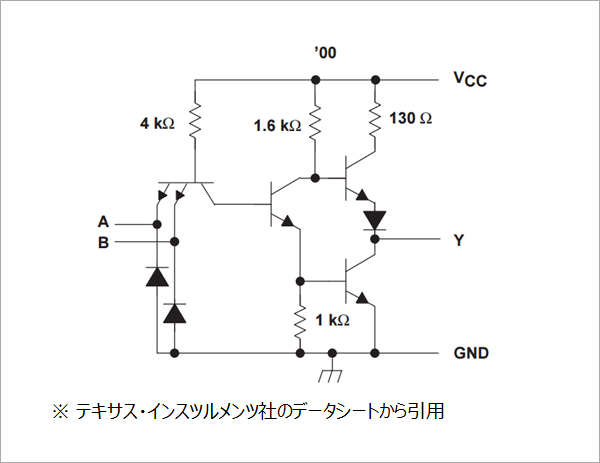

図3 は、SN74 シリーズの最も基本的な NAND ゲート、SN7400 の回路図です。前段がローのとき、入力は VCC から 4kΩ、さらにベース-エミッタを経由して前段の出力に電流が流れ込みます。この電流は、IIL≧-1.6mA@0.4V です(絶対値が 1.6mA 以下)。したがって、1つの出力に 10個の入力が接続されると、16mA が出力に流れ込みます。

図1 の TTL の静特性は、10個の入力の静特性を示しています。すなわち、ロー側の特性では 16mA を流し込んだときに、VOL が 0.4V 以下です。このことを、入力のファン・インが 1、出力のファン・アウトが 10 といいます。

TTL の VIH と VIL は、2.0V と 0.8Vです。この値は、図3 に示す回路図から求まります。

TTL の出力電圧

TTL

| 条件 | VCC | min | typ | max | 単位 | |

| VOL | IOL=16mA | 4.75V | 0.2 | 0.4 | V | |

| VOH | IOH= -400uA | 2.4 | 3.4 | V |

CMOS

| 条件 | VCC | min | typ | max | 単位 | |

| VOL | IOL=16mA | 3.0V | 0.25 | 0.4 | V | |

| VOH | IOH= -16mA | 2.6 | 3.05 | V |

表1 TTL と CMOS の出力電圧

表1 は、TTL と CMOS の出力電圧の規格です。TTL に関しては、ほぼ 1種類(脚注1)に規格化されていましたが、CMOS については電源電圧と出力電流に大きなバリエーションがあるので、筆者が勝手に決めた規格です。CMOS の電源電圧は、5V、3.3V、2.5V、1.8V のように広い電圧のバリエーションがあり、出力電流は 1mA 以下から 24mA 程度まで多岐にわたっています。

いずれも、出力電圧を規定するときの電源電圧は、使用条件の最小値を用います。すなわち、VCC=5V の規格だと -5% の VCC=4.75V で、VCC=3.3V の場合、VCC=3.0V で規定します。

なお、TTL のようなバイポーラの IC の電源電圧を VCC、CMOS の場合には VDDということが多いですが、VCC はトランジスタのコレクタ側に接続する電圧、VDD は同じくドレイン側に接続する電圧という意味で使い分けているようです。過去にも、例えばベースに供給する電圧を VBB、エミッタ側を VEE などと区別することがありましたが、現在のロジック IC は単一電源なので、VCC と VDD を区別する必要はないと筆者は考えています。

TTL は、TI (Texas Instruments) が 1960年代に発表した 74 シリーズが 20年以上、業界標準として使用されてきました。主に、NAND などの基本ゲートを複数個組み合わせて論理を組んでいました。したがって、一つのゲートの出力が、次段のゲートに入力に接続されます。この個数には制限があって、SN74 シリーズの IC の場合には、最大 10個と決まっていました。

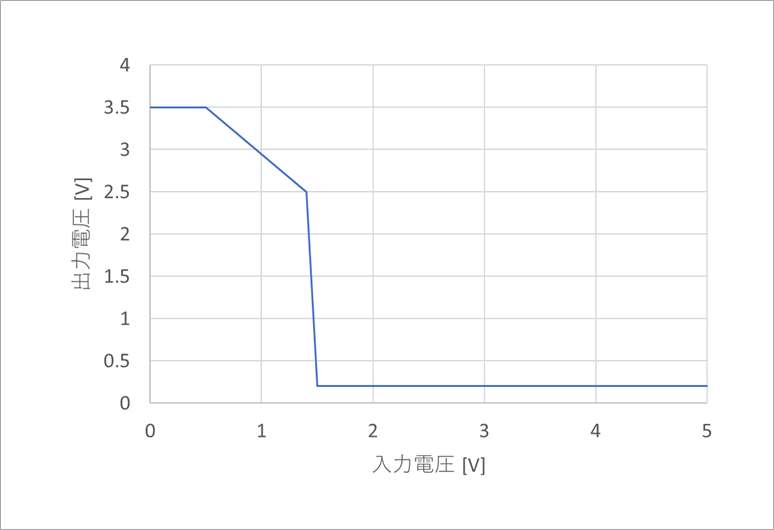

ハイ側は入力 1端子の電流が 40uA なので、10個で 400uA です。ハイ側の出力特性と比べると、かなり余裕があります。ただし、TTL の入出力の伝達特性が 図4 に示すように、入力電圧 VIL が最大値の 0.8V 付近になると、出力電圧の VOH が低下するので、注意が必要です。

CMOS の出力電圧

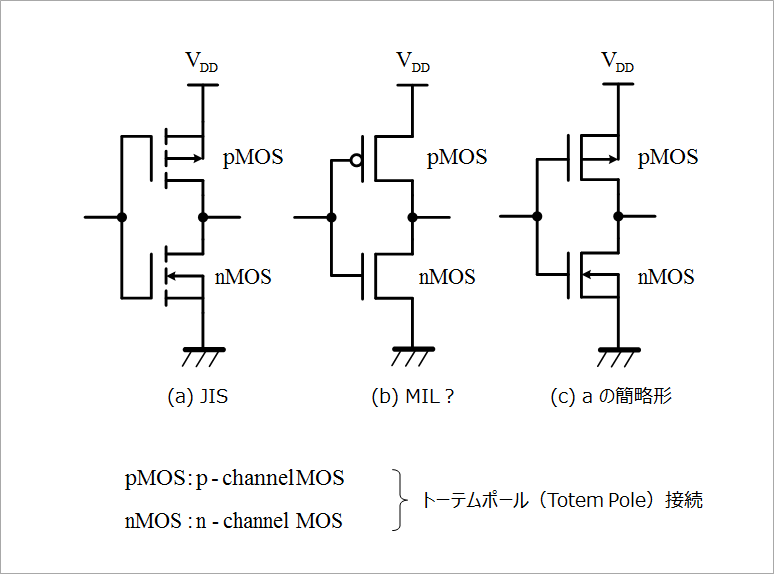

図5 は、CMOS の回路図です。p チャネル MOS (pMOS) と n チャネル MOS (nMOS) が上下にに重なった形です。アメリカ先住民が用いている彫刻のトーテムポールに形が似ているために、トーテムポール回路と呼ばれています。CMOS の入力スレッショールド電圧は、pMOS と nMOS、それぞれのスレッショールド電圧の綱引きで決まるので、回路図からは求まりません。一般的に、CMOS のスレッショールド電圧は電源電圧の 30~70% と言われています。3.3V 電圧の場合には、VIL=1V、VIH=2V 程度です。

CMOS の場合には、入力電流はほぼゼロなので、何個接続されても、直流的には出力電圧が変化することはありません。また、複数個接続することもあまりありません。

それでは、16mA ドライバとはどういう意味があるか考えてみます。先に述べたように、TTL は論理を組むために用いていました。当時の出力電圧の立ち上がり時間が遅く、通常は、反射を考えることはほとんどありませんでした。ロジック IC が TTL から CMOS に切り換わった時期には、個別の IC で論理を組むことはほとんどなくなり、1対1伝送で立ち上がり時間も速くなったので、IC 間を接続する際の反射を考慮する必要が生じてきました。この反射を解析する際に、出力の駆動能力が必要となります。

図2 を見ると、ロー側(Pull Down)もハイ側(Pull Up)も特性はほぼ直線です。表1 の規格を見ると、16mA のときに 0.4V なので、出力特性の傾き(の逆数))は、400mV/16mA=25Ω となりますが、この 400mV は製造プロセス、温度を含めた最悪値で、標準的な特性は、この 1/1.5 程度で 16Ω になります。

図1 から、TTL の無負荷時の VOH と VOL は 3.2V と 0.1V 程度です。一方、図2 から CMOS の無負荷時の VOH と VOL は 3.0V と 0V、すなわち電源電圧一杯です。アナログでは、rail-to-rail といいます。CMOS の場合には、VOL が 0.4V 以外のものも多く見られます。これは、前述のように、0.4V という値そのものに意味はなく(脚注2)、出力抵抗を規定している意味が強いので、0.2V でも 0.5V でもいいわけです。電圧と電流から求めた抵抗が非常に大きい場合には、出力特性の非線形の領域が動作範囲に入ってくることがあるので、反射の解析には注意が必要です。必要に応じて、Bergeron 解析を用いてください。

ibis の活用

74 シリーズの規格に対して、74L、74H、74LS、74S、さらには、74F、74AS、74ALS といったバリエーションが誕生し、規格自体(主に IOL と IOH)も異なります。

脚注2

TTL と CMOS の混在のときには意味がありました。

碓井有三のスペシャリストコラムとは?

基礎の基礎といったレベルから入って、いまさら聞けないようなテーマや初心者向けのテーマ、さらには少し高級なレベルまでを含め、できる限り分かりやすく噛み砕いて述べている連載コラムです。

もしかしたら、他にも気になるテーマがあるかも知れませんよ!