SSTL とは Stub Series Termination Logic の略です。Stub(スタブ)とは木の切り株といった意味があり、メモリの配線ではメインのバスに対して、DIMM (Dual-In-Line Memory Module) に入っていく支線を意味します。

分布定数回路を伝わる信号は、特性インピーダンスが不連続に変化する点で反射が生じて波形が乱れるので、このスタブにおける特性インピーダンスの不連続に対する対策が必要となります。

スタブの先にはメモリ素子のデータの I/O 端子が接続されています。この端子は終端されていません。短い、いわゆる開放線路です。

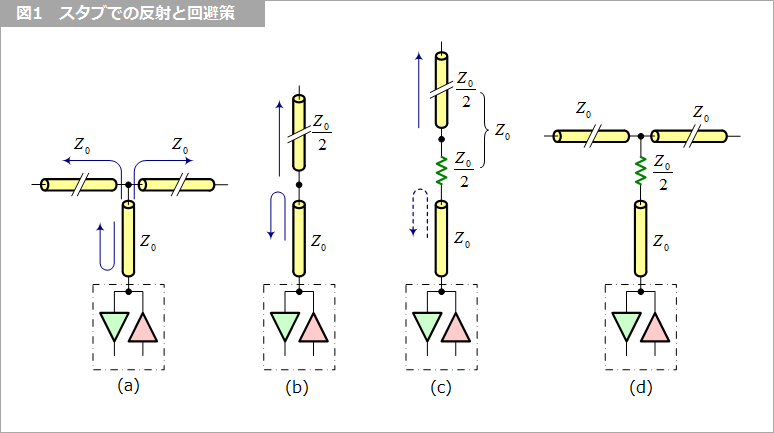

図1 の (a) に示すように、メイン のバスからスタブに入った信号は、メモリ素子の I/O 端子で反射します。開放線路なので、100 % 反射します。

反射した信号はメインのバスに戻ろうとしますが、スタブから見たバスは左右にわかれているので、同図 (b) に示すようにバスの特性インピーダンスは半分となり、すんなりと出ていけずに、再度 I/O 端子に戻って多重反射(反射の繰り返し)となります。

スタブから見たメインのバスは特性インピーダンス Zo の半分、すなわち Zo/2 と見えるので、同図 (c) のようにバスの根本に Zo/2 の直列抵抗を挿入すると、スタブから見たバスは Zo となってインピーダンスの非整合が解消されます。

この抵抗をスタブに直列に入れる意味で、Stub Series Termination といいます。

メモリ素子のデータ端子は I/O コモンです。メモリに対して書き込み(Write)のときには入力として働き、読み出し(Read)のときには出力として働きます。入力はトランジスタサイズも小さいので静電容量も小さいのですが、出力は線路を駆動するためにトランジスタサイズが大きく、静電容量が大きくなります。

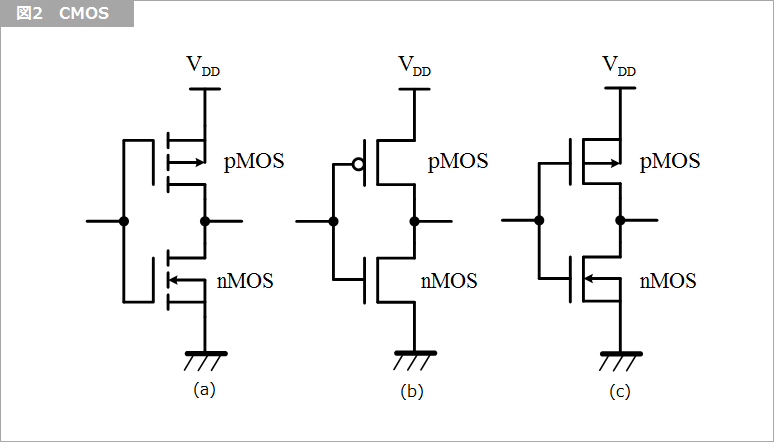

CMOS の "C" は Complementary(相補)の略で、図2 に示すように、pMOS と nMOS とが上下に積み重なった形をしています。この積み重ねの回路が、アメリカ先住民が記念碑や墓標として建てた柱状の木の彫刻に似ているので、トーテムポール回路またはトーテムポール出力といいます。

CMOS については、『同時スイッチングノイズ』を参照ください。

pMOS は nMOS に比べて半導体の移動度が小さく、トランジスタサイズを大きくとる必要があり、物理的形状が大きくなることが、CMOS の出力回路の静電容量が大きな理由です。

SSTL が採用された当初は、I/O 端子の容量は 7 pF もありました。

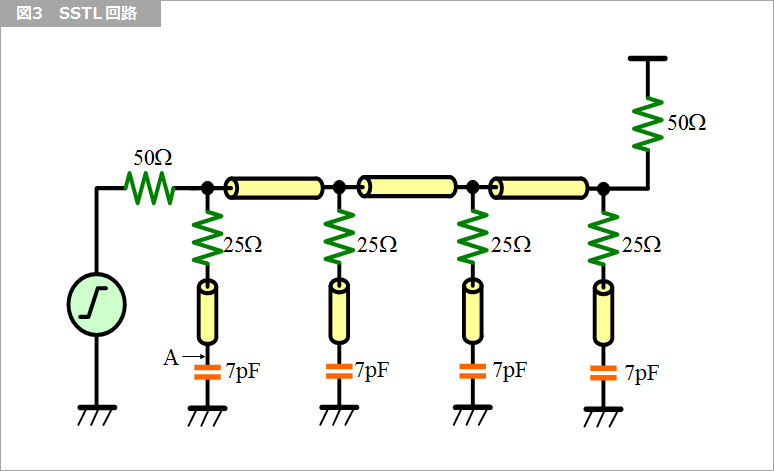

図3 は SSTL の回路例です。

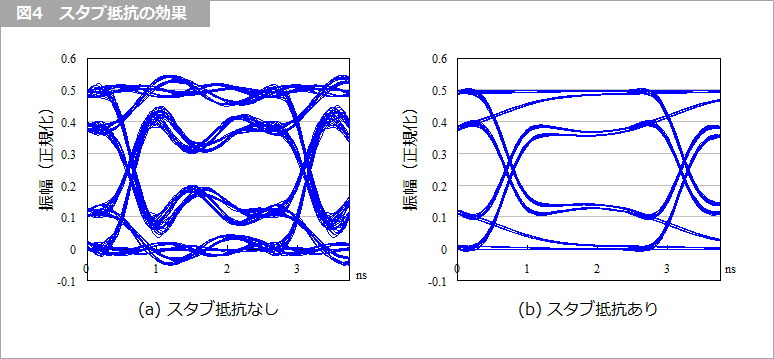

図3 の Write 時の A 点の波形を解析した結果を 図4 に示します。スタブ抵抗の有無により波形乱れが大きく改善されているのがわかります。

『豆知識:SSTL~その2』もご覧ください。

メモリバスはその後少しずつ改良されていきますが、機会があったらまた説明します。

おすすめ記事/資料はこちら

======================================

碓井有三のスペシャリストコラムとは?

基礎の基礎といったレベルから入って、いまさら聞けないようなテーマや初心者向けのテーマ、さらには少し高級なレベルまでを含め、できる限り分かりやすく噛み砕いて述べている連載コラムです。

もしかしたら、他にも気になるテーマがあるかも知れませんよ!

こちら から他のテーマのコラムも覗いてみてください。