『バス伝送~その1』で述べた、小振幅バスの代表であるラムバスについて解説します。これは、メモリのバスとして開発されました。

ラムバス

ラムバス(Rambus)は、ラムバス社の開発したバス伝送方式です。ラムバスは、ベース型およびこの後継のコンカレント型からスタートしました。これらはいずれも 9ビット幅でした。

これらと区別して、現在のラムバスはダイレクト・ラムバスといいます。

ダイレクト・ラムバス(以下、簡単にラムバスといいます)の開発当初は、2バイト(16ビット)幅で、400 MHz のクロックの立ち上がりと立ち下がりとで転送される、いわゆるダブル・データレート方式なので、1600 MB/s の転送速度を有する、当時としては画期的な方式でした。

ラムバスの特徴

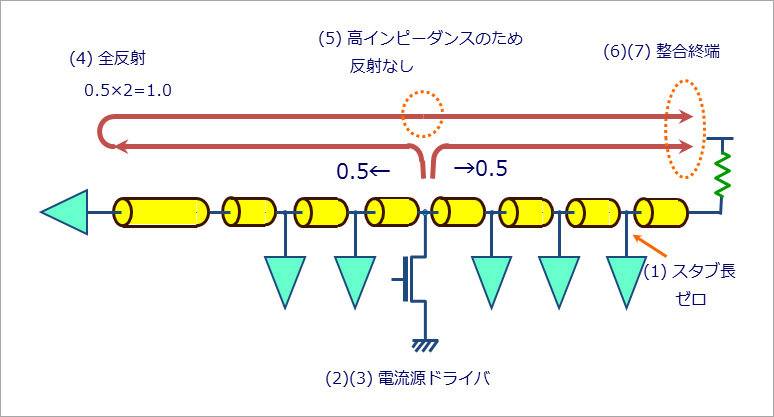

図1 はダイレクト・ラムバスの動作原理で、この図をもとにその特徴を列挙します。

(1)スタブ長ゼロ

バス上にチップを直接接続するために、バスとメモリとを接続するための配線によるスタブが存在しない。

(2)電流源ドライバ

ドライバは、N チャネルトランジスタのオープン・ドレイン形式なので、出力容量が小さい。 (脚注1)

(3)電流源ドライバ

電流源ドライバなので、出力インピーダンスは無限大 (開放) である。

(4)全反射

例えば、メモリからチップセットへの伝送では、メモリから見ると、左右に信号が分かれるため、振幅は半分になるが、チップセット側か開放であるため、オープン反射により倍の振幅となって、結局、所期の振幅を得ることが出来る。

(5)高インピーダンス

チップセット側でオープン反射した信号は、ふたたびドライバ側に戻るが、(3) で述べたように、ドライバは開放のため、ドライバを通過する際に反射しない。

(6)整合終端のため反射なし

ドライバを通過した信号は、反対側に設けられた終端抵抗で吸収される。

(7)整合終端のため反射なし

終端の場所では、最初にチップセットとは反対に進んだ信号が終端抵抗により吸収され、(5) の反射による信号とあわせて、ここの場所の波形はきれいではない。 ただし、ここの信号は不必要なので、汚くても問題がない。

ラムバスは上述の特徴のほかに、数々の新技術を採用して、その後の SDRAM(Synchronous Dynamic RAM)の発展にも大きく寄与し続けています。

ラムバスの欠点

シグナル・インテグリティ的には極めて高度な優れた技術を開発しましたが、PC のメインメモリに採用するには致命的な欠点があり、PC のメインメモリの地位は築けませんでした。

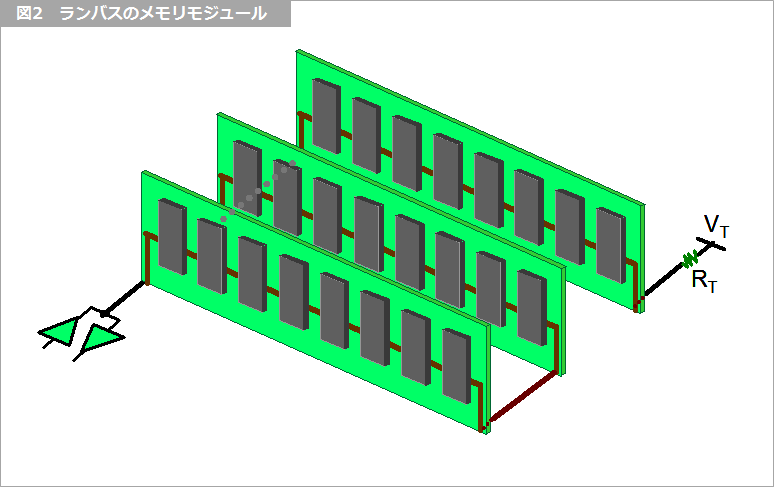

その理由は、図2 に示すラムバスのメモリモジュールをながめて皆さんで考えてください。 答えは文末に記載します。

SSTL

ラムバスに対抗する形で開発されたメモリバスが SDRAM に適用された SSTL(Series Stub Termination Logic)です。

SSTL の詳細については、本コラムの『豆知識:SSTL~その1』および『豆知識:SSTL~その2』を参照ください。

<span="bold">脚注1

通常の CMOS 出力は、pMOS と nMOS の 1組のトランジスタが上下に積み重ねられた構造です(『同時スイッチングノイズ』の 図1を参照下さい)。

一般的に、pMOS のトランジスタサイズは nMOS の 3倍程度なので、nMOS 換算で 4個のトランジスタ相当の容量になります。一方ラムバスは nMOS トランジスタが 1個なので、出力回路の容量は CMOS の 1/4 程度になります。

<span="bold">答え

メモリ・バスはバス配線がモジュール内を通る構造なので、メモリの増設ができません。当初からフル実装するか、メモリ素子の搭載されてないメモリモジュールを実装する必要があるため、メモリ増設を行う PC には不向きでした。ただし、メモリを増設しないゲーム機などでは、狭いバス幅と高速転送の利点を活かして、現在でも多用されています。

碓井有三のスペシャリストコラムとは?

基礎の基礎といったレベルから入って、いまさら聞けないようなテーマや初心者向けのテーマ、さらには少し高級なレベルまでを含め、できる限り分かりやすく噛み砕いて述べている連載コラムです。

もしかしたら、他にも気になるテーマがあるかも知れませんよ!