論理回路は基本的に、2つの(まれには多値)のレベルを切り換えて状態を表します。代表的な CMOS (Complementary Metal Oxide Semiconductor) の場合には、電源電圧とグラウンド電圧(0 ボルト)のレベルを論理 "1" と "0" とに割り当てます。

電源電圧は、以前は 5 V が標準でした。1960 年代に DTL (Diode Transister Logic) や TTL (Transistor Transistor Logic) からスタートして、現在でも 5 V ロジックは残っています。これらのバイポーラ(Bipolar)素子は、電源電圧とグラウンド電圧一杯までは振幅がとれずに、5 V 電圧でも論理振幅は 3 V 前後でした。その後、CMOS がロジックの中心となって、電源電圧一杯の振幅が得られるようになりました。ロジックの分野ではあまり使わない用語ですが、アナログの分野では、電源電圧一杯の振幅を得ることを Rail-to-Rail といいます。

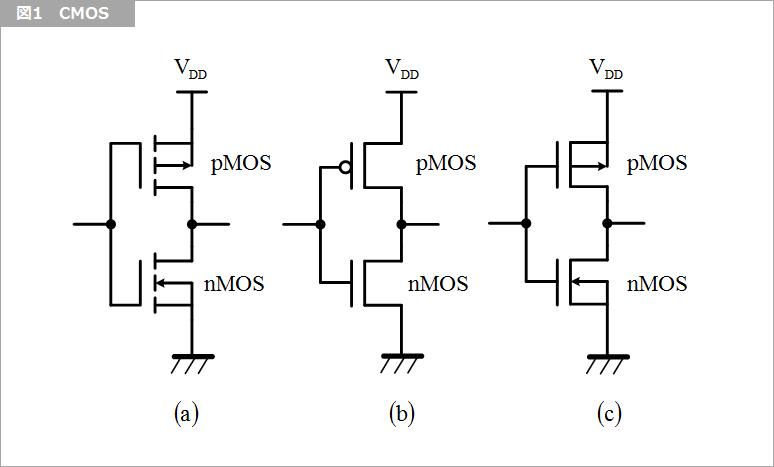

2つの論理レベルを切り換える際には、電流変化が生じます。1つには、CMOS のいわゆる貫通電流と言われるものです。CMOS は図1 に示すように、pMOS (p-channel MOS) と nMOS (n-channel MOS) とが上下に重なったトーテムポールと言われる回路構成をとっています。

余談ですが、CMOS の回路図の書き方は、同図の (a)、(b) または (c) のいずれもがよく用いられています。(a) は JIS で規定された書き方で、厳密にはエンハンスメント型(脚注1)の MOS の回路図です。CMOS にはエンハンスメント型の MOS が用いられます。(b) は MIL で規定された書き方だったと記憶しています。(c) は、(a) の簡略形で手書きでよく用いられるようです。(脚注2)

CMOS ゲートは、pMOS が導通したときには nMOS は非導通、その逆に、nMOS が導通したときには pMOS は非導通という、pMOS と nMOS とが互いに相補(Complementary)の関係にあります。CMOS の名前もこれに起因しています。この回路の入力スレッショールド電圧は、pMOS と nMOS それぞれのスレッショールド電圧がバランスすることにより決まります。

入力のスレッショールド電圧付近では、pMOS と nMOS とが完全に導通あるいは非導通の状態ではない半分導通、または瞬間的には両方とも導通する状態が存在します。この状態に、電源から pMOS と nMOS とを経由して、グラウンドに向かって大きな電流が流れます。この電流のことを貫通電流といいます。この他には、出力に接続された容量(キャパシタ)を充放電する際にも電流が流れます。

LSI の出力に接続された素子の場合には、出力から配線に流れる電流も存在します。出力が変化する瞬間は、出力配線は特性インピーダンスの純抵抗が接続されていることと等価です。『特性インピーダンスって何?』も参照下さい。

論理が変化するゲートの数が少ない場合には、この電流変化はそれほど大きな意味を持ちませんが、同時に変化するゲートの数が増えてくると、その電流のピークが重なり、大きな電流変化となります。この電流変化により、LSI 内部のグラウンド面に存在する抵抗分やインダクタンス分により、グラウンドレベルが変化します。グラウンドに流れる電流は、内部電流だけではなくて、配線を駆動する際に流れる電流の戻ってくる電流、すなわち、リターン電流も含みます。グラウンドレベルが変化するということは、このグラウンドレベルを基準にしている内部ゲートは、入力レベルが変化することと等価な動きをします。

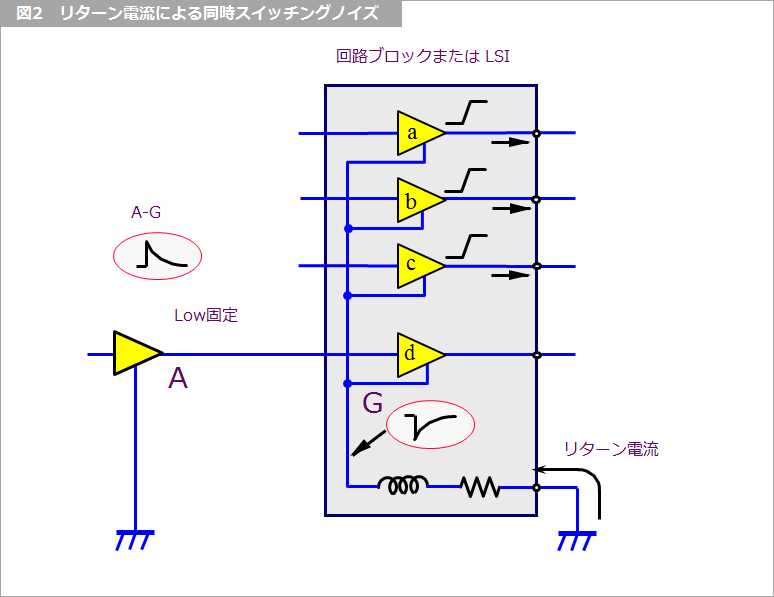

図2 にリターン電流による同時スイッチングノイズが現れる原理を示します。

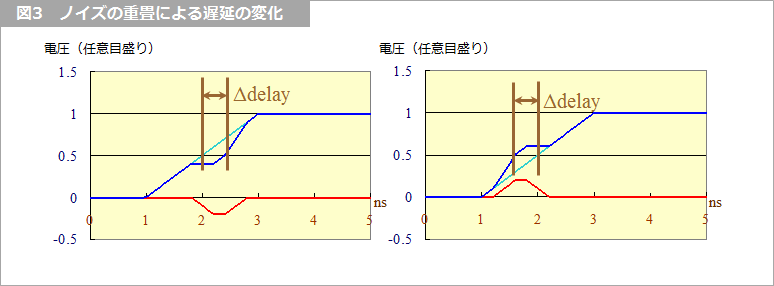

四角で囲んだ部分を、回路ブロックまたは LSI とします。同図 a~c の 3本の出力ゲートから外部に電流が流れ出る際に、線路を駆動する電流は、1出力あたり数十 mA となります。3本の出力に対して、リターンが 1本とすると、リターンには 1出力あたりの電流の 3倍のリターン電流が帰ってきます。この電流が、抵抗やインダクタを経由して内部に戻るので、内部のグラウンドは同図に示すように、電圧が瞬間的に低下します。同図のゲート d の基準電圧(グラウンド)は同図 G のように電圧が低下するので、この回路ブロックまたは LSI の外の Low レベルの論理を受けていたゲート d の入力電圧は、等価的に A-G となります。A-G は、誤動作に至るほどの振幅になることは少ないですが、ゲート d の入力信号の立ち上がりや立ち下がりにこのノイズが重なると、遅延時間が変化します。速くなっても遅くなっても、セットアップ時間やホールド時間が確保できなくなり、誤動作に至ることがあります。

同時スイッチングノイズの対策としては、同時に動作する信号数を制限するとか、意識的にタイミングをずらす方法が取られます。信号に対するリターンの本数を十分確保することも重要です。可能ならば、信号の立ち上がり(立ち下がり)時間を遅く制御することも非常に有効です。(脚注3)

脚注1

エンハンスメント型 MOS とは、ゲート電圧(ソースに対する電圧なので VGS という)がゼロのときにドレイン電流が流れないものをいいます。これに対して、ゲート電圧がゼロのときにもドレイン電流が流れるものをディプレッション型といいます。すなわち、ディプレッション型では、ドレイン電流をゼロにするためには、ゲート電圧を逆方向(nMOSなら負、pMOSなら正)にする必要があります。

脚注2

図1 の (a) と (c) において、矢印によって、サブストレートとソースとを接続していますが、ロジック回路においては、この接続は必ずしも意識する必要はないので、省略する書き方も多用されています。

脚注3

アルテラ社のデバイスでは、Quartus II 開発ソフトウェアの設定で出力ピン、双方向ピンの立ち上がり(立ち下がり)時間を調整することが可能です。”Slow Slew Rate” や ”Slew Rate” で設定します。

使用するデバイスにより項目が異なりますので、詳細については、『Quartus はじめてガイド - よく使用するピン・オプションの設定方法』 の ”Slow Slew Rate” や ”Slew Rate” 項目をご参照ください。

碓井有三のスペシャリストコラムとは?

基礎の基礎といったレベルから入って、いまさら聞けないようなテーマや初心者向けのテーマ、さらには少し高級なレベルまでを含め、できる限り分かりやすく噛み砕いて述べている連載コラムです。

もしかしたら、他にも気になるテーマがあるかも知れませんよ!