旧タイトル『DS-5 活用テクニック~レジスタ・ビュー[3/3]FPGA 側のレジスタ表示』のアップデート版です。

インテル® SoC FPGA 向けのソフトウェア統合開発環境として標準採用される Arm 純正ツールが Arm® DS-5 for Intel® SoC FPGA Edition (DS-5) から Arm® Development Studio for Intel® SoC FPGA Edition (Arm® DS) へと変更になりました。Arm® DS は DS-5 の後継製品となっており使い勝手は大きくは変わりません。このシリーズ記事の内容も Arm® DS / DS-5 両方に適用できるものが大半ですが、違いがある箇所はその旨明記する形でアップデートしています。

***

この記事では、インテル® SoC FPGA 向けのソフトウェア統合開発環境として利用可能な Arm® DS / DS-5 の使い方に関する補足情報を記載します。

インテル® SoC FPGA 向けの Arm® DS / DS-5 は「インテル® SoC FPGA エディション」という製品になります。インテル® SoC FPGA エディションと Arm® 純正エディションの違いは、サポートする接続対象デバイスくらいで、デバッガや付属のツール(コンパイラー/リンカーなど)の使い方自体に違いはありません。そのため、基本的には Arm® 社が公開している Arm® DS / DS-5 のマニュアル類を参照することで、一通りの使い方が理解できるようになっています。

Arm® Development Studio ドキュメント・ページ(Arm® Developer サイト)

DS-5 ドキュメント・ページ(Arm® Developer サイト)

今回は、Arm® DS / DS-5 のレジスタ・ビューに FPGA 側のレジスタを表示させる方法について掲載します。

レジスタ定義ファイルの自動生成

Platform Designer(旧 Qsys )を用いて SoC FPGA 向けのハードウェアデザインを作成した場合、レジスタ定義ファイル(.svd)が自動生成されます。

自動生成される場所

[Quartus Project Directory]/soc_system/synthesis/soc_system_hps_0_hps.svd

上記のレジスタ定義ファイルを、前回の記事に掲載した内容と同じ方法で Arm® DS / DS-5 に読み込ませることで、FPGA 側のレジスタをレジスタ・ビューに表示させることが可能です。(デバッグコンフィグレーションにて ”ディレクトリーからペリフェラル記述ファイルを追加します” を選択)

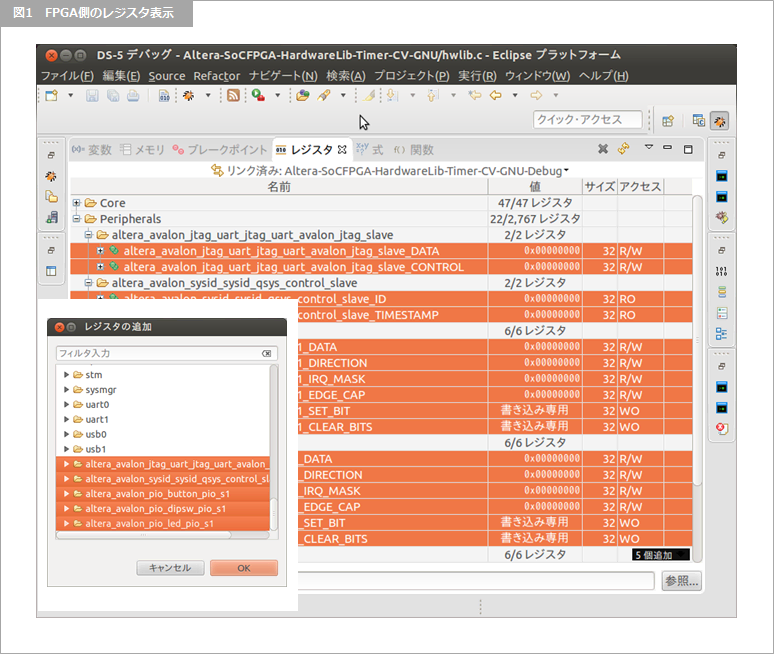

下記は FPGA 側のレジスタが表示されたレジスタ・ビューのイメージです。

ちなみに、自動生成されたレジスタ定義と、前回の記事に掲載したサンプルのレジスタ定義(.tcf)の両方を読み込ませると ”警告 (TAD231):xxxx ” で始まるワーニングメッセージが多数表示されますが、これらは全て無視して大丈夫です。

これらのメッセージは、レジスタ定義ファイルに使っているペリフェラルの名前が重複した場合に表示されるものです。サンプルのレジスタ定義(.tcf)では、初めから定義されているペリフェラル(dmanonsecure、dmasecure、mpul2、mpuscu)に対してレジスタの定義を追加記述するようにしていますが、自動生成されたレジスタ定義(.svd)の中にも同じ名前のペリフェラルが記述されているため、両方のレジスタ定義を読み込んだ場合には重複を警告する振る舞いになるようです。

レジスタ表示に対応した IP コンポーネント

レジスタ定義が自動生成される対象は Platform Designer (旧 Qsys ) 対応 の IP コンポーネントのなかで、レジスタ定義ファイル(CMSIS-SVD)をサポートしているものに限られます。

IP コンポーネントの CMSIS-SVD サポートについては、インテル® Quartus® Prime Software User Guide - Platform Designer のドキュメントに多少の説明がありますが、十分な内容ではないので既存の IP コンポーネントを参考にするのが良さそうです。

参照:インテル® Quartus® Prime Standard Edition User Guide - Platform Designer

参照:インテル® Quartus® Prime Pro Edition User Guide - Platform Designer

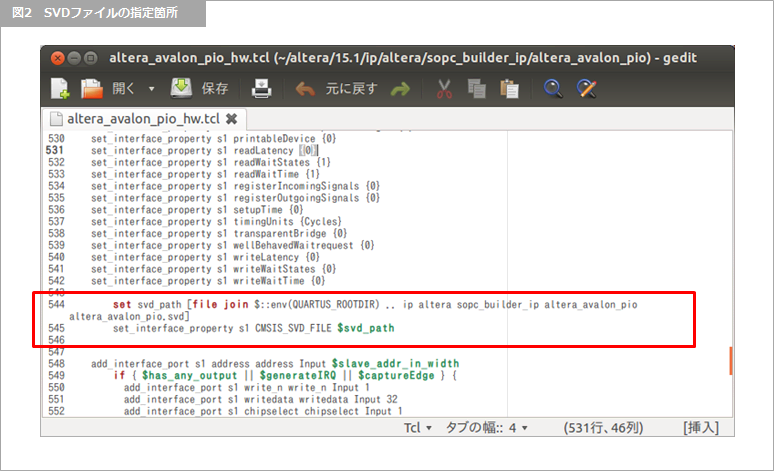

参考までに、CMSIS-SVD をサポートしたIPコンポーネント(PIO)のファイルを確認したところ、_hw.tcl ファイルの中で Interface Property として CMSIS_SVD_FILE をセットしていることが確認できました。

下記イメージの青枠内が該当の記述となります。

CMSIS-SVD サポートの IP コンポーネントを作成したい場合は下記の対応が必要となるようです。

* .svd 形式のレジスタ定義ファイルを用意。

* _hw.tcl に set_interface_property で CMSIS_SVD_FILE を指定する記述を行う。

インテル® SoCFPGA 関連の情報を配信しているコミュニティーサイト(Rocketboards.org)に

より詳細な情報が掲載されているので、下記リンク先のドキュメントページも参考にしてください。

レジスタ・ビューに対応していないレジスタの参照

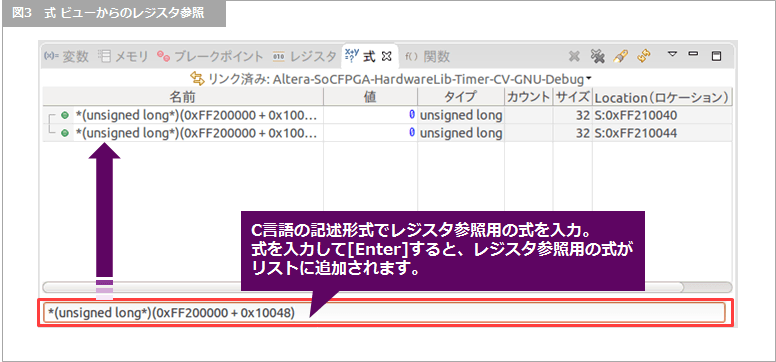

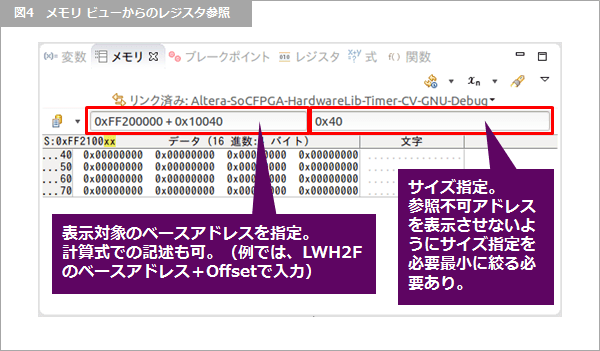

レジスタ定義を追加せずに所望のレジスタを参照する方法についても触れておきます。レジスタ・ビュー以外に下記のウィンドウを使ってレジスタの参照を行うことも可能です。

* 式 ビュー

* メモリ・ビュー

以下、各ビューでのレジスタ参照方法を示したイメージです。

ここまでレジスタ・ビューのカスタマイズ方法について記載してきましたが、レジスタ定義が面倒な場合には、上記のイメージに示した方法でレジスタ参照することになります。

3回に分けて Arm® DS / DS-5 のレジスタ・ビューの使い方について掲載してきましたが、レジスタ・ビューについては今回の記事にて最終回となります。

おすすめ記事/資料はこちら

Arm DS 活用テクニック ~レジスタ・ビュー[1/3]基本設定

Arm DS 活用テクニック ~レジスタ・ビュー[2/3]レジスター定義の自作

Arm DS 活用テクニック ~レジスタ・ビュー[3/3]FPGA 側のレジスター表示

Arm DS 活用に関する記事一覧

SoC FPGA 関連の記事や資料

インテル® FPGA の SoC FPGA

インテル® FPGA の開発フロー/FPGA トップページ