旧タイトル『DS-5 活用テクニック~レジスタ・ビュー[2/3]レジスター定義の自作』のアップデート版です。

インテル® SoC FPGA 向けのソフトウェア統合開発環境として標準採用される Arm 純正ツールが Arm® DS-5 for Intel® SoC FPGA Edition (DS-5) から Arm® Development Studio for Intel® SoC FPGA Edition (Arm® DS) へと変更になりました。Arm® DS は DS-5 の後継製品となっており使い勝手は大きくは変わりません。このシリーズ記事の内容も Arm® DS / DS-5 両方に適用できるものが大半ですが、違いがある箇所はその旨明記する形でアップデートしています。

***

この記事では、インテル® SoC FPGA 向けのソフトウェア統合開発環境として利用可能な Arm® DS / DS-5 の使い方に関する補足情報を記載します。

インテル® SoC FPGA 向けの Arm® DS / DS-5 は「インテル® SoC FPGA エディション」という製品になります。インテル® SoC FPGA エディションと Arm® 純正エディションの違いは、サポートする接続対象デバイスくらいで、デバッガや付属のツール(コンパイラー/リンカーなど)の使い方自体に違いはありません。そのため、基本的には Arm® 社が公開している Arm® DS / DS-5 のマニュアル類を参照することで、一通りの使い方が理解できるようになっています。

Arm® Development Studio ドキュメント・ページ(Arm® Developer サイト)

DS-5 ドキュメント・ページ(Arm® Developer サイト)

今回は、Arm® DS / DS-5 のレジスタ・ビューに新しい表示項目(レジスター定義)を追加する方法について掲載します。

レジスタ表示未対応のペリフェラルについて

Arm® DS / DS-5 のレジスタ・ビューには、HPS Technical Reference Manual に記載される各種ペリフェラルのレジスタが初めから定義されています。前回の記事に記載した表示項目の選択を行うのみでレジスタ表示が可能です。

ただし、Arm® 製の IP を利用して実装されたペリフェラルについては、レジスタの詳細定義が一部行われていないため、レジスタ・ビューによる値の設定/確認が行えないようになっています。

以下のペリフェラルのレジスタ表示に対応していません。

* DMA Controller(DMA-330)

* L2Cache Controller(L2C-310)

* Cortex-A9 MPCore 内蔵 SCU(Snoop Control Unit)

* Cortex-A9 MPCore 内蔵 Interrupt Controller(GIC: PL-390)

* Cortex-A9 MPCore 内蔵 Timer(GlobalTimer, PrivateTimer, WatchdogTimer)

レジスタ・ビューの表示に対応していないペリフェラルについては、レジスタマップ上にもレジスタの詳細仕様は記述されておらず、ベースアドレスと参照すべきドキュメントへのリンクが記載された状態になっています。

レジスタの定義を追加する方法

.svd 形式もしくは .tcf 形式(いずれも XML ベースのファイル形式)でレジスタの定義を記述することで、レジスタ・ビューの表示に対応したレジスタを自由に定義することができます。

初期表示されるレジスタ定義についても Arm® DS / DS-5 のインストールディレクトリー以下に格納されているので、.tcf を記述する際の参考にすることができます。(他のデバイス向けの定義も近くのディレクトリーに格納されています)

[Arm® DS / DS-5 Install Directory]/sw/debugger/configdb/SoCs/altera/hps_svd.tcf

.svd の参考としては、インテル® Quartus® Prime 開発ソフトウェアのインストールディレクトリー以下に .svd 形式のファイルが格納されています。

[インテル® Quartus® Prime Install Directory]/ip/altera/hps/altera_hps/altera_hps.svd

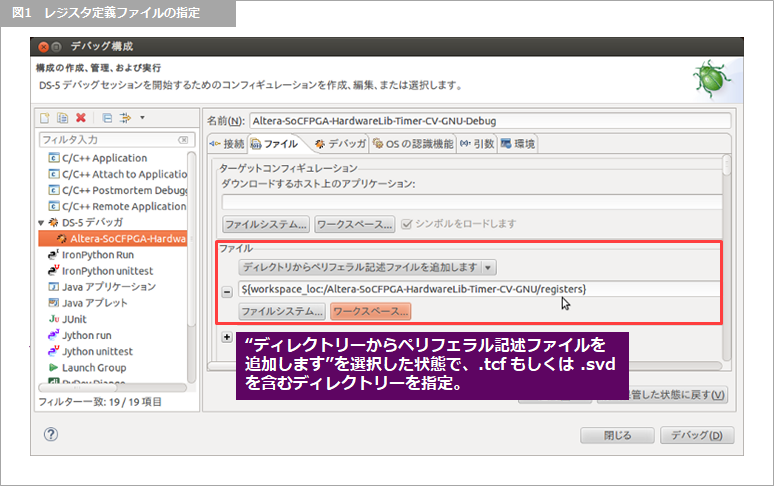

記述したレジスター定義ファイルは、Arm® DS / DS-5 のデバッガー接続設定(デバッグコンフィギュレーション)のファイルタブ上で、"ディレクトリーからペリフェラル記述ファイルを追加します"を選択してファイルの所在を指定することで、デバッガー接続時にレジスター定義が読み込まれるようになります。この指定以外に特別な設定は必要ありません。

下記はレジスター定義ファイルを指定する設定画面のイメージです。

.svd と .tcf の違い

レジスタ定義ファイルの形式は、.tcf と .svd のいずれかを選択する事になります。

.svd については、Cortex Microcontroller Software Interface Standard (CMSIS) という規格の中で、System View Description (SVD) として標準化されています。XMLのフォーマットも CMSIS のドキュメントとして公開されます。

インテル® SoC FPGA エンベデッド開発スイート (SoC EDS) ユーザーガイド にも .svd を利用する方法のみ説明が記載されているので、.svd が推奨のフォーマットとなっているように思われます。(.tcf 形式はユーザーガイドには記載されていません)

参照:Cortex Microcontroller Software Interface Standard (CMSIS)

一方で、Arm® DS / DS-5 の推奨形式は .tcf のようです。

Arm® DS / DS-5 のドキュメントにも、Target Configuration File (TCF) として説明が記載されていて、専用の編集用エディターが用意されているというメリットもあります。

参照:Arm® Development Studio User Guide「Working with the Target Configuration Editor」

参照:Arm® DS-5 Debugger User Guide「Working with the Target Configuration Editor」

尚、.svd 形式で作成されたレジスタ定義であっても、Arm® DS / DS-5 がレジスタ定義ファイルを読み込む際に自動的に .tcf 形式に変換されるようです。結局は自動変換された .tcf が使われることになるので、どちらの形式でレジスタ定義を作成するかは好みで選択すれば良いと思います。

個人的には、.tcf の方がお勧めです。

編集用エディターが用意されているだけでなく、テキストエディターで XML を直接編集する場合でも .tcf のXMLの方が編集し易いタグ構造になっていると感じます。

記述方法(XMLタグ構造)の詳細については、この記事では触れません。既存の定義ファイルやドキュメントを参考にして記述してみてください。

レジスタ定義ファイルのサンプル

Arm® DS / DS-5 のレジスタ・ビューが対応していない Arm® 関連のペリフェラルについて、一通りのレジスタ定義を記述した .tcf ファイルを掲載しておきます。レジスタ定義ファイルの記述内容の参考としてご利用ください。

Cyclone® V SoC / Arria® V SoC のデバッグにそのまま利用頂けるように記述していますが、内容が正しいことを保証するものではありません。(ユーザー責任にてご利用ください)

soc_cv_av_hps_addon_dma330__2.tcf

DMA Controller(DMA-330)用のレジスタ定義

soc_cv_av_hps_addon_mpul2_l2c310__1.tcf

L2Cache Controller(L2C-310)用のレジスタ定義

soc_cv_av_hps_addon_mpuscu__2.tcf

Cortex-A9 MPCore 内蔵ペリフェラル用のレジスタ定義

インテル® Arria® 10 SoC 用にベースアドレス定義を変更したバージョンも作成しました。

(こちらもユーザー責任にてご利用ください)

soc_a10_hps_addon_dma330__1.tcf

DMA Controller(DMA-330)用のレジスタ定義[for インテル® Arria® 10 SoC]

soc_a10_hps_addon_mpul2_l2c310__1.tcf

L2Cache Controller(L2C-310)用のレジスタ定義[for インテル® Arria® 10 SoC]

soc_a10_hps_addon_mpuscu__1.tcf

Cortex-A9 MPCore 内蔵ペリフェラル用のレジスタ定義[for インテル® Arria® 10 SoC]

今回は、 Arm® DS / DS-5 のレジスタ定義を自作する方法について記載しました。

次回(最終回)は、FPGA 側のレジスタを表示させる方法について記載します。

おすすめ記事/資料はこちら

Arm DS 活用テクニック ~レジスタ・ビュー[1/3]基本設定

Arm DS 活用テクニック ~レジスタ・ビュー[2/3]レジスター定義の自作

Arm DS 活用テクニック ~レジスタ・ビュー[3/3]FPGA 側のレジスター表示

Arm DS 活用に関する記事一覧

SoC FPGA 関連の記事や資料

インテル® FPGA の SoC FPGA

インテル® FPGA の開発フロー/FPGA トップページ