DC/DCコンバーターのスイッチング周波数は、高くすべきか低く抑えるべきか悩んだことはありませんか?

少し前は300~500KHzが主流でしたが、最近は1~2MHzのスイッチング周波数の製品が一般的になってきて、なかには4MHz以上の製品まであります。

高い周波数のDC/DCコンバーター使用した場合、使用するインダクターサイズを小さくできるなどのメリットを、前回の記事「レギュレーターにおける高いスイッチング周波数を取り扱うためのPCBレイアウト(1)」でLTspiceの理想回路を使用した説明でご理解いただけたかと思います。

今回の記事では、実際に製品化されている昇圧のスイッチングレギュレーターLTC1871のシミュレーション回路を用いて、スイッチング波形を確認しPCB レイアウト上の寄生インダクタンスの影響を確認します。

理想的なモデルでシミュレーションを実施した場合

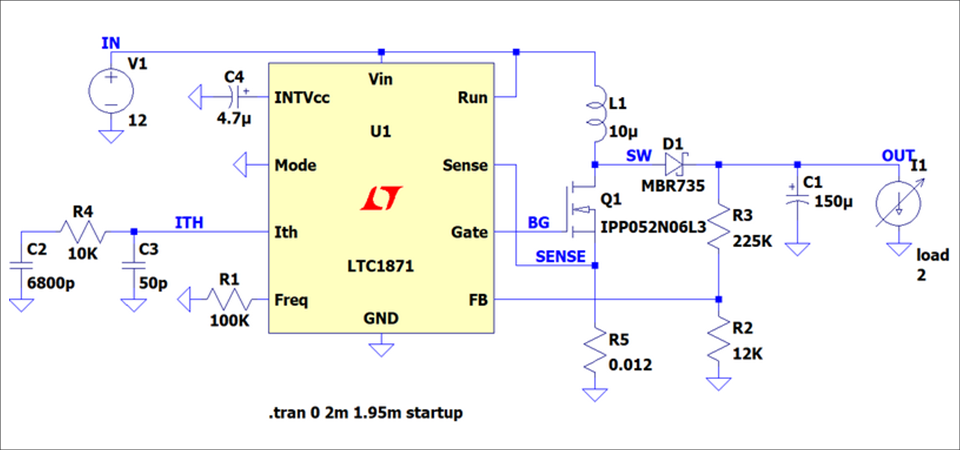

スイッチングレギュレーターLTC1871は、出力に外付けのMOSFETとショットキーダイオードを使用した非同期式昇圧コンバーターです。

LTC1871のSPICEモデルを用いて図1のような、入力電圧12(V)、出力電圧24(V)、負荷電流2(A)の昇圧コンバーターを構成しました。

シミュレーションを実行して、各端子の波形を確認したいと思います。

作成したLTspiceファイルは、下記リンクからダウンロードして実行してください。

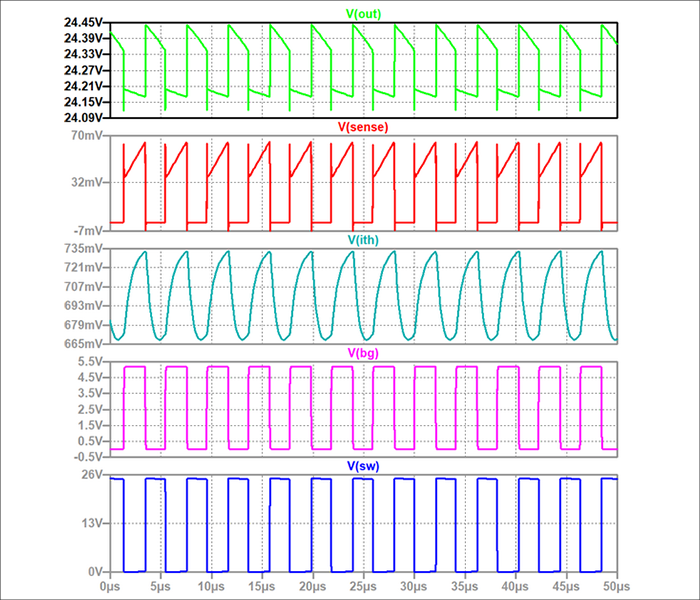

シミュレーション結果

図2がシミュレーション結果になります。上から、出力波形、SENSEピンの波形、Ithピンの波形、GATE(BG)ピンの波形、スイッチ(SW)ノードの波形となります。

波形をみると安定しています。制御ピンIthの信号は綺麗で、SENSEピンには通常の立ち上がりエッジスパイクしかありません。また、スイッチノードには電圧スパイクがありません。この波形は、実際の昇圧コンバーターの波形と同じでしょうか?

実際には、シミュレーションの波形と全く異なる波形となります。スイッチノードにはオーバシュートが発生することがありますし、GATEピンにはアンダーシュートが発生することもあり、GATEピンの絶対最大仕様に違反する可能性があります。また同様にスイッチノードがアンダーシュートして絶対最大定格を違反する恐れがあります。これらの症状は、現実世界で起こりうることで、PCBレイアウトによってさらに悪化する可能性があります。

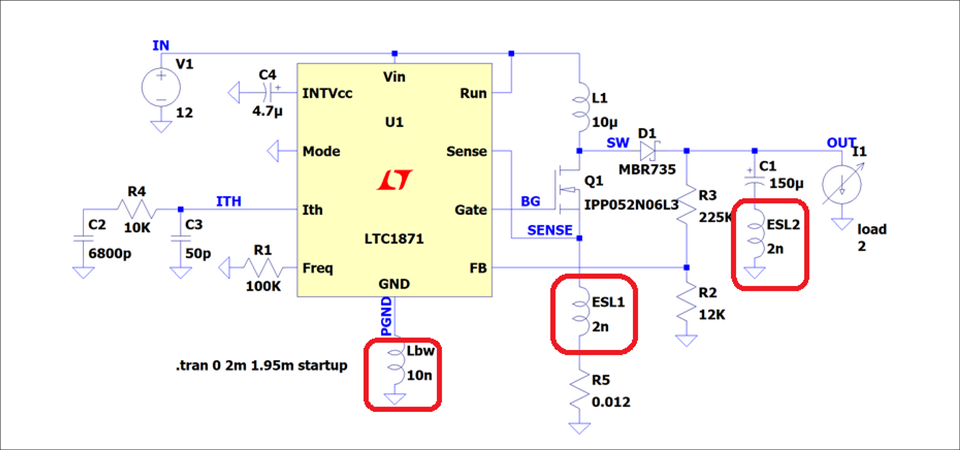

基板パターンの寄生インダクタンスを考慮した場合

さて、実際の回路には寄生インダクタンスなどの寄生成分があります。図3は、寄生インダクタンス(赤枠)を追加した昇圧コンバーター回路を示します。この回路には、コントローラーのGNDピンに寄生インダクタンスを追加しています。 これは重要な要素で、これから説明いたします。赤枠以外の寄生インダクタンスは、今回のシミュレーションでは重要ではないため省略しています。

寄生インダクタンスは、コンポーネントの形状やPCBレイアウトに起因します。MOSFET、ダイオード、出力コンデンサーと直列の寄生インダクタンスは、電流スルーレートが非常に高いために問題になる可能性があります。 電流のスルーレートが高いと、これらの寄生インダクタンスに大きな電圧が発生します。

寄生インダクタンスの影響

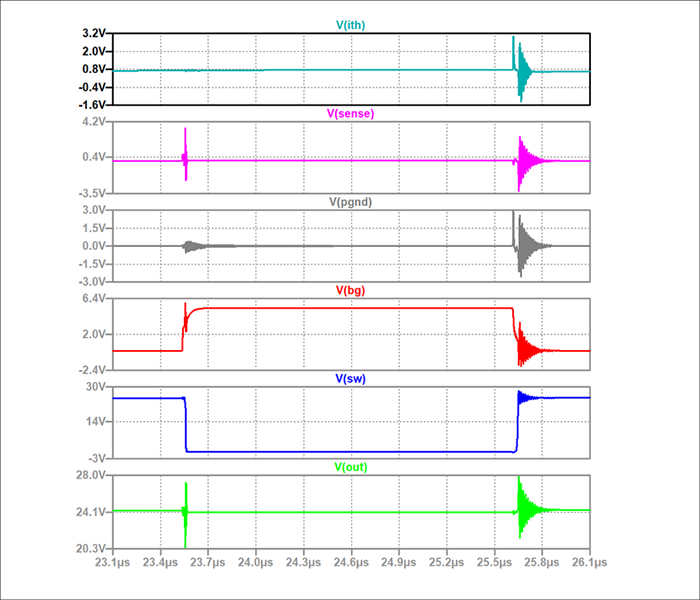

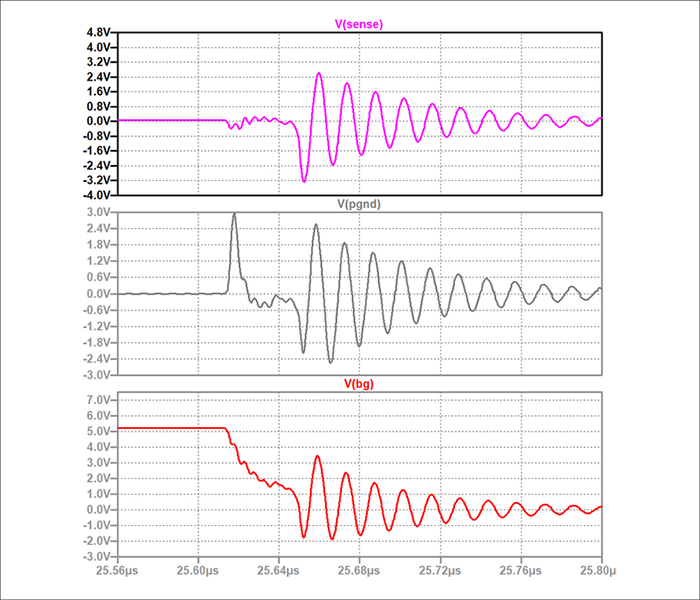

さて、シミュレーション結果を見てみましょう。

図4のインダクタンスの影響を受けた出力波形を確認します。かなりの量の高周波リンギングがあります。1段目のIth制御ピンと2段目のSENSEピンに電圧スパイクがあります。コントローラーが影響を受ける可能性があるため、これらの電圧スパイクは非常に問題になる可能性があります。

また、3段目のコントローラーのPGNDにリンギングがあります。これにより、外部コンポーネントとコントローラーのGNDとの間に電圧差が生じます。4段目のGATEドライブピンにも過度のリンギングがあります。 このリンギングは、ゲートピンの最大定格を超え、故障の原因となる可能性があるので注意が必要です。

もう少し波形を拡大してみてみます。

図5の拡大出力波形を見てみると、寄生インダクタンスによる問題が良くわかります。一番の問題は、コントローラーピンの最大定格を超えることです。特に、ゲートドライバーのピンはリンギングの影響を受け、回路の問題を引き起こす可能性があります。これらの問題を最小限に抑えるには、寄生インダクタンスを最小限に抑える必要があります。

1つ目の注意点としては、パワーMOSFETや出力コンデンサーについて寄生インダクタンスが小さい部品を選択することです。

外付けパワーMOSFET(IPP052N06L3)のパッケージは、TO-220パッケージとTO-263タイプのパッケージがあります。TO-220のパッケージには、長さ約13mmのシングル・ソースピンがあります。TO-263タイプのパッケージは、約4mmの長さのソース・ピンがあります。 長さだけで考えると、TO-220パッケージはTO-263タイプ3倍以上大きいな寄生インダクタンスを持つことが考えられます。

出力コンデンサーのインダクタンスを最小限に抑えるためには、リード端子をを持つコンデンサーではなく、表面実装タイプのセラミック コンデンサーを選択することを推奨します。また、セラミックコンデンサーを並列に接続することにより、等価直列インダクタンスが大幅に減少します。

2つ目の注意点は、寄生インダクタンスを低減するために、パワーMOSFET、ダイオード、および出力コンデンサーは可能な限り近くに配置し太く短い配線で接続する必要があります。これは、最も重要なレイアウトの約束事になります。

まとめ

図1のような理想てきなシミュレーションでは、LTC1871自体のGNDも外付けの部品のGNDも理想的な同電位にすることができます。しかしながら、実際には図3のような回路のように各部品やPCB上の寄生インダクタンスなどによって電位が揺れることがわかりました。

これらの寄生インダクタンスの影響により、電源ICの誤動作や不具合が発生する可能性があることをシミュレーション波形からも理解いただけたかと思います。

次回の記事で最終回となりますが、パワーグランドとシグナルグランドに特化した形でLTspiceを用いてシミュレーションをおこない、PCBレイアウトの影響と注意点について考えてみたいと思います。

おすすめセミナー/ワークショップはこちら

[オンラインセミナー] アナログソリューション 電源設計セミナー <無料>

おすすめ記事/資料はこちら

お問い合わせ

本記事に関して、ご質問などありましたら以下よりお問い合わせください。

アナログ・デバイセズ メーカー情報Topへ

アナログ・デバイセズ メーカー情報Topページへ戻りたい方は、以下をクリックください。