最近の Altera® FPGA では、当然のように DDRx などの外部メモリー・インターフェース(External Memory Interface / EMIF)をサポートしていますよね。ちなみに、EMIF を「いーみふ」と Altera® FPGA 関係者では呼んでいます。

Altera® FPGA にメモリー・コントローラーを実装しようと思った時に、まずどんなことを考えますか?

- どの FPGA デバイスがサポートしているのか?

- どのメモリー規格をサポートしているのか?

- どの程度の転送レートをサポートしているのか?

などなど、いろいろ気になることがあると思います。

このページでは、初めて Altera® FPGA で EMIF を実現する人向けに、DDRx SDRAM コントローラーを例に、簡単に選定から動作確認までの流れを紹介します。

EMIF サポート状況の確認

Altera® FPGA の EMIF サポート状況を確認するための便利なページを紹介します。

- External Memory Interfaces IP Support Center (Altera® のサイト 英語版)

このページにリンクされている『外部メモリー・インターフェース・スペック・エスティメーター(External Memory Interface (EMIF) Spec Estimator)』を使用すると、Altera® FPGA の EMIF サポート状況を確認することができます。

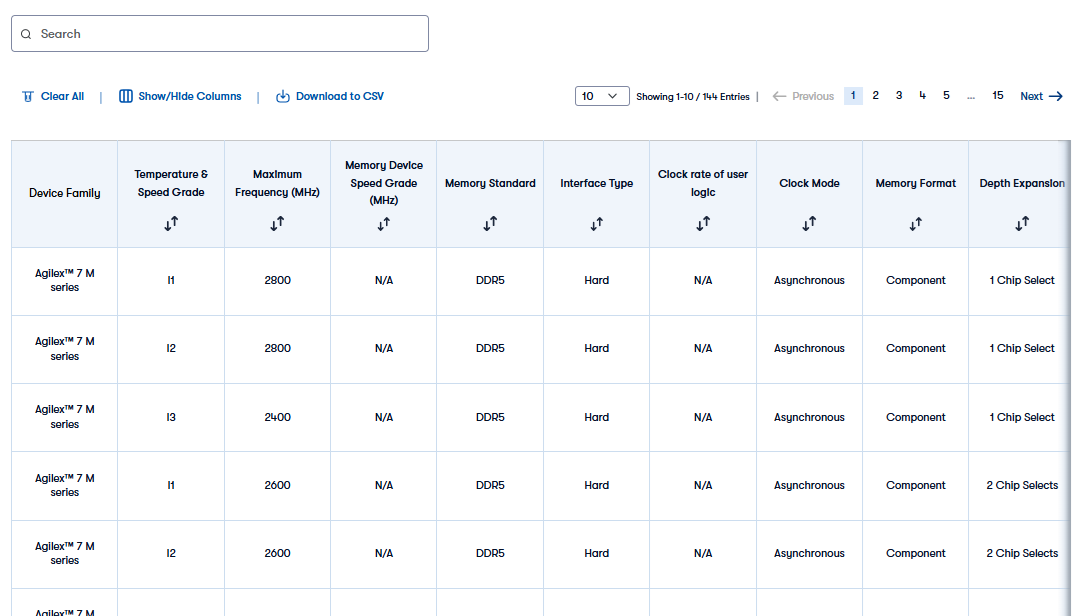

デバイス・ファミリーやスピード・グレード、インターフェースの種類、メモリー規格、周波数など、いろいろな条件を入れて検索することができます。

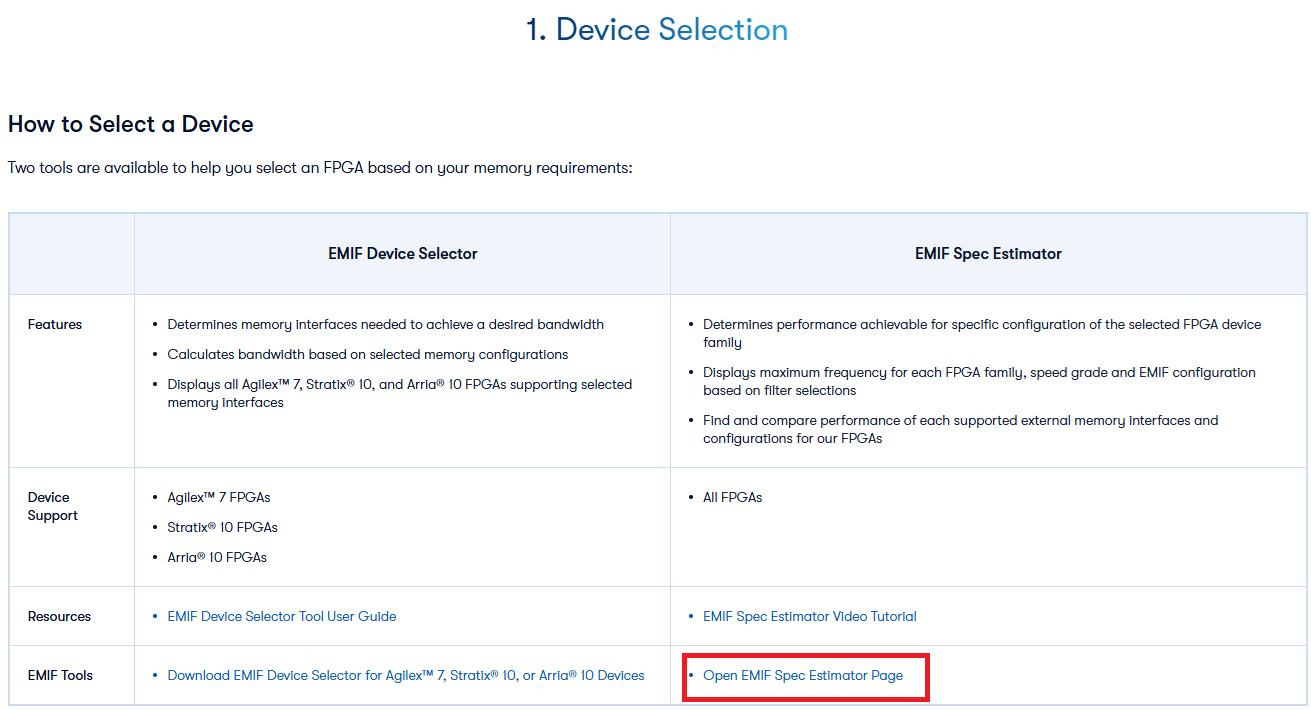

まずは、External Memory Interfaces IP Support Center 内にある Open EMIF Spec Estimator Page(下図)をクリックします。

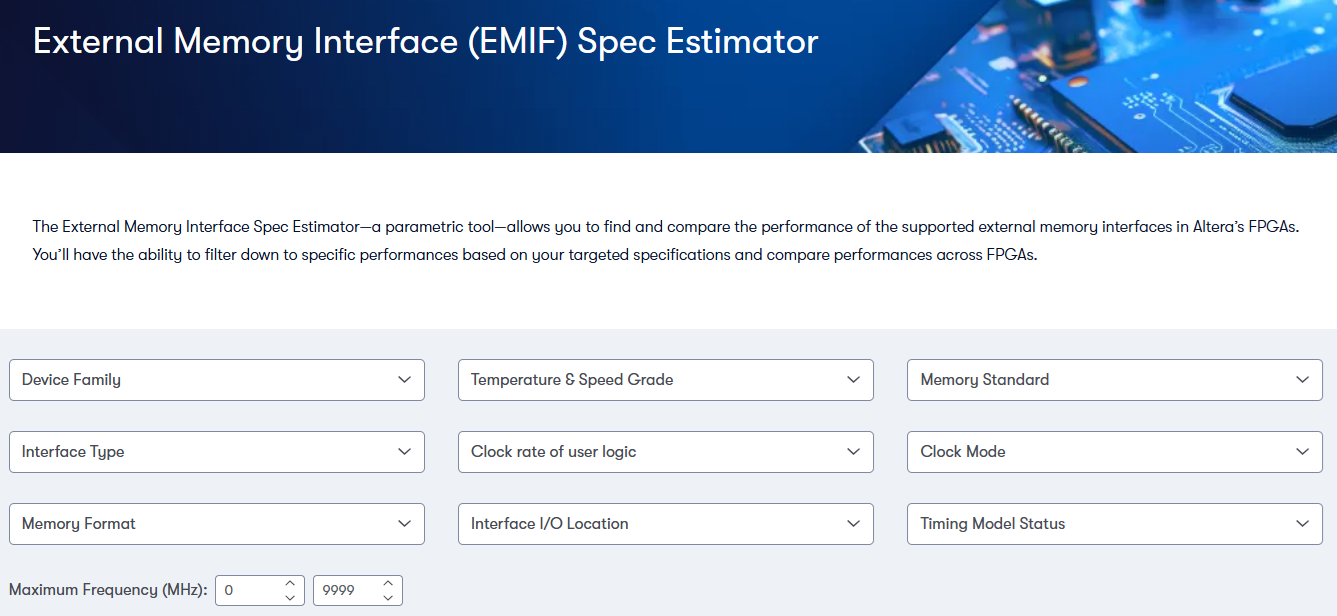

External Memory Interface (EMIF) Spec Estimator(下図)が表示され、各種条件の選択(絞り込み)をおこないます。

デバイス・ファミリー

使用する、もしく候補に挙がっているデバイス・ファミリーにチェックを入れます。複数のデバイス・ファミリーにチェックすることもできます。

全くチェックしなかった場合は、すべてのデバイス・ファミリーが対象となります。

温度範囲 & スピード・グレード

デバイスの温度範囲やスピード・グレードにチェックを入れます。

<温度範囲>

下記の温度範囲が存在します。ただし、デバイスによって存在する温度範囲と存在しない温度範囲がありますので、詳しくは各デバイスのドキュメントをご覧ください。

- コマーシャル温度範囲(C 品):ジャンクション温度 0~85℃

- インダストリアル温度範囲(I 品):ジャンクション温度 -40~100℃

- オートモーティブ温度範囲(A 品):ジャンクション温度 -40~125℃

- 拡張温度範囲(E 品)::ジャンクション温度 0~100℃

- ミリタリー温度範囲(M 品):ジャンクション温度 -55~125℃

<スピード・グレード>

デバイス・ファミリーによって、ある程度存在するスピード・グレードが決まっています。詳しくは各デバイスのドキュメントをご覧ください。

インターフェースの種類

- ソフト

ロジックや内部メモリーなどの FPGA のリソースを消費してメモリー・コントローラーを実装します。ソフト・メモリー・コントローラー(SMC)とよく呼ばれます。

- ハード

予めデバイス内部にハード・マクロとして搭載されているメモリー・コントローラーを使用します。ハード・メモリー・コントローラー(HMC)とよく呼ばれます。

- ハード HPS

ARM* コア内蔵の SoC FPGA のハード・プロセッサー・システム(HPS)に搭載されたメモリー・コントローラーを使用します。

メモリー規格

外部メモリー規格を選択します。

ローカル・インターフェース(User Logic)のクロック・レート

あらかじめ、指定がある場合は、選択してください。

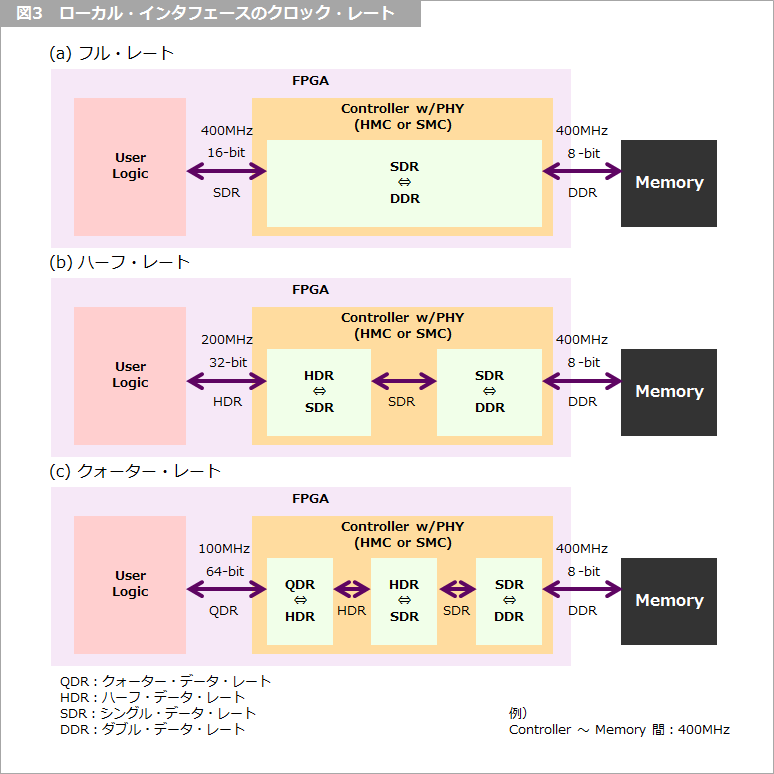

イメージは、下図の通りです。(イメージしやすくするため、コントローラー ~ メモリー間を 400MHz(800Mbps)のダブル・データ・レートを例にしています。)

簡単に言うと、コントローラー ~ メモリー間は高速、かつダブル・データ・レートでデータ伝送されますが、FPGA 内はダブル・データ・レートのままではデータ処理できないので、まず同周波数でシングル・データ・レートに変換します。でも、この時、データ幅が倍になります。これが、フル・レートです。

次に、フル・レートで周波数が高すぎて FPGA 内でデータ処理できない場合は、更に周波数を半分にします。でも、この時、データ幅が更に倍になります。これが、ハーフ・レートです。

更に、ハーフ・レートでも周波数が高すぎて FPGA 内でデータ処理できない場合は、さらに周波数を半分にします。でも、この時、データ幅が更に倍になります。これが、クォーター・レートです。

メモリー・フォーマット

この項目は、メモリー・トポロジーを選択します。コンポーネント(メモリー・デバイス)、モジュール(DIMM など)を選択します。

インターフェース I/O の位置

この項目では、FPGA のどのバンクに EMIF 関連のピンを配置するかを指定します。FPGA によっては、I/O バンクの位置によってサポートする転送レートが異なるものがあります。

タイミングモデル状況

タイミングモデルの対応状況を選択します。

最大周波数 (MHz)

メモリー・インターフェース(メモリー・コントローラー ~ メモリー間)の周波数の上限と下限を指定します。

検索結果

「条件を確定し、検索」をクリックすると、指定した条件を満たした結果が表示されます。結果が表示された後も、更に条件を指定して絞り込むことができます。

この結果から、外部メモリー・インターフェース部について採用する FPGA の候補が確認できますので、他のインターフェースや条件などを加味して、使用する FPGA をご検討ください。

実践編

実践編として Altera® FPGA に実装するメモリー・コントローラーの生成やシミュレーション方法、開発キットを使用した動作確認の方法を紹介します。

DDR4

DDR3

デザイン&デバッグ・ガイドライン

外部メモリー・インターフェース(External Memory Interface/EMIF)の高速化に伴い、データ・バリッド・ウインドウ(データの有効なウィンドウ)の縮小や信号品質の悪化が課題として挙げられています。

要求仕様を満たすための検証やデバッグに費やす時間が増加傾向にあるため、適切な手順でデバイス・ボードの設計をおこない、かつ、設計段階であらかじめデバッグするための手段を実装することが重要です。

本資料はデザイン・フローとデバッグ・フローを示し、適切な手順で設計することにより、不具合の混入を防ぐこととデバッグに必要な仕組みを実装することにより、速やかに問題を解決することを目的として作成されたものです。

FPGA の EMIF デザイン & デバッグ・ガイドライン

おすすめ記事/資料はこちら

Altera® FPGA で DDR3 動作!(実践編)[1/2]

Altera® FPGA で DDR3 動作!(実践編)[2/2]

Altera® FPGA で DDR4 動作!(実践編)

FPGA の EMIF デザイン & デバッグ・ガイドライン

Altera® FPGA の開発フロー/トップページ