Altera® FPGA に DDR3 SDRAM メモリー・コントローラーを実装して、Example Design を用いたシミュレーションや動作確認までの流れをやさしく解説します。このページでは Cyclone® Vデバイスが実装されている Beryll Cyclone V GX ベーシックボード(Beryll ボード) を使用して説明しますが、UniPHY ベースの DDR3 SDRAM コントローラーをサポートしている Stratix® シリーズや Arria® シリーズでも、基本的なフローは同じです。

<アジェンダ>

1. Cyclone® V デバイスの DDR3 SDRAM サポート状況の確認

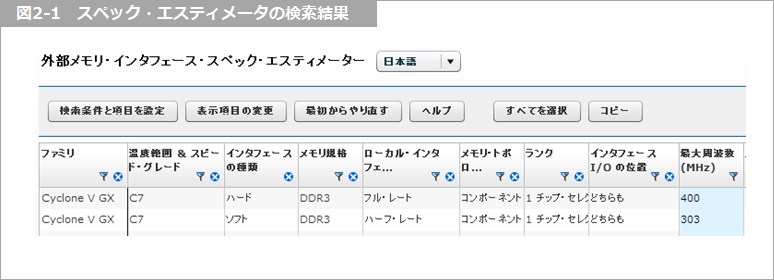

DDR3 SDRAM インターフェースのサポート状況は、『Altera® FPGA に外部メモリー・コントローラーを実装!(準備編)』でも紹介している通り、外部メモリー・インターフェース・スペック・エスティメーター で確認することができます。

外部メモリー・インターフェース・スペック・エスティメーターに条件を入れていきます。今回の検証で使用する Beryll Cyclone V GX ベーシックボード(Beryll ボード) に実装されている Cyclone® V デバイス(型番:5CGXFC4C6F27C7N)やメモリー、ボードの仕様など「検索条件と項目を決定」ボタンをクリックして、下記条件を入れてみます。

- ファミリ:Cyclone® V GX

- 温度範囲 & スピード・グレード:コマーシャル温度範囲 (C)、-7

- インターフェースの種類:ソフト、ハード

- メモリー規格:DDR3

- メモリー・トポロジー & ランク:コンポーネント、1 チップ・セレクト

検索結果は、以下の通りとなりました。ちなみに、型番の後半部分の C7 が、温度範囲 & スピード・グレードを表しています。

この検索結果から、Beryll ボードで確認できるのは、

- ハード・メモリー・コントローラー(HMC)だと、最大周波数は 400 MHz (800 Mbps) まで

- ソフト・メモリー・コントローラー(SMC)だと、最大周波数は 303 MHz (606 Mbps) まで

ということになります。従って、今回は

- ハード・メモリー・コントローラー(HMC)で、メモリー・インターフェースの周波数は 400 MHz (800 Mbps)

で動かしてみたいと思います。

それでは、Altera® Quartus® Prime 開発ソフトウェアを使用して、実際にコントローラーを生成してみましょう!

<使用するツール>

- Quartus® Prime 開発ソフトウェア v16.0:Standard Edition または Lite Edition

- Standard Edition:有償ライセンス必要

- Lite Edition:ライセンス不要

- ModelSim® - Altera® FPGA Edition 10.4d (Quartus® Prime 16.0)

- ModelSim® - Altera® FPGA Edition:有償ライセンス必要

- ModelSim® - Altera®FPGA Starter Edition:ライセンス不要

ツールのインストールは済んでいますか?

インストールが済んでいない方は、Altera® FPGA のサイト(ダウンロード)から入手できます。

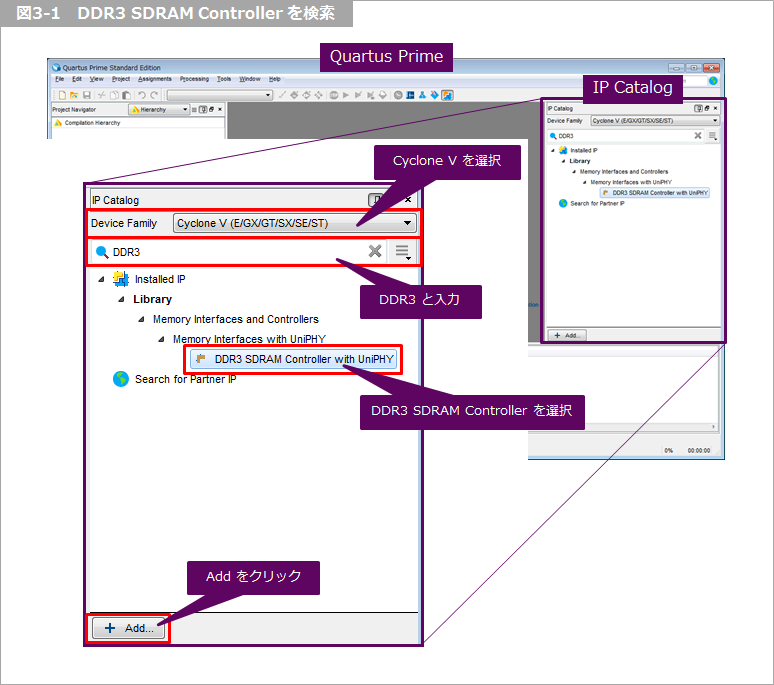

2. DDR3 SDRAM コントローラー with UniPHY の生成

まずは、メモリー・コントローラーを生成してみましょう!

Quartus® Prime 開発ソフトウェアを起動して、IP Catalog の検索バーに DDR3 と入力して、DDR3 SDRAM Controller with UniPHY を検索します。

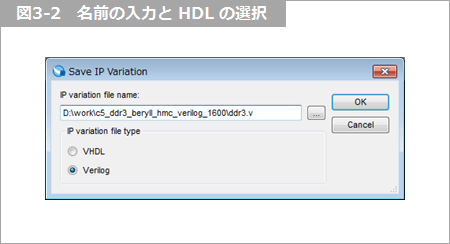

コントローラー関連のさまざまなファイルを生成するディレクトリーとコントローラーの名前を設定する画面が現れます。生成する言語(Verilog または VHDL)も選択して OK をクリックします。この時、パスやファイル名に全角文字や半角スペースは避けましょう!今回は、コントローラーを ddr3 という名前にします。

すると、コントローラーの設定画面が表示されます。必要な設定をしていきましょう!

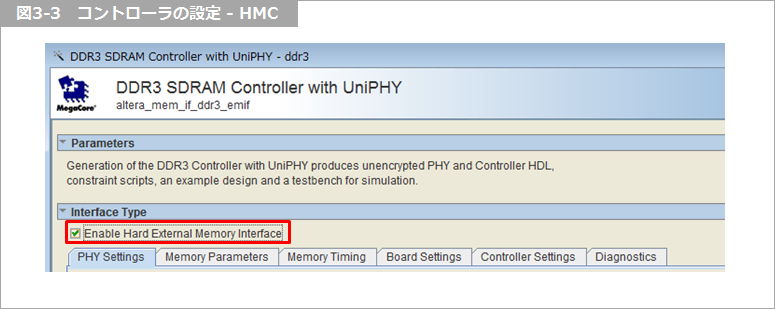

まずは、HMC を有効に設定します。

以降、必要な設定をしていきますが、今回は Beryll ボードで動作確認する上で必要最小限の設定しかおこないません。それ以外は、デフォルトのままとします。

詳細は、EMIF ハンドブック を参照してください。

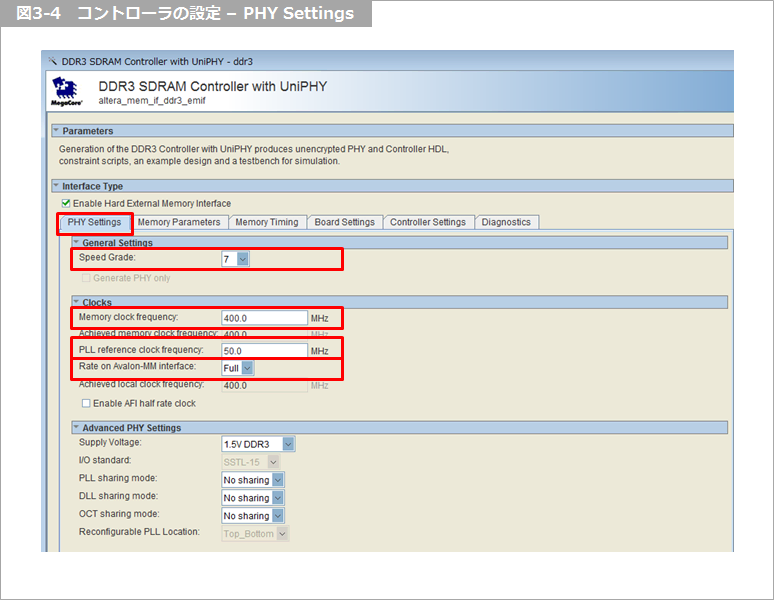

PHY Settings タブ

今回はリファレンス・クロックに 50 MHz のクロックを使用します。PHY Settings タブは、以下の設定をおこなってください。

- Speed Grade:7

- Memory clock frequency:400.0 MHz

- PLL reference clock frequency:50.0 MHz

- Rate on Avalon-MM interface:Full

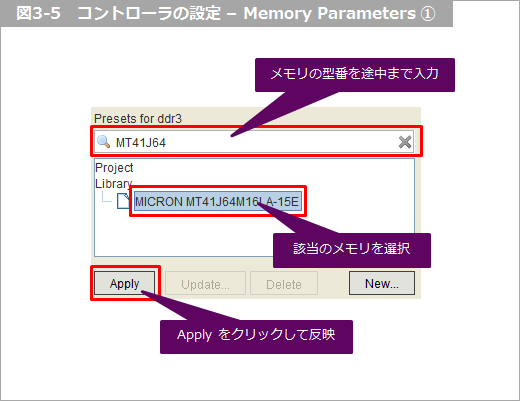

Memory Parameters タブ

Beryll ボードに実装されている DDR3 SDRAM は、Micron の MT41J64M16 が 2個です。このメモリーは 1個当たり 16-bit 幅なので、合計で 32-bit 幅となります。

右側の Preset for ... から、実装されているメモリーを探します。ここには代表的なメモリーが予めリスト化されていて、細かいパラメーターも設定済みです。今回は運よく、実装されているメモリーがありましたので、選択して Apply をクリックします。そうすると、メモリーの構成やパラメーターなどが反映されます。もし使用したいメモリーがリストにない場合は、構成などが似ているメモリーを選択してパラメーターをデータシートを見ながら編集し、名前を付けて保存すると、次からは簡単に呼び出せます。

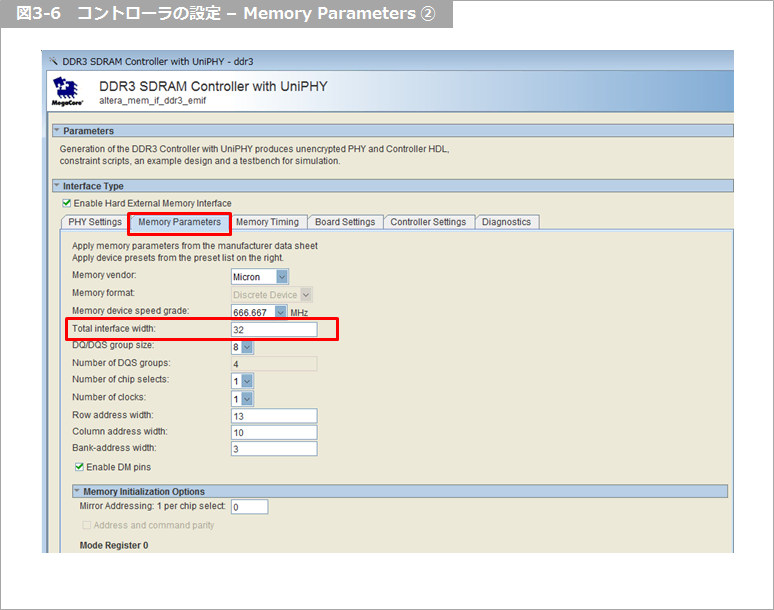

Beryll ボード上で Cyclone V デバイスとメモリー間はデータが 32-bit 幅で接続されているので、今回の検証も 32-bit 幅でおこなってみようと思います。

今回は、以下の設定のみ Memory Parameters タブ内の設定をします。

- Total interface width:32

Memory Timing タブ

先ほど Memory Parameters タブでメモリ情報を反映させたので、設定はそのままにします。

Board Settings タブ

今回は、デフォルトのままとします。

Controller Settings タブ

今回は、デフォルトのままとします。

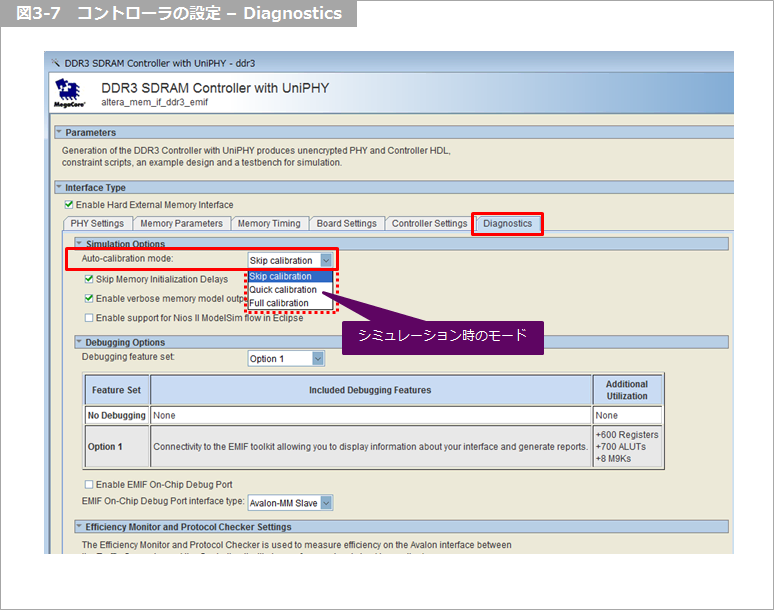

Diagnostics タブ

今回は、Auto-calibration mode のみ設定します。この設定はシミュレーションのみ有効で、実機動作には影響しません。

DDR3 SDRAM インターフェースは、電源オン後すぐにリード/ライトできる訳ではなく、初めにイニシャライズやキャリブレーションなどがおこなわれます。詳しい説明はここでは省略しますが、これらのステップを踏まないとリード/ライトなどのアクセスができません。

このキャリブレーションをシミュレーションではスキップさせることができます。もちろん、フルでキャリブレーションの動きをシミュレーションで確認することもできますが、構成によっては相当な時間が掛かるので、覚悟が必要です。このキャリブレーションの省略度合を設定するのが、Auto-calibration mode です。

- Skip calibration:キャリブレーションをスキップ

- Quick calibration:キャリブレーションを一部だけ実行

- Full calibration:キャリブレーションを省略することなく実行

コントローラーの生成

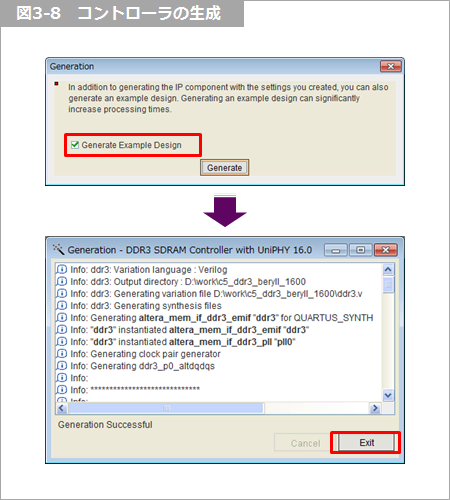

Finish をクリックして、コントローラーを生成させます。この時、下図のように Generate Example Design にチェックを入れて Generate をクリックすると、シミュレーションや実機動作が簡単におこなえる環境(Example Design)も同時に生成してくれます。

コントローラーの生成は、数分程度掛かります。生成が終わったら、Exit をクリックします。

続きは、『Altera® FPGA で DDR3 動作!(実践編)[2/2]』をご覧ください。

メーカーの情報

外部メモリー・インターフェース(Altera®のサイト)

おすすめ記事/資料はこちら

FPGA の EMIF デザイン & デバッグ・ガイドライン

Altera® FPGA に外部メモリー・コントローラーを実装!

Altera® FPGA の開発フロー/トップページ