3. ファンクション・シミュレーションの実行

次に、ファンクション・シミュレーションを実行してみます。シミュレーションを実行するために必要なファイル(シミュレーション用プロジェクトやテストベンチ、トラフィック・ジェネレーター、メモリー・モデルなど)も、コントローラーの生成時に自動で生成されるので、手間を掛けずにシミュレーションできます。

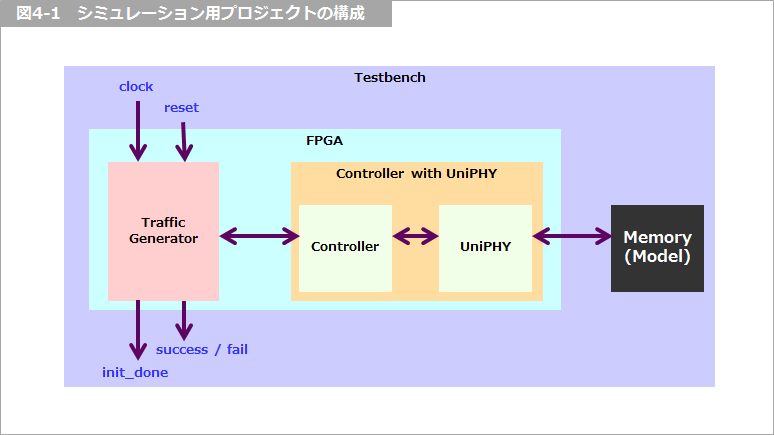

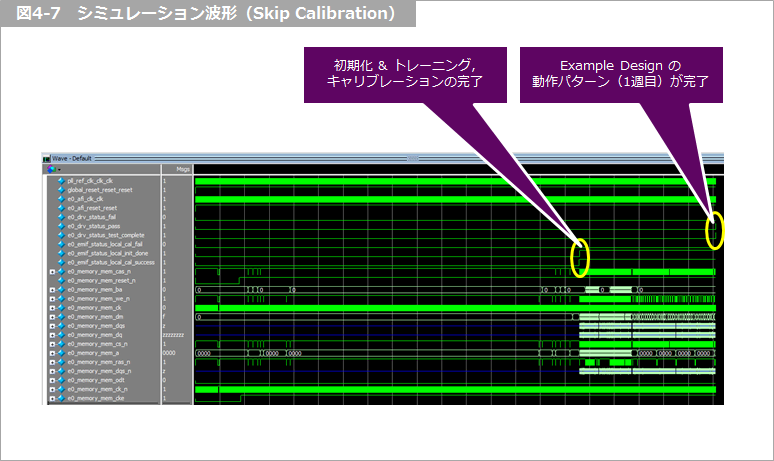

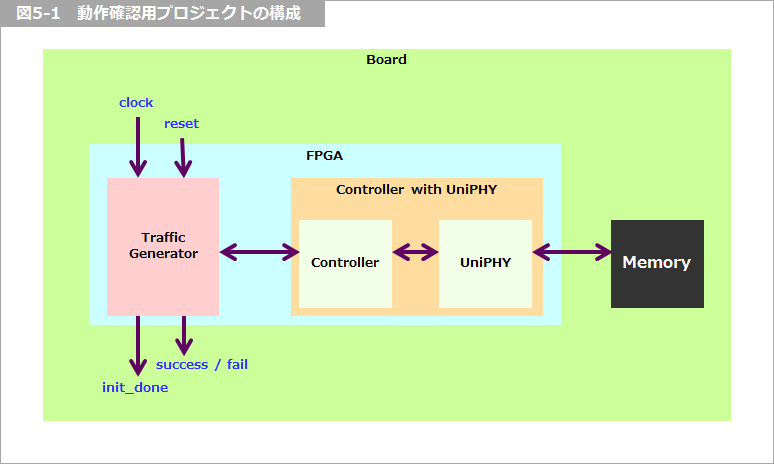

シミュレーションの簡単な動きを説明すると、クロックの供給を受けているトラフィック・ジェネレーターからメモリー・コントローラーへアドレスやコマンド、データが送られ、UniPHY を介してメモリーへライトされます。その後、メモリーからリードされたデータがライトしたデータと比較されます。一致していれば Success = High、一致していなければ Fail = High となります。

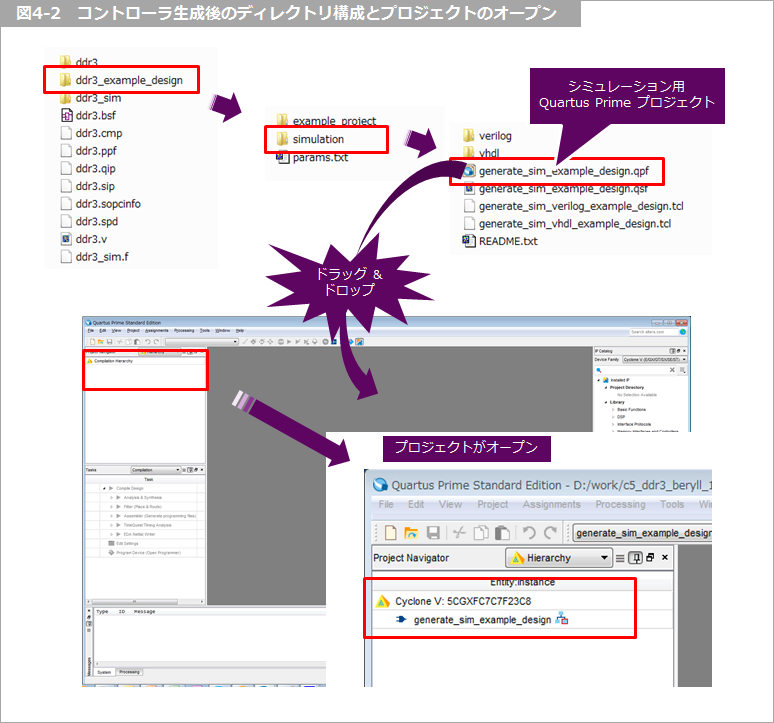

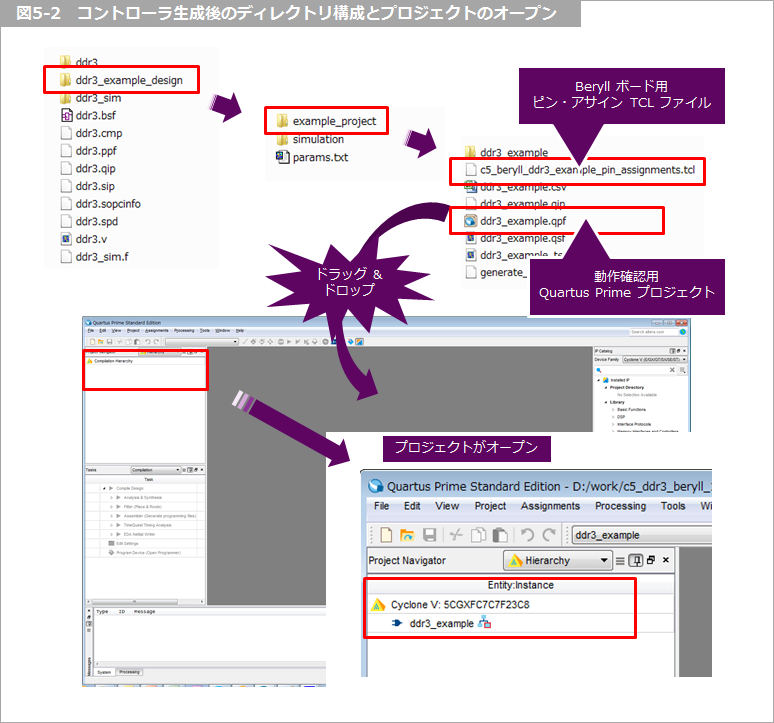

まずは、コントローラー生成時後のディレクトリーやファイルを見てみましょう!

上図のように、シミュレーション用の Quartus® Prime プロジェクトが生成されているので、Quartus® Prime 上の File メニュー ⇒ Open Project でシミュレーション用プロジェクト(QPF ファイル)を選択して、プロジェクトを開きます。(Windows* のエクスプローラ上から QPF ファイルを Quartus® Prime へドラッグ & ドロップでも大丈夫です。)

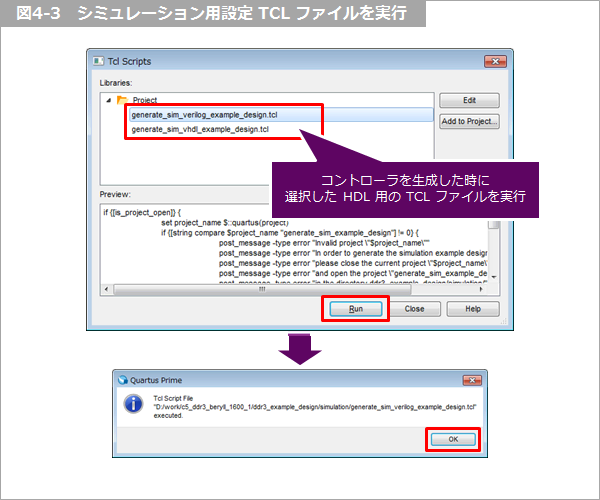

プロジェクトが開いたら、Quartus® Prime の Tools メニュー ⇒ Tcl Scripts を選択して、シミュレーション用設定 TCL ファイルを選択して Run をクリックして実行します。この時、コントローラー生成時に選んだ HDL(Verilog or VHDL)を選んでください。これも完了まで数分掛かります。TCL ファイルの実行が終わったら、Close をクリックします。

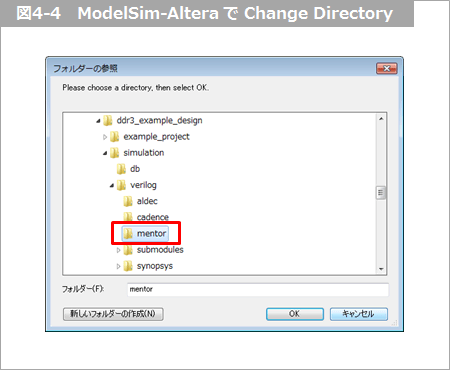

次に、ModelSim® - Altera® FPGA Edition を起動します。起動したら、ModelSim® - Altera® FPGA Edition の File メニュー ⇒ Change Directory を選択して、Example Design 格納ディレクトリー ⇒ simulation ⇒ verilog または vhdl ⇒ mentor を選択してください。

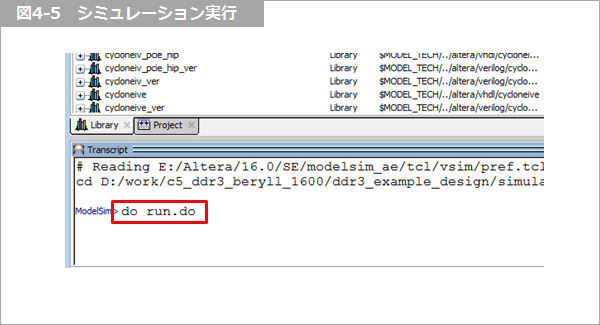

移動したディレクトリーにシミュレーション実行用の DO ファイルが生成されているので、ModelSim® - Altera® FPGA Edition の Transcript ウィンドウ上で do run.do とタイプして Enter キーを押してシミュレーションを実行させます。

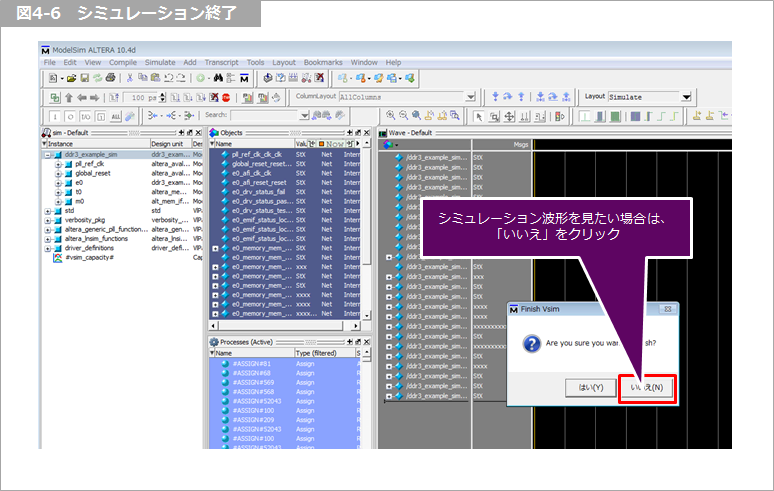

シミュレーション完了まで数分掛かります。シミュレーションが終わったら、自動で停止します。

シミュレーションが完了して波形を確認したい時は、いいえ をクリックしてください。(はい をクリックすると、ModelSim® - Altera® FPGA Edition が閉じてしまいますので、注意してください。)

4. Example Design のコンパイル

続いて、Beryll ボードの Cyclone® V デバイス用のデザインをコンパイルしてみましょう。コンパイルするには、各種設定や制約、ピン・アサインが必要です。

既に Beryll ボードを購入された方は、Mpression の専用ページから回路図やユーザー・ガイドをダウンロードすることができます。これらを見ながらピン・アサインできますが、このページをご覧の方向けに、簡単に DDR3 Example Design のピン・アサインができる TCL ファイルを用意しました。この TCL ファイルをダウンロードしたら、Example Design のプロジェクト・ディレクトリーに保存してください。また、Beryll ボードの回路図もこのページから特別にダウンロードできちゃいます。

c5_beryll_ddr3_example_pin_assignments__1.tcl

Beryll ボード向け DDR3 SDRAM インターフェース Example Design のピン・アサイン TCL ファイル

Beryll ボードの回路図(Rev.A)

次に、動作確認用 Example Design のプロジェクトを開きます。Quartus® Prime 上の File メニュー ⇒ Open Project で動作確認用のプロジェクト(QPF ファイル)を選択して、プロジェクトを開きます。(Windows* のエクスプローラー上から QPF ファイルを Quartus® Prime へドラッグ & ドロップでも大丈夫です。)

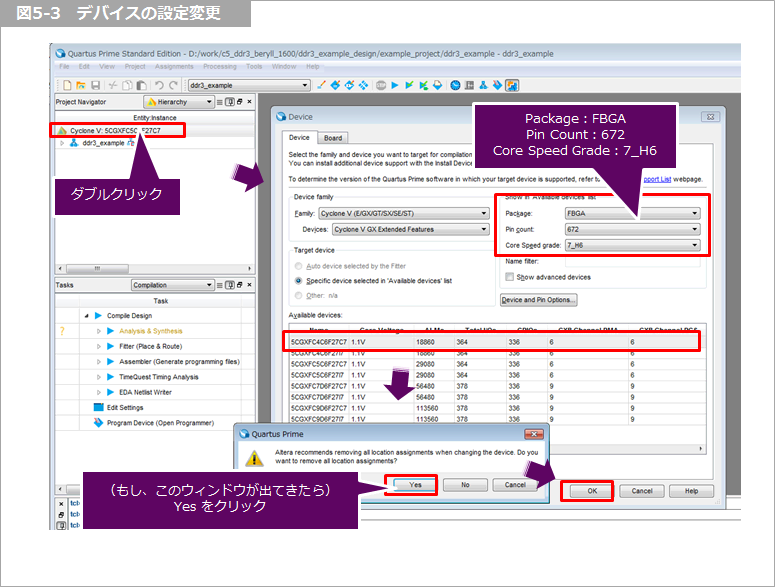

プロジェクトを開いたら、デバイスの変更をおこないます。Beryll ボードには 5CGXFC4C6F27C7N という型番の Cyclone® V デバイスが実装されているので、その型番に設定します。型番の最後の N は鉛フリー品であることを示しています。Quartus® Prime 上ではこの N は表示されないので、5CGXFC4C6F27C7 を選んでください。

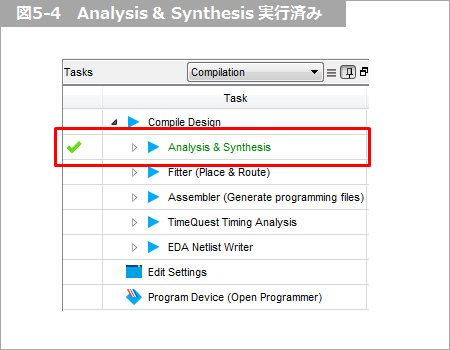

動作確認用のプロジェクトを開いたら、Processing メニュー ⇒ Start ⇒ Start Analysis & Synthesis を選択して論理合成を実行します。(論理合成が正常に終了すると、Tasks ウィンドウの Analysis & Synthesis が緑色のチェック・マークに変わります。

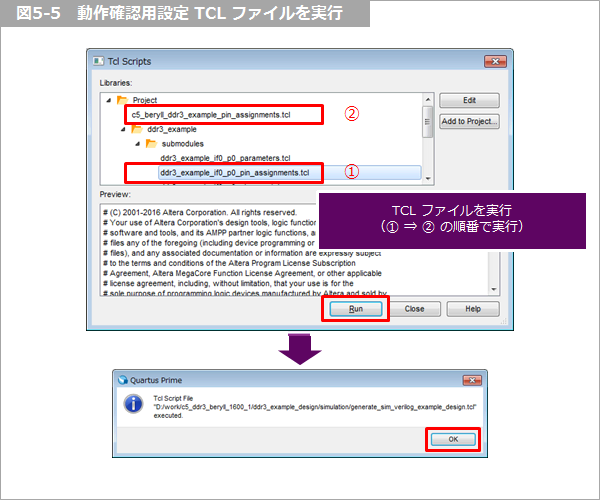

Tools メニュー ⇒ Tcl Scripts を選択して、① の TCL ファイルを選択して Run をクリックします。これはコントローラー生成と同時に生成された DDR3 インターフェース関連ピンの I/O Standard やその他制約などが設定できる TCL ファイルです。

次に ② の TCL ファイルを実行します。これは、先ほど触れた Beryll ボード用のピン・アサイン TCL ファイルで、本記事内からダウンロードできます。Example Design 用のプロジェクト・ディレクトリーに保存していない場合は、このように表示されない可能性がありますので、見えない場合は保存先を再度確認してください。

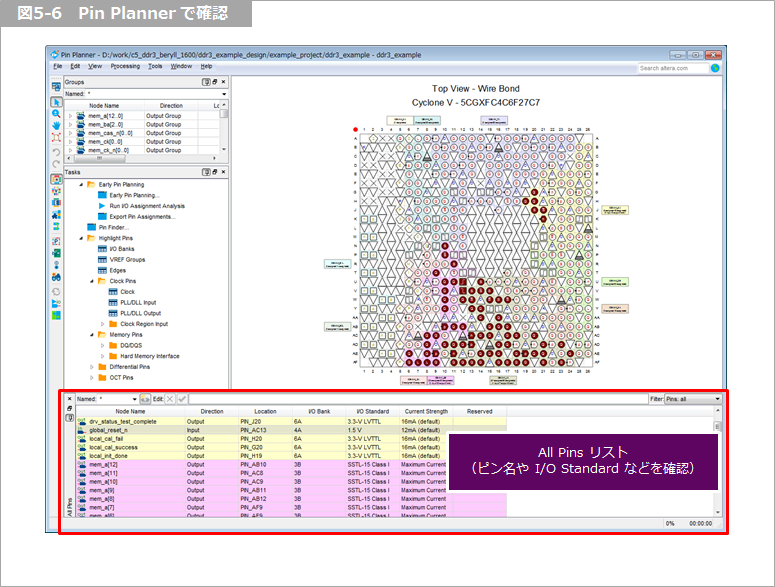

Quartus® Prime の Assignments メニュー ⇒ Pin Planner で Pin Planner を起動して、ピン・アサインやピンの制約がされているかを確認してください。

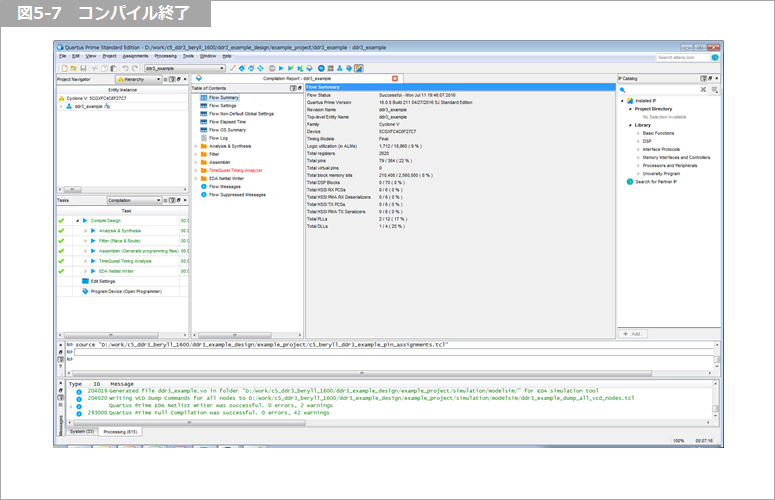

ここまでできたら、コンパイルしましょう。Quartus® Prime の Processing メニュー ⇒ Start Compilation を選択してください。

正常にコンパイルは終了しましたか?

<補足①>

タイミング解析結果(コンパイル・レポートの TimeQuest Timing Analyzer)が赤字になっています。これは、すべてのピンに対してタイミング制約をしていない事に起因しています。しかし、未制約ピンはリセットや JTAG 関連、LED に出力するピンであるため、今回はこのまま進めることにします。

もし、Setup や Hold でタイミング違反が起きている場合は、コンパイルの設定を変更してみましょう。Quartus® Prime の Assignments メニュー ⇒ Settings ⇒ Compiler Settings ⇒ Optimization mode で Performance に設定します。この設定はパフォーマンス重視のコンパイルを目指すものなので、タイミングに関しては改善する傾向にありますが、リソースを多く消費するケースがあります。

<補足②>

メモリ・コントローラーの設定などを変更したい場合は、ddr3.v を開いてから設定を変更して、再生成してください。この時、ピン情報が消えてしまうので、変更前にピン情報をエクスポートしておくことをお勧めします。

【FAQ】既存プロジェクトのピン情報をエクスポートして、別プロジェクトにインポートする方法はありますか?

5. Beryll ボードを使用して動作確認

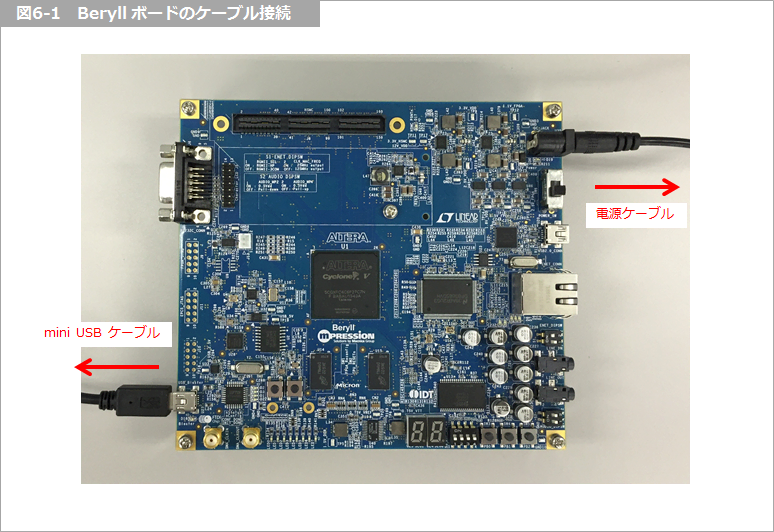

コンパイルが完了したら、コンパイルで生成された SOF ファイルを Cyclone® V デバイスへ書き込みます。Beryll ボードと PC 間を USB ケーブル(Beryll 側:USB Mini-B)で接続し、電源を投入します。

<補足>

Altera® FPGA には、JTAG ポートが備わっています。この JTAG ポートから Altera® FPGA ダウンロード・ケーブルを介して、データを書き込みます。

通常は Altera® FPGA ダウンロード・ケーブル(USB-Blaster™ や USB-Blaster™ II など)を使用しますが、Beryll ボードは Blaster の機能がボード上に実装されているため、別途ダウンロード・ケーブルを用意する必要はなく、USB ケーブルだけでデータ書き込みができます。

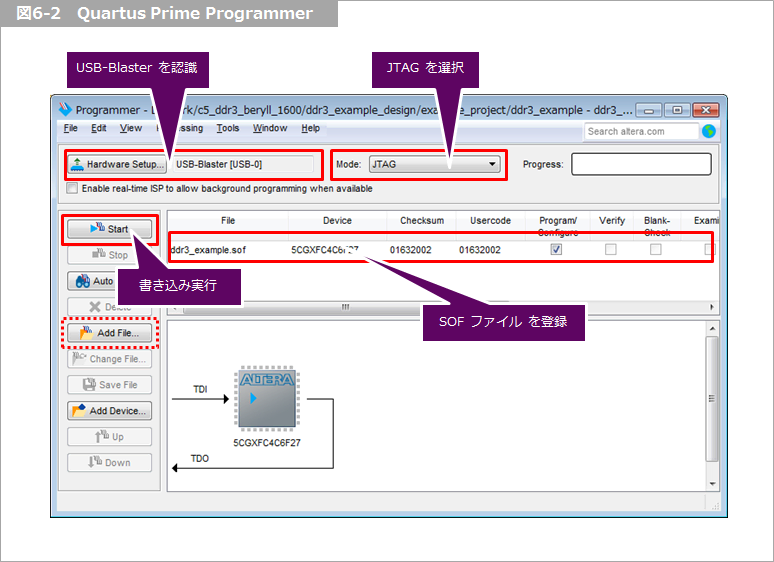

次に、Quartus® Prime の Tools メニュー ⇒ Programmer を選択して、Quartus® Prime Programmer を起動します。

Programmer が起動して、書き込み用の SOF ファイルが自動で登録されていれば、Hardware Setup と Mode が選択されていることを確認してから、Start をクリックして書き込みを実行します。

もし Programmer が真っ新な状態で起動したら、ダウンロード・ケーブルとモード、書き込みファイルを以下のように設定してから、Start をクリックして書き込みを実行します。

- Hardware Setup:USB-Blaster™ を選択(USB-Blaster™ のドライバーをインストールしていないと、選択できません)

- Mode:JTAG を選択

- Add File:コンパイル時に生成された SOF ファイルを選択(ファイル名:<コントローラ名>_example.sof)

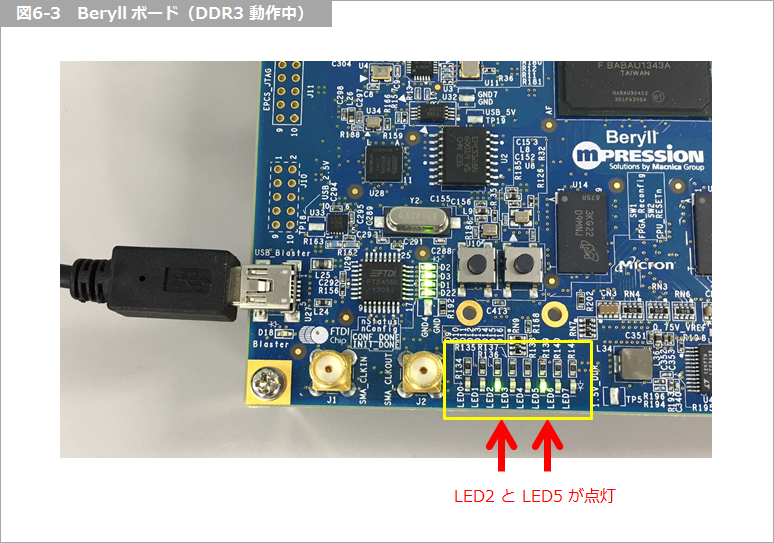

SOF ファイルの書き込みが終わったら、実際に Example Design が動作しています。正常に動作していれば、LED2 と LED5 が点灯しているはずです。

TCL ファイルでピン・アサインしましたが、LED は下表の通りに割り当てられています。ピンが Low レベルだと、LED が点灯するようになっています。

この LED だけ見ていても、本当に動いているかわからないかも知れません。そういう場合、動いている間は LED が点滅するなどのロジックを組み込んでみると面白いかも知れません。

また、SignalTap® II ロジック・アナライザー機能を利用すれば、FPGA 内部信号をモニターすることもできます。これについては、別の機会に紹介したいと思います。

表6-1 Example Design のピン説明(一部)

| ピン名 | LED | 説明 |

| local_Init_done | LED0 | メモリーの初期化(イニシャライズ)やトレーニング、キャリブレーションが完了すると、High にアサートされます。 |

| local_cal_success | LED1 | メモリーの初期化(イニシャライズ)やトレーニング、キャリブレーションが正常に完了すると High にアサートされます。コントローラーがメモリー・インターフェースを使用する準備ができていることを示しています。 |

| local_cal_fail | LED2 | メモリーの初期化(イニシャライズ)やトレーニング、キャリブレーションが失敗すると、High にアサートされます。この時、local_init_done はアサートされません。 |

| drv_status_test_complete | LED3 | Example Design によるメモリーへのライト/リードの動作確認パターンの 1周目が完了すると、High にアサートされます。シミュレーションでは 1周で停止しますが、動作確認用 Example Design では動作確認パターンを繰り返します。 |

| drv_status_pass | LED4 | Example Design によるメモリーへのライト/リードの動作確認パターンが正常に 1周目が完了すると、High にアサートされます。 |

| drv_status_fail | LED5 | Example Design によるメモリーへのライト/リードの動作確認パターンが失敗すると、High にアサートされます。 |

6. まとめ

ここまで、下記のアジェンダに沿って説明しましたが、イメージ掴めましたか?

- Cyclone® V デバイスの DDR3 SDRAM サポート状況の確認

- DDR3 SDRAM コントローラー with UniPHY の生成

- ファンクション・シミュレーションの実行

- Example Design のコンパイル

- Beryll ボードを使用して動作確認

今回は Cyclone® V デバイスが実装された Beryll ボードを例に説明しましたが、UniPHY ベースの DDR3 SDRAM コントローラーをサポートしている Stratix® シリーズや Arria® シリーズでも、基本的なフローは同じです。

ぜひ、この手順を実践してみてください。

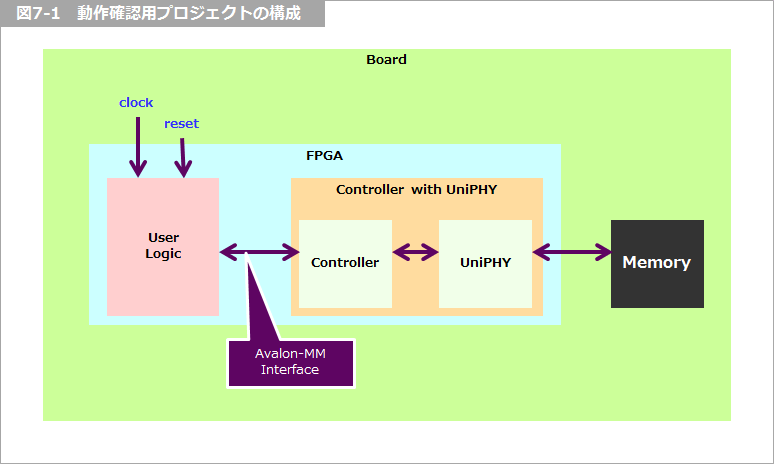

なお、実際にユーザ・デザインに組み込む場合は、下図のように Example Design の Traffic Generator の部分がユーザー・ロジックに置き換わるイメージです。ユーザ・ロジックとコントローラー間は、Avalon-Memory Mapped (Avalon-MM) インターフェースで接続することになります。

おすすめ記事/資料はこちら

FPGA の EMIF デザイン & デバッグ・ガイドライン

Altera® FPGA に外部メモリー・コントローラーを実装!

Altera® FPGA の開発フロー/トップページ

おすすめ FAQ はこちら

メーカーサイト/その他関連リンク

外部メモリー・インターフェース (Altera® のサイト)

Avalon インターフェース仕様 (Altera® のサイト)