Altera® FPGA に DDR4 SDRAM メモリー・コントローラーを実装して、Example Design を用いたシミュレーションや動作確認までの流れをやさしく解説することを目的としているため、詳細な説明は省略しています。このページでは Arria® 10 が実装されている Arria® 10 GX FPGA 開発キットをベースに説明しますが、DDR4 SDRAM コントローラーをサポートしている他の FPGA でも、基本的なフローは同じです。

環境

- 開発ツール:Altera® Quartus® Prime 開発ソフトウェア v17.1(Pro Edition または Standard Edition)

- Pro Edition:有償ライセンス必要

- Standard Edition:有償ライセンス必要

- シミュレーション・ツール:ModelSim® - Altera® FPGA Edition 10.5b (Quartus® Prime 17.1)

- ModelSim® - Altera® FPGA Edition:有償ライセンス必要

- 開発キット:Altera® Arria® 10 GX FPGA 開発キット Macnica-Mouser 購入サイト

Quartus® Prime のエディション比較

ツールのインストールは済んでいますか?

インストールが済んでいない方は、Altera® FPGA のサイト(ダウンロード)から入手できます。

手順

- DDR4 SDRAM インターフェースのサポート状況の確認

- DDR4 SDRAM コントローラー IP の設定

- ファンクション・シミュレーションの実行

- Example Design のコンパイル

- 実機動作確認

1. DDR4 SDRAM インターフェースのサポート状況の確認

DDR4 SDRAM インターフェースのサポート状況は、『Altera® FPGA に外部メモリー・コントローラーを実装!』でも紹介している通り、外部メモリー・インターフェース・スペック・エスティメーター で確認することができます。

外部メモリー・インターフェース・スペック・エスティメーターに条件を入れていきます。今回の検証で使用する Altera® Arria® 10 GX FPGA 開発キット に実装されている Arria® 10 (型番:10AX115S2F45I1SG)やメモリー、ボードの仕様など「検索条件と項目を決定」ボタンをクリックして、下記条件を入れてみます。

- ファミリー:Arria® 10 GX and GT

- 温度範囲 & スピード・グレード:インダストリアル温度範囲 (I)、-1

- インターフェースの種類:ハード

- メモリー規格:DDR4

- メモリー・トポロジー & ランク:コンポーネント、UDIMM

検索結果は、以下の通りとなりました。型番の後半部分の I1 が、温度範囲 & スピード・グレードを表しています。

この結果から、コンポーネント(メモリー・デバイス)であっても、チップ・セレクトが 1/2/4 でメモリー・インターフェースの最大周波数の上限が異なっていることがわかると思います。また、UDIMM (Unbuffered DIMM) でも、シングル・ランク/デュアル・ランクで最大周波数の上限が異なっています。

それでは、Altera® Quartus® Prime 開発ソフトウェアを使用して、実際にコントローラーを生成してみましょう!

2. DDR4 SDRAM コントローラー IP の設定

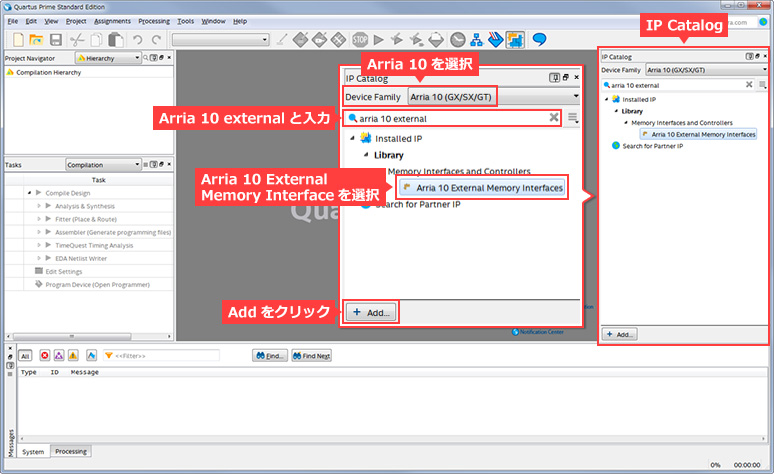

Quartus® Prime を起動して、IP Catalog の検索バーに Arria® 10 External... まで入力すると、Arria® 10 External Memory Interfaces を容易に検索できます。(Quartus® Prime の Standard Edition はプロジェクトを開いていない状態でも作業できますが、Pro Edition はプロジェクトを開いていないと作業できません。)

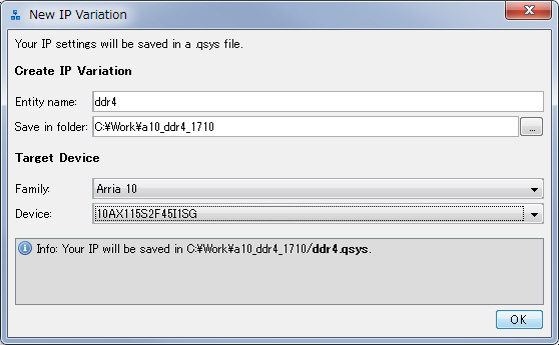

Add をクリックすると、IP Parameter Editor が起動して、名称やターゲット・デバイスを入力する画面が開きます。ここでは以下のようにします。ターゲット・デバイスは、Arria® 10 GX FPGA 開発キットに実装されているデバイスです。

- Entity name: ddr4

- Save in folder: C:\Work\a10_ddr4_1710

- Family: Arria® 10

- Device: 10AX115S2F45I1SG

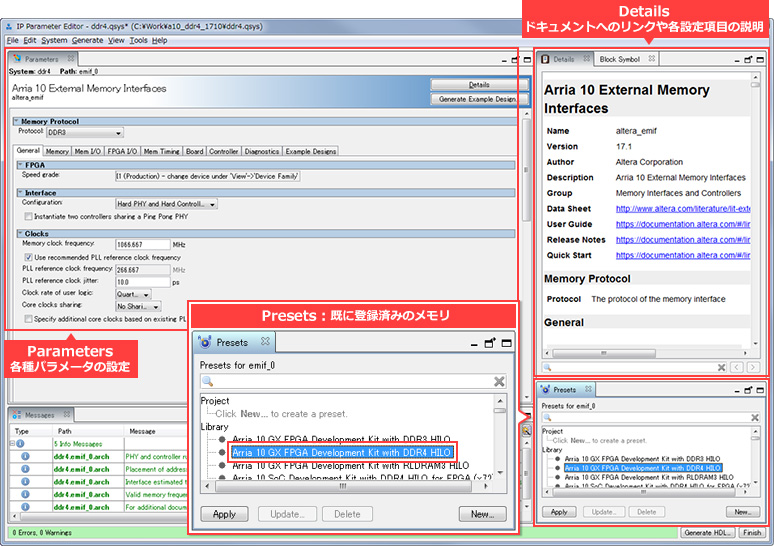

OK をクリックすると、IP Parameter Editor が表示されます。必要な設定をしていきましょう!

中央の Parameters は、各種必要な設定をしていくエリアとなっていて、右上の Details にはドキュメントへのリンクが貼られていたり、各設定項目の説明が書かれています。

Presets には、あらかじめ代表的なメモリが登録されています。Arria® 10 GX FPGA 開発キットで動作確認するには、開発キットに同梱されている DDR4 ドーター・カード(Arria® 10 GX FPGA Development Kit with DDR4 HILO)を使用するので、それを選択して Apply をクリックします。すると、大部分のメモリーのパラメーター設定が自動で反映されます。

それでは、Parameters 内の各タブで、今回の動作確認をする上で必要な設定をしていきます。その他の設定はデフォルトのままとします。各設定の詳細説明は、先ほど触れた Details を確認してください。

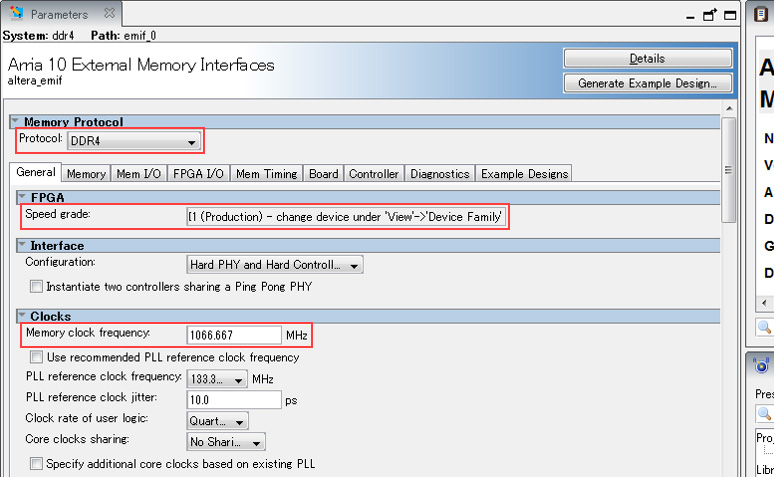

General タブ

Protocol が DDR4 になっていることを確認してください。これは、先ほどの Presets で自動反映されているはずです。

次に、Speed Grade(FPGA のスピード・グレード)が I1 になっていることを確認してください。これは、先ほどのコントローラーの名称と同時にターゲット・デバイスを選択しましたが、その情報が自動反映されているはずです。

他の設定はデフォルトのままとします。ちなみに、メモリー・インターフェースの周波数は 1066.667MHz です。

Memory タブ

デフォルトのままとします。

Mem I/O タブ

デフォルトのままとします。

FPGA I/O タブ

デフォルトのままとします。

Mem Timing タブ

デフォルトのままとします。

Board タブ

デフォルトのままとします。

Controller タブ

デフォルトのままとします。

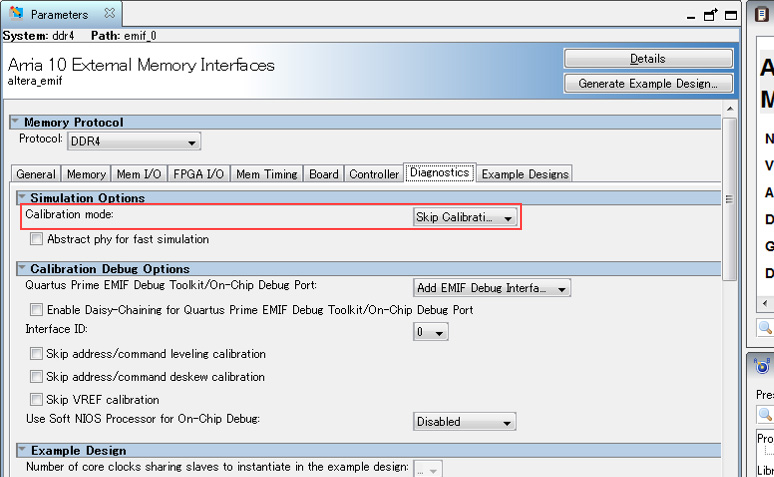

Diagnostics タブ

Simulation Options - Calibration mode

この設定はシミュレーションのみ有効で、実機動作には影響しません。

DDR4 SDRAM インターフェースは、電源オン後すぐにリード/ライトできる訳ではなく、初めにイニシャライズやキャリブレーションなどがおこなわれます。詳しい説明はここでは省略しますが、これらのステップを踏まないとリード/ライトなどのアクセスができません。

このキャリブレーションをシミュレーションではスキップさせることができます。もちろん、フルでキャリブレーションの動きをシミュレーションで確認することもできますが、構成によっては相当な時間が掛かります。

- Skip calibration:キャリブレーションをスキップ

- Full calibration:キャリブレーションを省略することなく実行

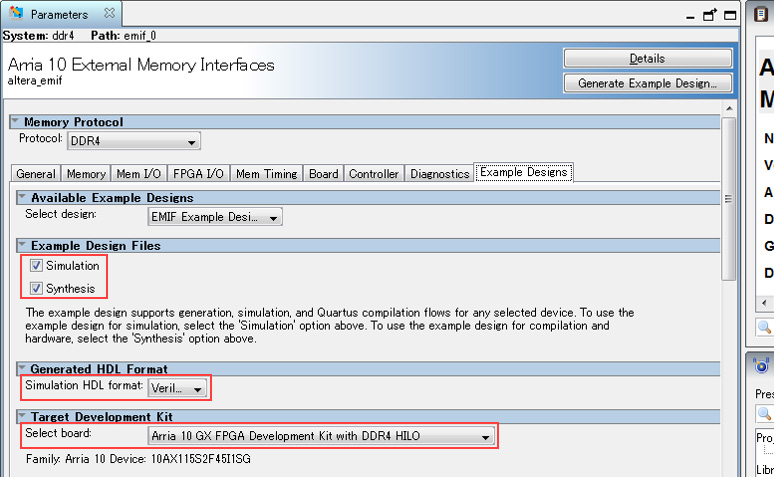

Example Designs タブ

Example Design Files

- Simulation

Example Design でシミュレーションする場合は、チェックを入れてください。 - Synthesis

Example Design で実機確認する場合は、チェックを入れてください。

Generated HDL Format - Simulation HDL format

シミュレーションをおこなう HDL を選択します。

Target Development Kit - Select board

ターゲットのボードを選択します。ただし、前述の Presets のところで Arria® 10 GX FPGA 開発キットに同梱されている Arria® 10 GX FPGA Development Kit with DDR4 HILO を使用する設定をしているので、それが選択されているはずです。

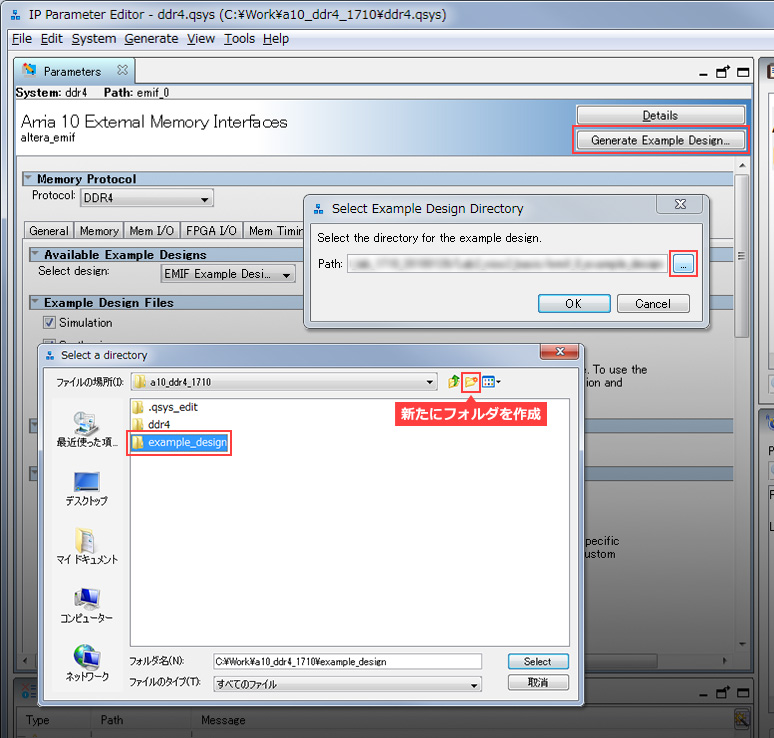

設定が終わったら、この設定を保存します。IP Parameter Editor の File メニュー ⇒ Save As を選択して、ここでは ddr4.qsys という名前で保存します。

次に、Example Designを生成します。Generate Example Design をクリックして、Example Design を生成する場所を指定したら、Generate をクリックします。今回は C:\Work\a10_ddr4_1710\example_design を生成場所として指定しました。

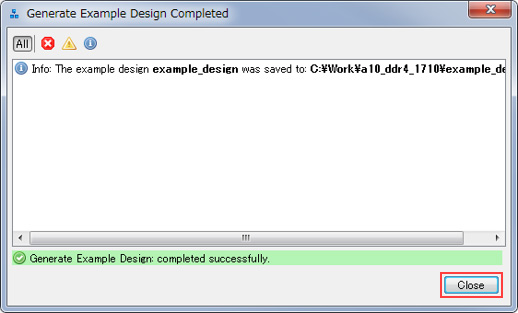

Example Design の生成には数分掛かります。正常に生成できたら以下のウィンドウが表示されるので、Close をクリックします。

今回は Example Design による動作確認を行うので、コントローラーの生成はおこないません。皆さんの FPGA デザインにコントローラー実装する予定であれば、コントローラーの生成をおこなってください。

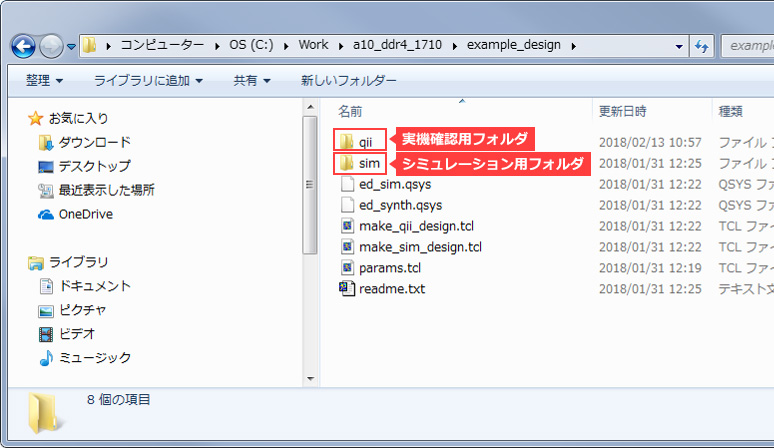

Example Design が生成されると、qii フォルダーと sim フォルダーなどが生成されます。

3. ファンクション・シミュレーションの実行

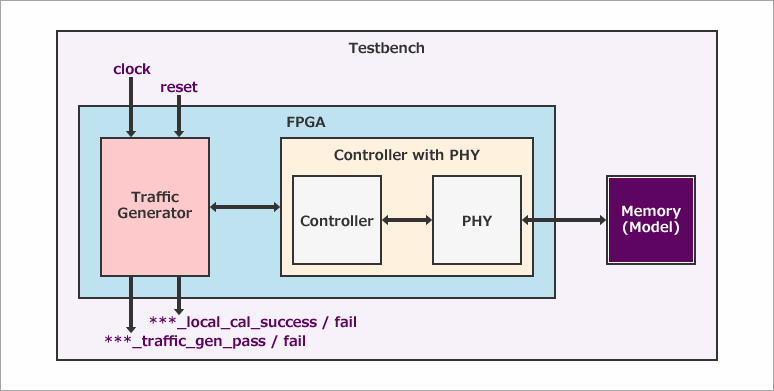

ファンクション・シミュレーションを実行してみます。シミュレーションを実行するために必要なファイル(シミュレーション用プロジェクトやテストベンチ、トラフィック・ジェネレーター、メモリー・モデルなど)も、コントローラーの生成時に自動で生成されるので、手間を掛けずにシミュレーションできます。

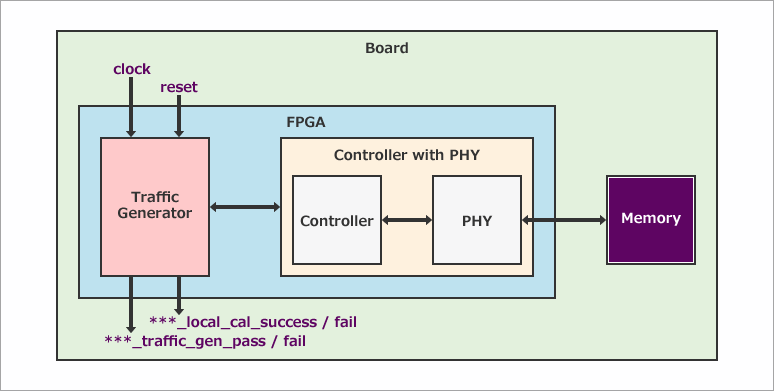

シミュレーションの簡単な動きを説明すると、クロックの供給を受けているトラフィック・ジェネレーターからメモリー・コントローラーへアドレスやコマンド、データが送られ、PHY を介してメモリーへライトされます。その後、メモリーからリードされたデータがライトしたデータと比較されます。一致していれば Success = High、一致していなければ Fail = High となります。

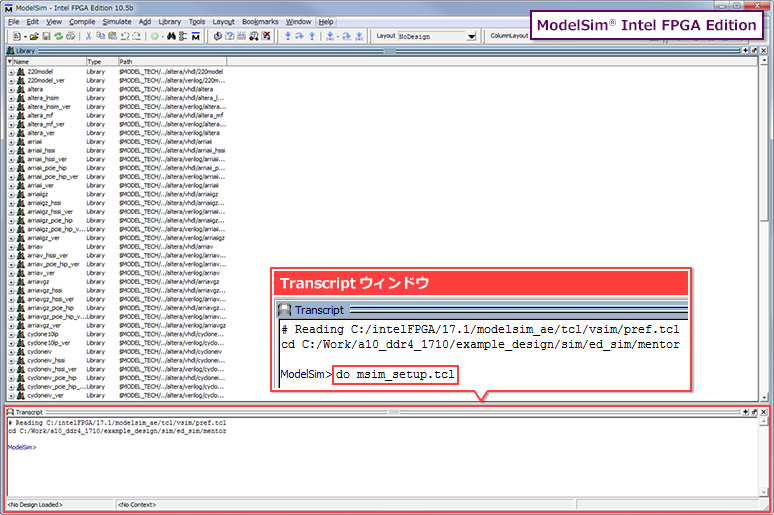

今回は、ModelSim® - Altera® FPGA Edition を使用してシミュレーションしてみます。

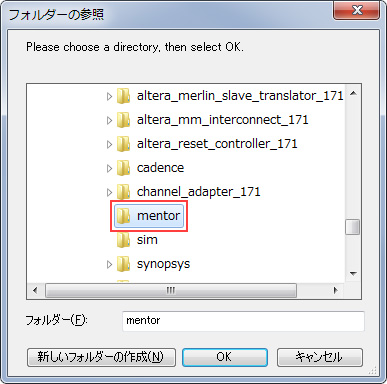

ModelSim® - Altera® FPGA Edition を起動したら、File メニュー ⇒ Change Directory を選択して、作業ディレクトリーを指定します。今回は C:\Work\a10_ddr4_1710\example_design\sim\ed_sim\mentor を指定します。ModelSim® は Mentor Graphics® 社のシミュレーターなので、mentor フォルダーを指定します。

次に、ModelSim® - Altera® FPGA Edition の Transcript ウィンドウに、以下の順にコマンドを実行します。

- do msim_setup.tcl (シミュレーション用スクリプトを実行)

- ld_debug (ライブラリーをコンパイル/デザイン・ファイルをコンパイル/デザインをロード)

- add wave "ed_sim/*" (wave ウィンドウに信号を取り込み)

- run -all (シミュレーションを実行)

PC スペック依存ではありますが、この構成では、ModelSim® - Altera® FPGA Edition によるシミュレーション完了まで 30分程度掛かりました。(ちなみに、Questa® Prime/Core では 4分程度で終わりました。)

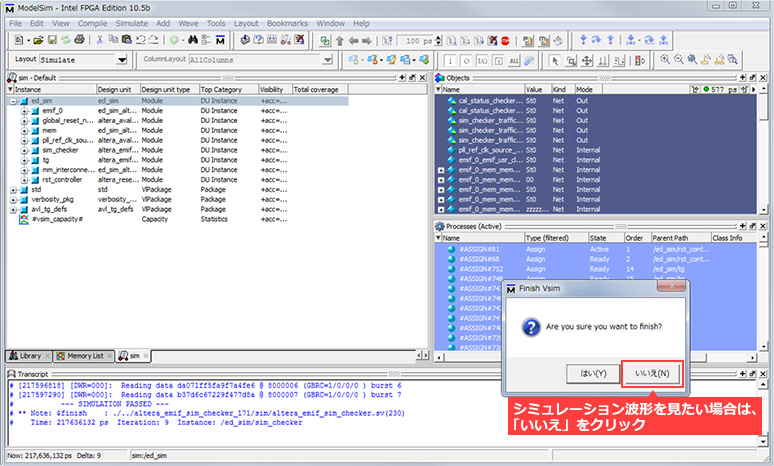

シミュレーションが終わったら、自動で停止します。シミュレーションが完了して波形を確認したい時は、いいえ をクリックしてください。(はい をクリックすると、ModelSim® - Altera® FPGA Edition が閉じてしまうので、注意してください。)

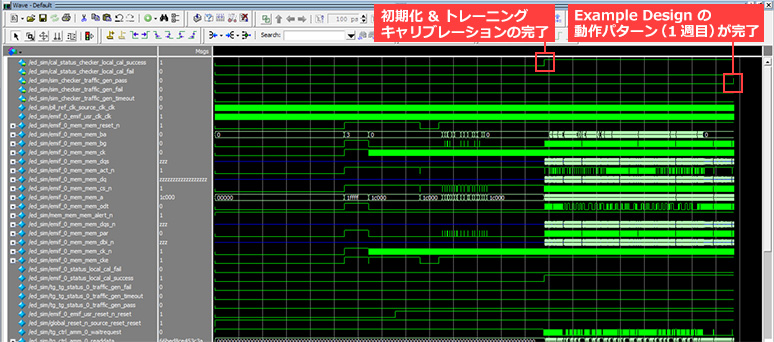

シミュレーション波形を見ると、途中のキャリブレーションが完了した時点で ***_local_cal_success が High になっていることが確認できます。Skip Calibration でのシミュレーションではキャリブレーションの波形は省略されています。

また、***_traffic_gen_pass が High になった時点で、シミュレーションが完了しています。Example Design ではライト/リードしてコンペアする動作を繰り返しますが、シミュレーションでは 1週目が終わったら終了するようになっています。ただし、実機確認ではこれがずっと続くので、ロング・ランのテストにも使用できます。

4. Example Design のコンパイル

続いて、Example Design をコンパイルする準備をします。下図は Example Design のブロック図です。

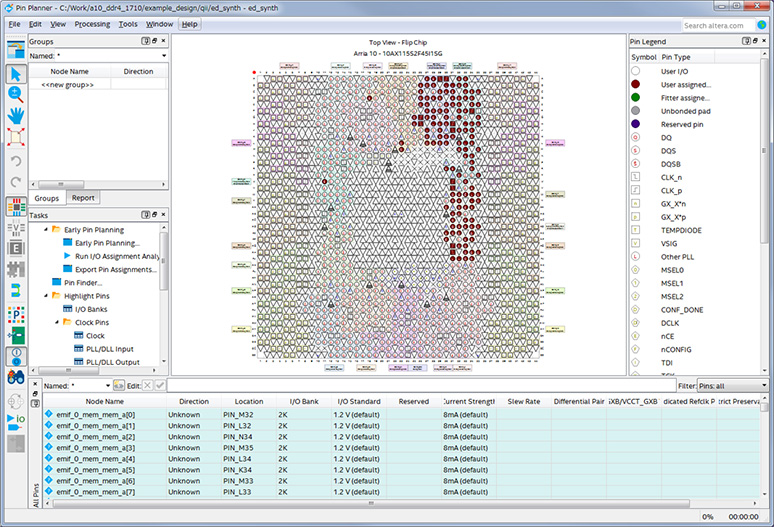

コンパイルするには各種設定や制約、ピン・アサインが必要ですが、Arria® 10 GX FPGA 開発キット 向けに生成した Example Design は、各種設定や制約、ピン・アサインが既にされています。念のため、Pin Planner を見てみましょう。Quartus® Prime の Assignments メニュー ⇒ Pin Planner を選択してください。

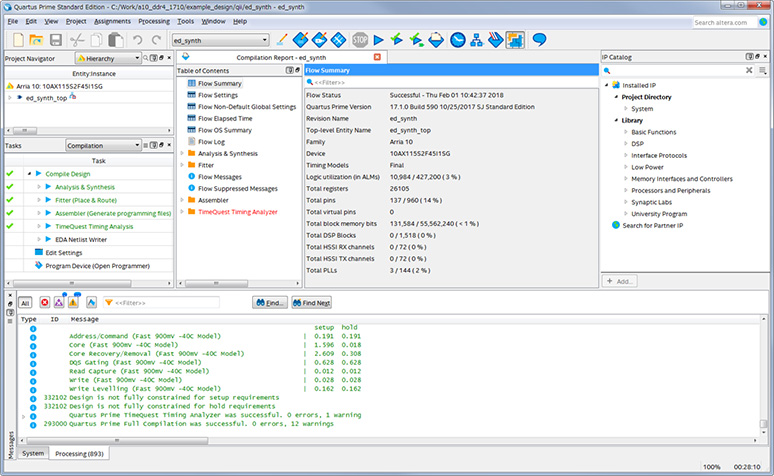

実際に、コンパイルしてみます。Quartus® Prime の Processing メニュー ⇒ Start Compilation を選択してください。

正常にコンパイルは終了しましたか?

<補足>

タイミング解析結果(コンパイル・レポートの TimeQuest Timing Analyzer)が赤字になっています。これは、すべてのピンに対してタイミング制約をしていない事に起因しています。しかし、未制約ピンはリセットや JTAG 関連、LED に出力するピンであるため、今回はこのまま進めることにします。

もし、Setup や Hold でタイミング違反が起きている場合は、コンパイルの設定を変更してみましょう。Quartus® Prime の Assignments メニュー ⇒ Settings ⇒ Compiler Settings ⇒ Optimization mode で Performance に設定します。この設定はパフォーマンス重視のコンパイルを目指すものなので、タイミングに関しては改善する傾向にありますが、リソースを多く消費するケースがあります。

5. 開発キットを使用して動作確認

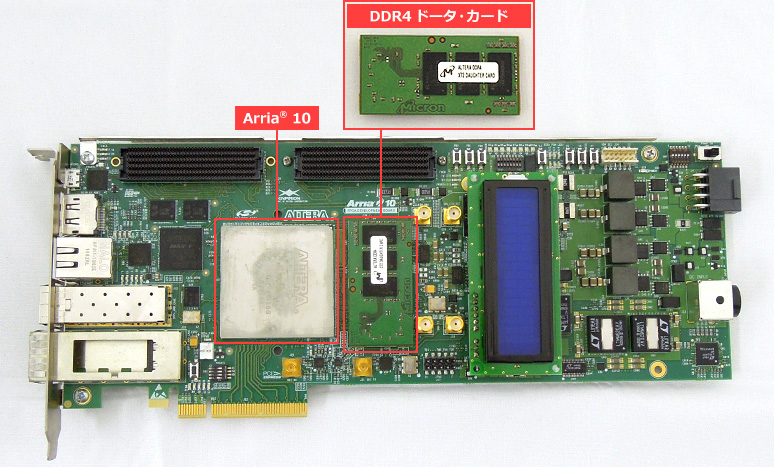

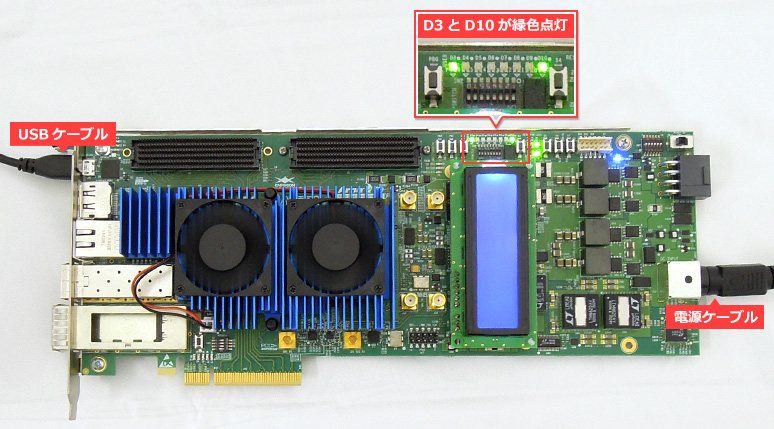

コンパイルが完了したら、コンパイルで生成された SOF ファイルを Arria® 10 デバイスへ書き込みます。開発キットと PC 間を USB ケーブル(開発キット側:USB Micro-B)で接続し、電源を投入します。

<補足>

Altera® FPGA には、JTAG ポートが備わっています。この JTAG ポートからAltera® FPGA ダウンロード・ケーブルを介して、データを書き込みます。

通常はAltera® FPGA ダウンロード・ケーブル(USB-Blaster™ や USB-Blaster™ II など)を使用しますが、Arria® 10 GX FPGA 開発キットは Blaster の機能がボード上に実装されているため、別途ダウンロード・ケーブルを用意する必要はなく、USB ケーブルだけでデータ書き込みができます。

開発キットの中央に、同梱されている DDR4 ドーター・カードを実装してください。

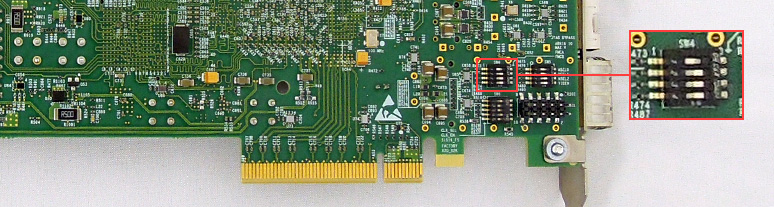

また、JTAG チェーンの 設定(裏面の DIP スイッチ/SW4)も確認してください。

- 1:OFF (左側)

- 2:ON (右側)

- 3:ON (右側)

- 4:ON (右側)

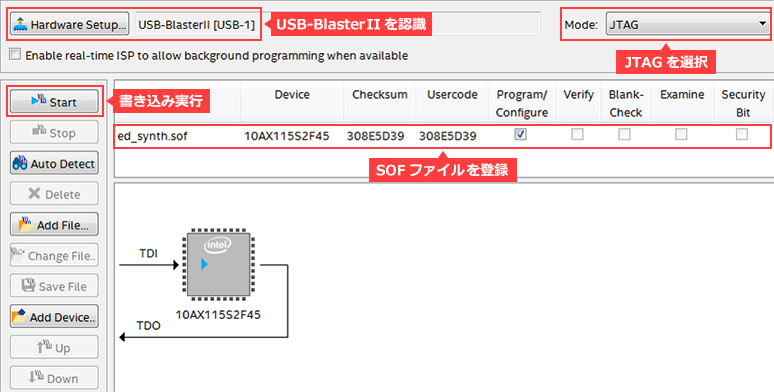

次に、Quartus® Prime の Tools メニュー ⇒ Programmer を選択して、Quartus® Prime Programmer を起動します。

Programmer が起動して、書き込み用の SOF ファイルが自動で登録されていれば、Hardware Setup と Mode が選択されていることを確認してから、Start をクリックして書き込みを実行します。

もし Programmer に SOF ファイルが登録されていない場合、ダウンロード・ケーブルやモード、書き込みファイルを以下のように設定してから、Start をクリックして書き込みを実行します。

- Hardware Setup:USB-Blaster™ II(USB-Blaster™ II のドライバをインストールしていないと、選択できません) ⇒ USB-Blaster™ II のドライバのインストール方法

- Mode:JTAG

- Add File:コンパイル時に生成された SOF ファイル(ファイル名:ed_synth.sof)

SOF ファイルの書き込みが終わったら、実際に Example Design が動作します。正常に動作していれば、緑色の LED が点灯しているはずです。

LED は下表の通りに割り当てられています。これらのピン・アサインも、開発キット用の Example Design では自動でアサインされています。

| ピン名 | LED | 説 明 |

| ***_status_local_cal_success | D3 緑 | メモリーの初期化(イニシャライズ)やトレーニング、キャリブレーションが正常に完了すると High にアサートされます。コントローラーがメモリー・インターフェースを使用する準備ができていることを示しています。 |

| ***_status_local_cal_fail | D3 赤 | メモリーの初期化(イニシャライズ)やトレーニング、キャリブレーションに失敗すると High にアサートされます。 |

| ***_tg_0_traffic_gen_pass | D10 緑 | Example Design によるメモリーへのライト/リードの動作確認パターンの 1周目が完了(正常)すると、High にアサートされます。 シミュレーションでは 1周で停止しますが、動作確認用 Example Design では動作確認パターンを繰り返します。 |

| ***_tg_0_traffic_gen_fail | D10 赤 | Example Design によるメモリへのライト/リードの動作確認パターンの 1周目が完了(失敗)すると、High にアサートされます。 シミュレーションでは 1周で停止しますが、動作確認用 Example Design では動作確認パターンを繰り返します。 |

| ***_tg_0_traffic_gen_timeout | D7 緑 | Example Design によるメモリーへのライト/リードの動作確認パターンでタイム・アウトすると、High にアサートされます。 |

また、Signal Tap ロジック・アナライザー 機能を利用すれば、FPGA 内部信号をモニターすることもできます。これについては、別の機会に紹介したいと思います。

おすすめ記事/資料はこちら

FPGA の EMIF デザイン & デバッグ・ガイドライン

Altera® FPGA に外部メモリ・コントローラを実装!

Altera® FPGA の開発フロー/トップページ

おすすめ FAQ はこちら

商品の購入はこちら

メーカーサイト/その他関連リンク

外部メモリー・インターフェース (Altera®のサイト)