※ ModelSim は新規販売を終了しました。

HDL(ハードウェア記述言語)で設計された FPGA やカスタム IC などの機能的な検証(Function Simulation)を行うためのシミュレーターで、高いパフォーマンスや最先端の検証、デバッグ機能を持っています。

▶ 紹介動画

▶ 論理シミュレーターの紹介

▶ デバッグ機能の紹介 ( アサーション・ベース検証 / コード・カバレッジ / 波形比較 / 拡張データフロー )

▶ 関連情報

▶ セミナー/ワークショップ

▶ お問い合わせ

紹介動画

論理シミュレーターの紹介

Questa Sim と ModelSim は、ワールド・ワイドで広く使用されている論理シミュレーターです。Verilog や SystemVerilog、VHDL といったハードウェア記述言語(HDL)をサポートし、これらの混在シミュレーションも可能です。

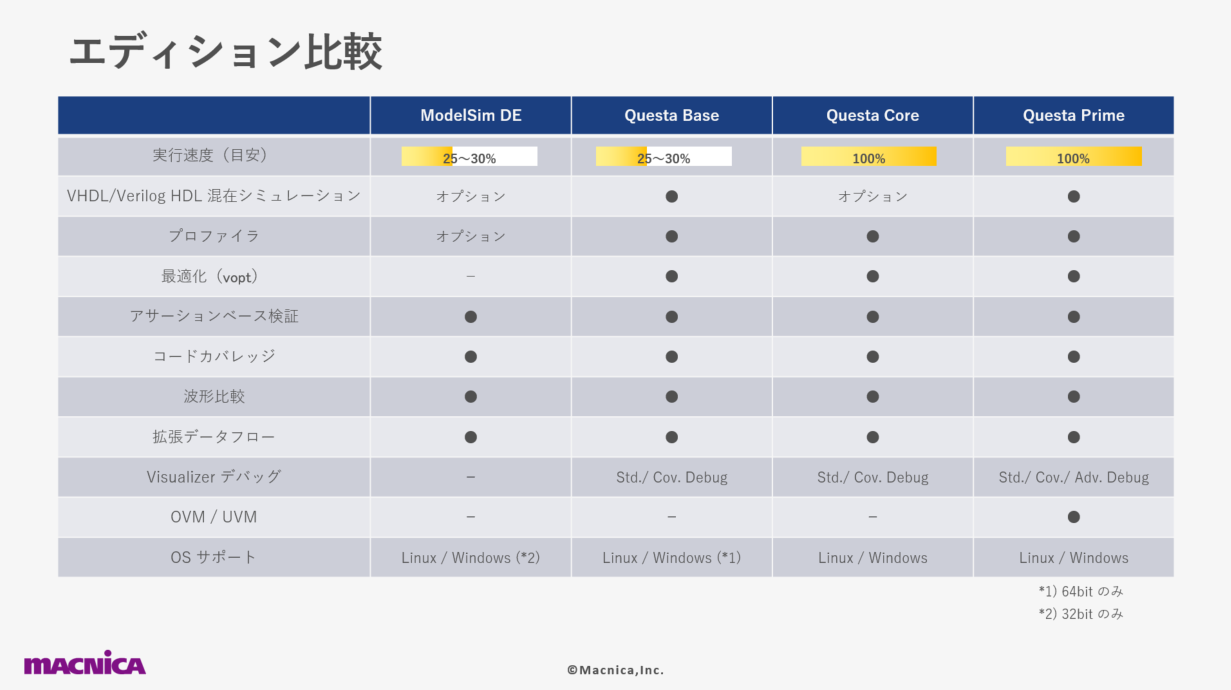

製品(エディション)の比較

エディションによって、シミュレーション速度や搭載されているデバッグ機能が異なります。最近の FPGA デザインは大規模化しているので、機能シミュレーション以外のデバッグ機能が、とても好評です。

デバッグ機能の紹介

Questa Sim および ModelSim の各機能は、こちらで紹介しております。

(↓画像をクリックすると、次ページへジャンプします。)

アサーション・ベース検証

回路内部にアサーションを配置することにより、期待にそぐわない動作がないかを自動で監視します。

コード・カバレッジ

シミュレーションでトグルしていない HDL 記述を検出します。テストベンチがカバーしていない個所や入力条件を検出します。

関連情報

▶ Siemens EDA ツールのダウンロード方法

▶ Questa / ModelSim のインストール方法

▶ Siemens EDA ツールのライセンス設定方法

セミナー/ワークショップ

Questa Advanced Simulator 新デバッグ環境 Visualizer の使用方法

▶ Siemens EDA セミナー

お問い合わせ

メーカー情報 Top へ

メーカー情報 Top ページへ戻りたい方は、以下をクリックください。

シーメンス(Siemens)が所有する商標や登録商標:こちら