検証に便利な機能を豊富に備えており、その検証機能の1つである波形比較についてご紹介します。

波形比較

波形比較の機能

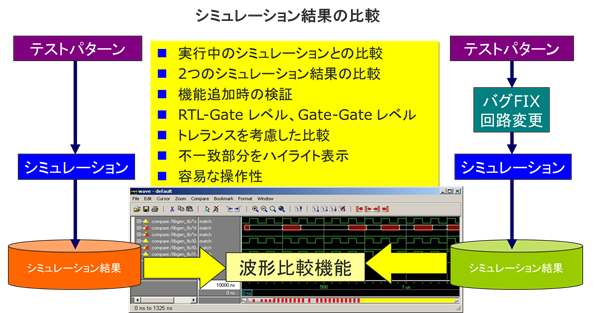

波形比較機能では、2つのシミュレーション結果を比較することができます。

例えば、バグ FIX などによる回路変更後と変更前のシミュレーション結果を比較し、修正による動作の影響を確認することができます。波形比較機能では、シミュレーション結果の不一致箇所をハイライト表示させ、容易に判断することができるようになっています。

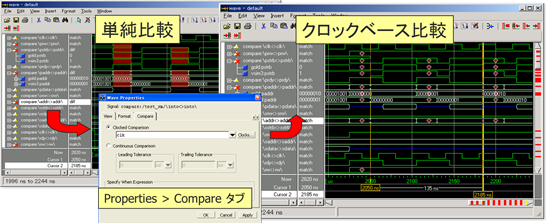

(1)2種類の比較モードをサポート

● 単純比較

選択した信号の変化時にその信号の値を比較します。信号にトレランス(許容誤差)時間を与えて幅を持たせたり、Enable 時だけ波形比較する等の比較条件を設定することができます。

● クロック・ベース比較

基準クロックのエッジに合わせて比較します。基準クロックにオフセット時間を与えることができます。

(2)階層間や信号名が異なる信号波形を比較可能

「階層的な RTL デザイン」と「論理合成されたフラットなデザイン」を比べると、階層や信号名の不一致やバスが分割されるので単純に波形を比較できませんが、Questa Sim / ModelSim の波形比較は、比較対象となる基準デザインの階層変更、信号名追加、分解されたバス信号の自動再構築を行えます。

(3)比較する信号強度のマッチング・ルールを設定可能

マッチ条件には、“0”、“1”、“X”、“Z” の4種類ありますが、そのマッチする信号強度を各々に設定できます。

比較結果の表示

下記に単純比較での比較結果の例を表示を示します。

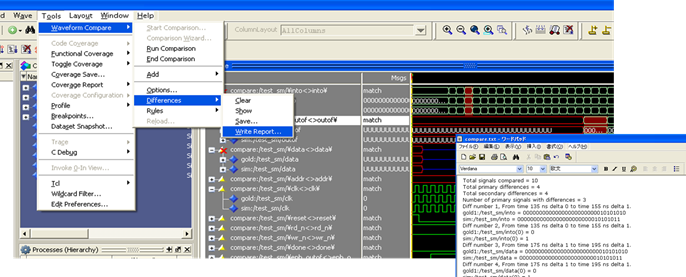

波形比較のレポート出力

比較結果をファイルに出力することができます。下記は、不一致情報をテキストに保存する場合の例になります。

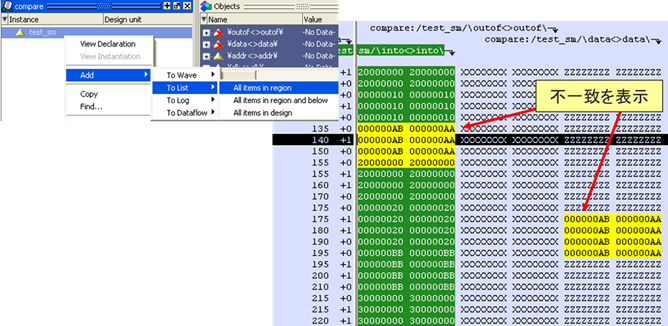

リスト・ウィンドウに比較結果を表示

リスト・ウィンドウに不一致を表示することで、テキスト出力同様に詳細な比較ができます。下記は、不一致情報をリスト・ウィンドウに表示させた場合の例になります。

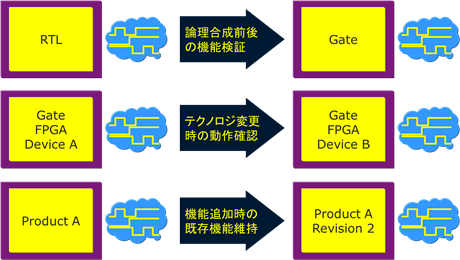

波形比較が有効な検証

波形比較が有効な検証は、次のようなものになります。

① RTL と Gate の比較

使用例:論理合成後のネットリストや手修正したネットリストと、元の RTL との論理比較を行えます。テスト用回路の削除、回路面積の縮小、パフォーマンス向上、見やすさ等のために RTL を手修正した際に使用されると便利です。

② テクノロジーを変更した場合などの Gate to Gate の等価性検証

使用例:試作用の FPGA ネットリストと量産用の ASIC ネットリストの論理比較、他社 FPGA デザインから インテル FPGA デザインへ変更した際の論理比較に利用できます。

③ 回路機能を変更した際の以前の機能の維持の確認

使用例:影響しない信号は変わらないとの先入観から目視確認はバグを見落とすケースが多くなります。回路修正に影響しない信号が他に影響がないことを「波形比較」を使って確認できます。

関連情報

セミナー/ワークショップ

▶ [オンラインセミナー] ModelSim によるアサーション検証 <無料>

Questa Sim / ModelSim のデバッグ機能であるアサーションベース検証(ABV)やコード・カバレッジ、拡張データフローの効果を紹介するセミナーです。特に、アサーションベース検証は FPGA デザインの半数以上で活用されているお勧めの検証手法です。

▶ 関連のイベント・セミナー

お問い合わせ

メーカー情報 Top へ

メーカー情報 Top ページへ戻りたい方は、以下をクリックください。

シーメンス(Siemens)が所有する商標や登録商標:こちら