hello.

My name is Intel F. Hanako and I provide technical support for Intel® FPGA products at Macnica.

Here, in Quartus® Prime Standard Edition,

I will show you how to apply the sub-entities placed under the placement constraint by another project.

Notes:

- See this article for an overview of applying placement-constrained subordinate entities to another project.

- Quartus Prime Pro Edition has different specifications and work flow. Please see this article.

Work environment

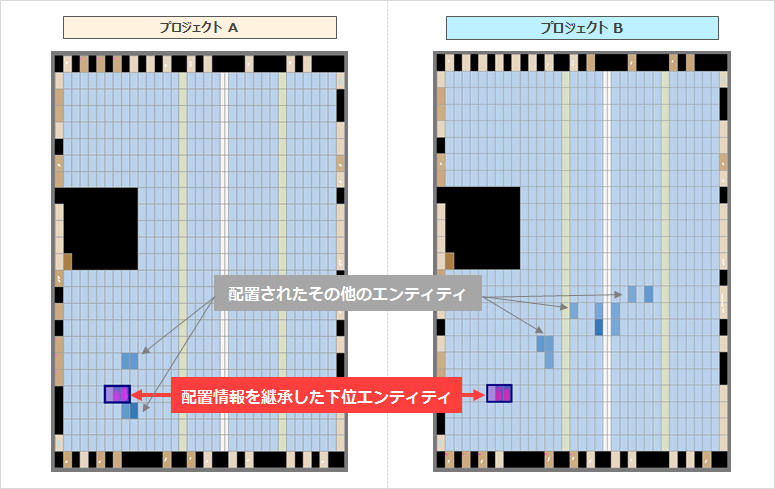

For ease of explanation, we will prepare two projects, called [Project A] and [Project B] respectively.

This flow implements the lower-level entities used in [Project A] in [Project B].

At that time, the device model number and Quartus Prime Standard Edition environment must be as follows.

|

Project A |

Project B. |

|

| FPGA |

same model number |

|

|

Quartus Prime Standard Edition |

Same version (including build number) |

|

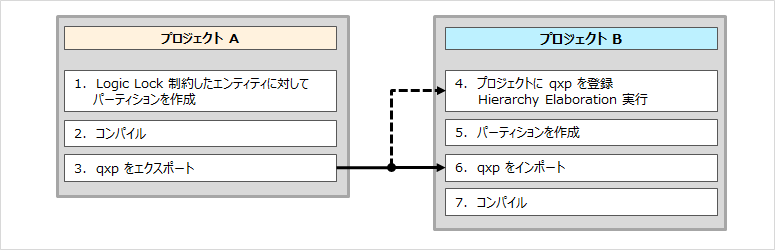

work flow

The figure below is a flowchart of the work in the Standard Edition.

Export the netlist file qxp for the lower entity partition and reuse it in another project.

Now, I will guide you through this flow in detail using the Quartus Prime Standard Edition menu.

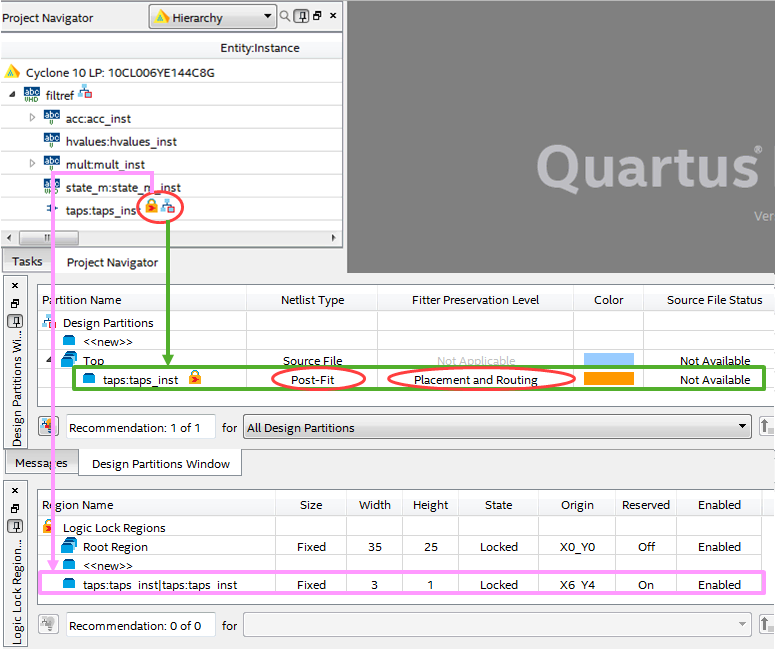

1. [Project A] Create partitions on subentities constrained by Logic Lock

Create a partition on the subordinate entity that has Logic Lock.

(For instructions on how to create a Logic Lock region, see "Creating a Logic Lock Region" in this article.)

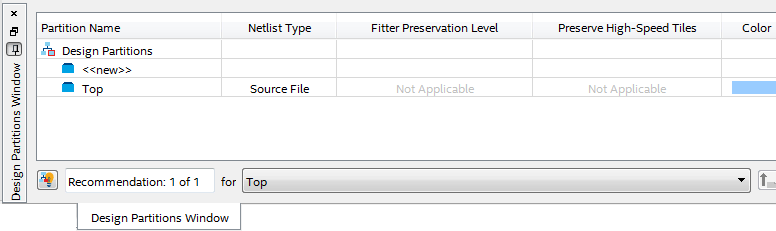

1. Display the Design Partitions Window (Assignments menu) for creating partitions.

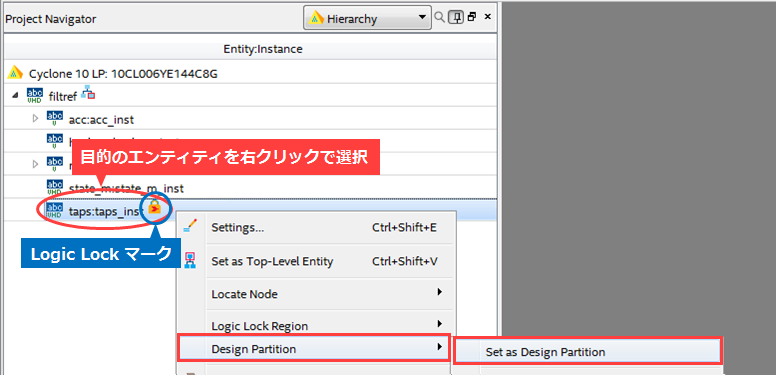

2. From the Project Navigator window, right-click and select the entity you want to partition and select

Select Design Partition > Set as Design Partition.

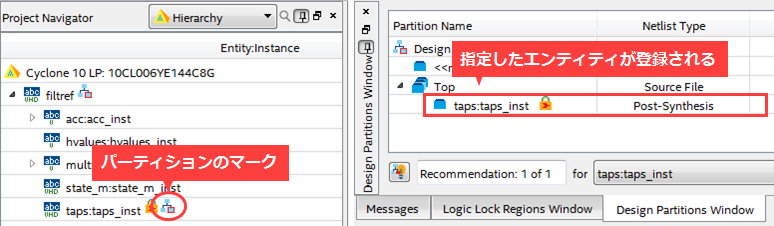

Confirm that the specified entity is registered in the Design Partitions Window and marked on the Project Navigator window.

The specified "entity name: instance name" is used as the partition name by default.

You can also change it with Rename (right-click menu).

2. [Project A] Execute Compile/Check Compilation Results

Constraints such as pin assignments, timing constraints, and options as necessary

Compile (Processing menu > Start Compilation) to take into account Logic Lock's layout constraints.

Compile reports, Chip Planner, and Timing Analyzer are used to verify compilation results and confirm whether project A specifications are satisfied.

If it does not meet your requirements, add constraints such as options and timing and recompile.

At that time, by adopting Rapid Recompile and incremental compilation (Pro Edition is incremental optimization)

It is possible to reduce the time required for recompilation.

To generate a netlist that inherits the placement information for the created partition

Set the Netilist Type to Post-Fit and the Fitter Preservation Level to the desired level and compile again.

関連情報:

Quartus Prime had this method to reduce compilation time

3. [Project A] Generate qxp files for subordinate entities

Generate a partition file qxp for that entity.

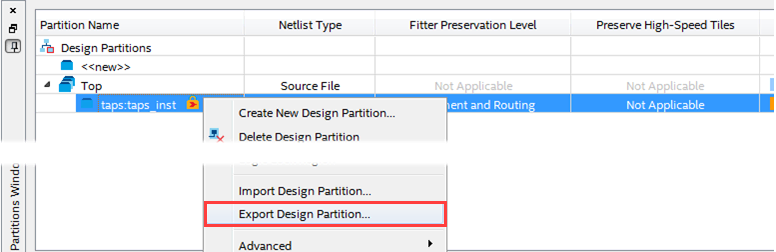

1. Right-click on the appropriate entity in the Design Partitions Window and select Export Design Partition.

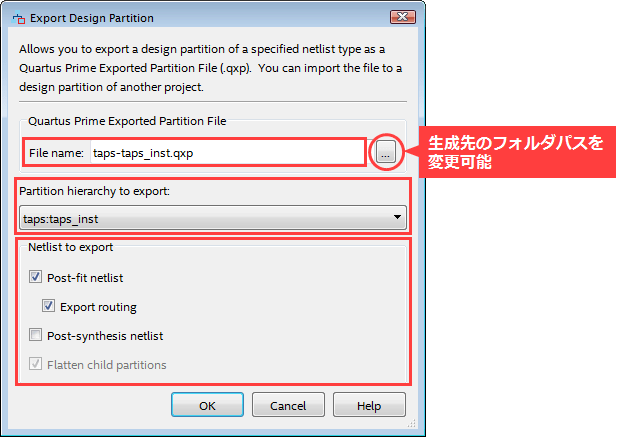

2. The Export Design Partition dialog Box will appear.

Make settings for qxp files.

| File name | Specifies the file name of the generated qxp. (default is ”partition_name”.qxp) |

| Partition hierarchy to export | Make sure the specified partition name is selected. |

| Netlist to export | Select the information to record in the qxp file. [Post-fit netlist] Generate a post-placement netlist. If you also want to add routing information, apply the [Export routing] option. [Post-synthesis netlist] Generate a netlist after logic synthesis. If both Post-fit netlist and Post-synthesis netlist are checked (On), the Netlist Type of the partition becomes selectable in the destination project. |

In this case, the purpose is to transfer the placement information of the lower entity to another project as it is.

Netlist to export selects Post-fit netlist.

Apply Export routing as needed.

Click the OK button to generate the qxp.

This concludes the work on Project A. Next, let's apply the qxp of the corresponding entity to Project B.

4. [Project B] Register qxp in the project and execute Hierarchy Elaboration

1. In the reuse destination project B, the object to compile the lower module is the qxp file exported in project A.

Therefore, it is registered in the project in the same way as the design file created by the user.

■ When creating a new project

⇒ In Add Files of New Project Wizard, instead of HDL source of lower entity,

Select the qxp file generated in Project A.

■ If the project already exists

⇒ In Add/Remove Files in Project (Project menu), remove the HDL source of the subentity.

Add the qxp file generated in project A.

2. Perform Hierarchy Elaboration to create a database of hierarchical relationships for each entity.

- Processing Menu > Start > Start Hierarchy Elaboration

5. [Project B] Create a partition on the subordinate entity

1. Display the Design Partitions Window (Assignments menu).

2. From the Project Navigator window, select the entity to which you want to apply the partition file.

Right-click > Design Partition > Select Set as Design Partition.

The specified entity is registered in the Design Partitions Window and a partition mark is added on the Project Navigator window.

Confirm that

6. Import the qxp file into the [Project B] partition

Import the qxp file into the subordinate entity partition.

1. Right-click on the appropriate entity in the Design Partitions Window and select Import Design Partition.

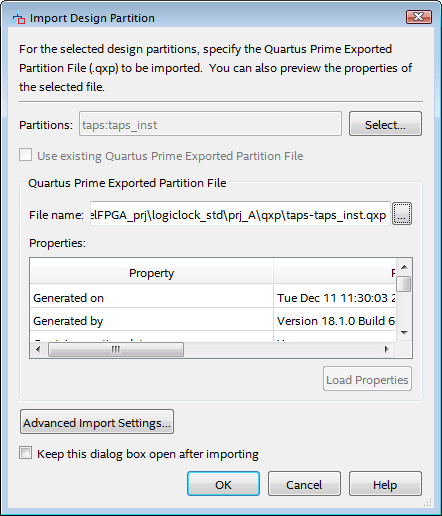

2. The Import Design Partition dialog Box will appear.

- Specify the partition file generated in project A in File name, and click the [OK] button.

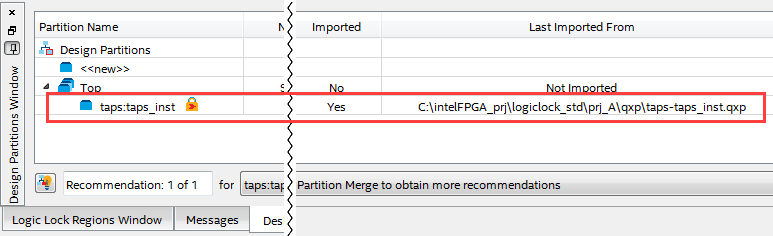

You will see a message that the import was successful and you will see the following in the Design Partitions Window:

- Imported term = Yes

- Last Imported From term = Path of the registered partition file

Also, you can confirm that the contents set in project A have been registered in the Design Partitions Window and Logic Lock Regions Window.

You can confirm that the imported entity is automatically set with the netlist information specified at the time of export.

In this example, it is registered with Post-Fit/Placement and Routing.

When handing over to Project B, it is also possible to change the Fitter Preservation Level if necessary.

Also, if Project A selected Post-synthesis netlist when exporting, Netlist Type can also be applied.

7. [Project B] Execute Compile/Check Compilation Results

Constraints such as pin assignments, timing constraints, and options as necessary

Execute compilation (Processing menu > Start Compilation).

Compilation report, Chip Planner, and Timing Analyzer are used to verify compilation results.

Verifies that subordinate entity placement information has been applied.

If the project as a whole does not meet your requirements, add constraints such as options and timing and recompile.

At that time, it is possible to reduce the time required for recompilation by adopting Rapid Recompile or incremental compilation.

Click here for recommended articles/materials

How to specify placement of sub-modules in the design

How to recompile only part of the FPGA design

Quartus® Prime has a way to reduce compilation time

Try to use incremental compilation

Intel® FPGA Development Flow/FPGA Top Page

Click here for recommended FAQ

Do MAX 10 devices support incremental compilation?

Is it possible to generate a .qxp (Quartus II Exported Partition) file with Quarus II Web Edition?