こんにちは。

マクニカでインテル® FPGA 製品の技術サポートをしている インテル・F・ハナコ です。

以前、Quartus® Prime で下位エンティティの配置を指定するLogic Lock (ロジック・ロック)を紹介しましたが、今回はその応用編として、Logic Lock で配置指定した下位エンティティを、別のプロジェクトで適用させる方法をご紹介します。

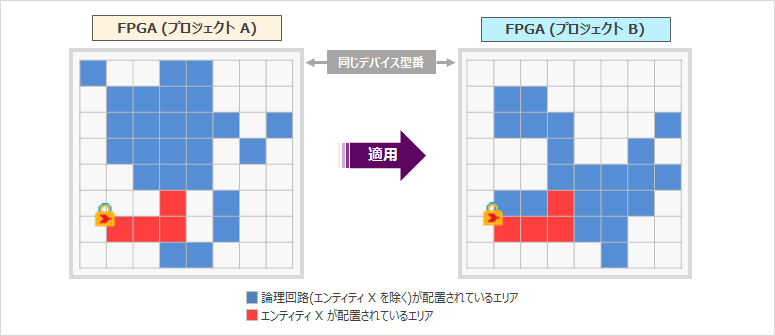

下図は、プロジェクト A で Logic Lock により FPGA に配置したエンティティ X を、プロジェクト B で FPGA にインプリメントした際のイメージ図です。

このように、プロジェクト A の開発段階でエンティティ X に Logic Lock で配置制約を与えておけば、プロジェクト B においても配置状況をそのまま継承することができます。

この方法により、エンティティ X はプロジェクト B でもタイミングを Fix した状態が維持できるため、 プロジェクト Bにおけるデザイン全体のタイミング・クロージャ―の工数軽減が期待できます。

概要

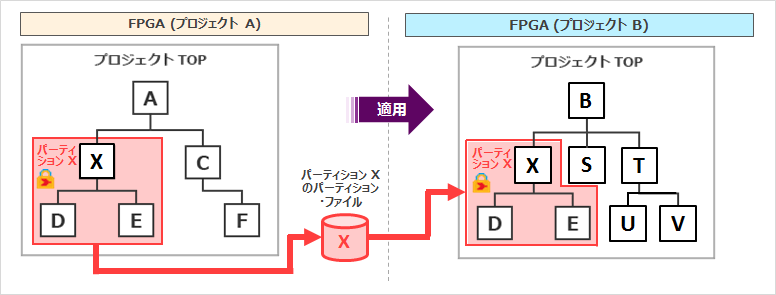

下図は、Logic Lock 設定した下位エンティティを別プロジェクトへ適用させるための作業を、イメージ化したものです。

プロジェクト間で配置制約したエンティティ X のコンパイル結果を継承するには、プロジェクト A の時点でエンティティ X に対して Logic Lock 設定の他に、“パーティション”と言う論理的な枠組みを作成します。その後、プロジェクト A においてコンパイルを実行し制約通りに配置させます。

このコンパイル結果をプロジェクト B に継承するため、エンティティ X の論理回路情報とコンパイル結果を含んだ特殊なファイル“パーティション・ファイル”を生成します。

パーティション・ファイルは、使用する Quartus Prime のエディションによりフォーマットが異なります。

| Quartus Prime Standard Edition | Quartus Prime Exported Partition File (.qxp) |

| Quartus Prime Pro Edition | Quartus Prime Partition Database File (.qdb) |

プロジェクト B では、プロジェクト A で生成したパーティション・ファイルを HDL ソース・ファイルの代わりに使用してコンパイルを実行します。

つまり、このフローを採用したい場合には、プロジェクト A の時点で該当するエンティティにパーティションを作成してコンパイル作業をする必要があります。

各エディションの作業フロー

Quartus Prime のエディションにより作業フローが異なります。

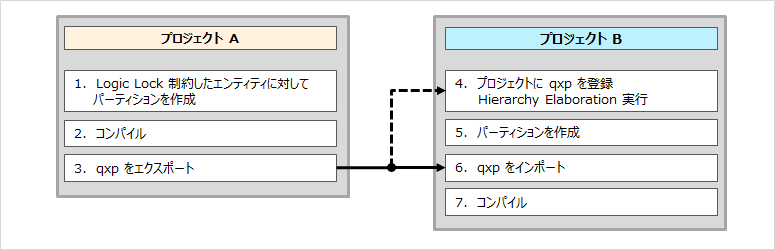

Quartus Prime Standard Edition

下図は、Standard Edition における作業をフローチャート化したものです。下位エンティティのパーティションに対してパーティション・ファイル qxp をエクスポートし、別のプロジェクトで再利用します。

では、このフローを Quartus Prime のメニューでご紹介します。

配置制約した下位エンティティを別プロジェクトへ適用させる方法 (Standard Edition)

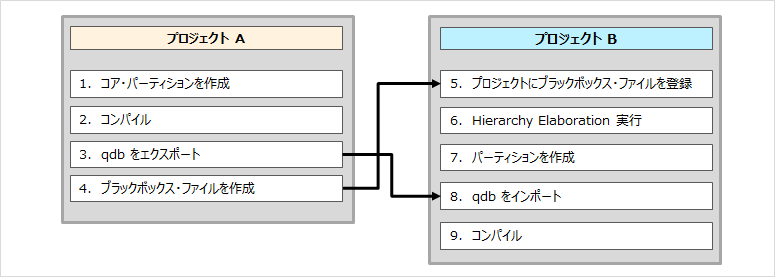

Quartus Prime Pro Edition

Pro Edition には、パーティションの仕様に以下の2パターンがあります。いずれも、パーティションに対してパーティション・データーベース・ファイル qdb をエクスポートし、別のプロジェクトで再利用します。

| コア・パーティション | コア・リソース(LUT、レジスタ、M20Kメモリブロック、およびDSP)のみを含めることができます。 |

| ルート・パーティション | ルート・パーティションには、周辺リソース(I/O、HSSIO、PCIe、PLLを含む)、および関連するコア・リソースが含まれますが、コア・パーティションは今後の開発のために Open のままにします。 |

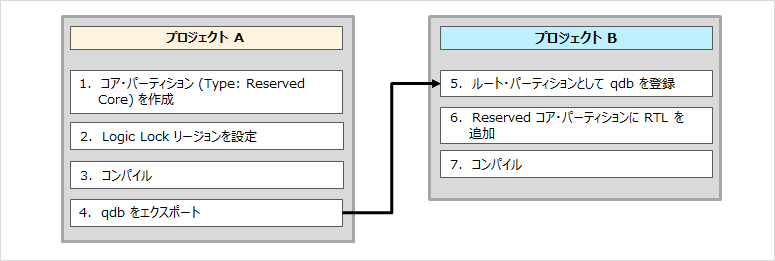

下図は、Pro Edition における作業をフローチャート化したものです。

では、このフローを Quartus Prime のメニューでご紹介します。

配置制約した下位エンティティを別プロジェクトへ適用させる方法 (Pro Edition)

おすすめ記事/資料はこちら

デザインの下位エンティティの配置を指定する方法 (Logic Lock)

Quartus® Prime にはコンパイル時間を短縮させる こんな方法があった

おすすめ FAQ はこちら

MAX 10 デバイスはインクリメンタル・コンパイルをサポートしていますか?

Quarus II Web Edition で.qxp (Quartus II Exported Partition) ファイルを生成することはできますか?