こんにちは。

マクニカでインテル® FPGA 製品の技術サポートをしている インテル・F・ハナコ です。

今回は、Quartus® Prime のコンパイル・テクニック「インクリメンタル・コンパイル」について概要をお話しします。

(インクリメンタル・コンパイルをご存じない方は、まず 「FPGA デザインの一部だけを再コンパイルする方法」 を先にご覧ください。)

インクリメンタル・コンパイルのサポート環境

インクリメンタル・コンパイルが使用できる環境を以下に示します。

| 対応する Quartus Prime |

Quartus Prime Standard Edition |

| 対応する デバイス・ファミリ |

Quartus Prime Standard Edition がサポートするデバイス・ファミリ ※ ただし MAX® V、MAX II を除く ※ Arria 10 の場合は、Quartus® Prime Pro Edition においてインクリメンタル最適化機能(Incremental Optimization)の活用を推奨 |

インクリメンタル・コンパイルが有効な適用例

インクリメンタル・コンパイルは、デザイン・フローのさまざまな場面で適用でき、デザインの生産性向上に役立ちます。例えば、

- ソース・ファイル(特に大規模デザイン、大規模デバイス向け)変更時や最適化オプションを適用時のコンパイル時間を短縮

- 他のロジックを追加する前に、既存デザインの結果を維持

- ファンクション・ブロックごとに担当者が設計し、最終的にトップ・レベルで結合する

- SignalTap® II ロジック・アナライザでのデバッグ時

このようなときに、大きなメリットが得られます。

トップダウン・アプローチ と ボトムアップ・アプローチ、あなたはどっち派?

ユーザーのデザイン構成、つまりプロジェクトの管理方法により、インクリメンタル・コンパイルのアプローチ方法(作業フロー)が異なります。

トップダウン・アプローチ方法

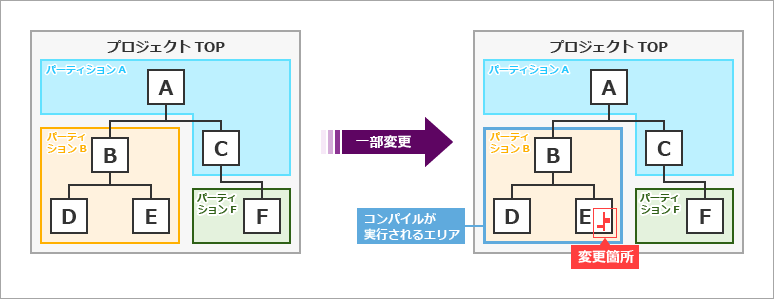

上図は、トップダウンでアプローチするイメージを表しています。

一つのプロジェクト下でデザイン設計を進めながら、変更が必要になったパーティション(モジュール)だけを再コンパイルする手法です。

これにより、以下のメリットがあります。

- 変更のないパーティションは再コンパイルされないので、コンパイル時間を短縮できる

- 変更のないパーティションは最終回のコンパイル結果(論理合成結果あるいは配置配線結果)を引用するため、性能(パフォーマンス)を維持できる

- コンパイル時間の短縮により、タイミングクロージャが必要なパーティションの改善に注力できる

- Quartus Prime の操作フローが簡単!

そのため、インクリメンタル・コンパイル初心者向きの手法と言えます。

また、一つのプロジェクトの中で作業するため、ファイル管理もシンプルです。

ボトムアップ・アプローチ方法

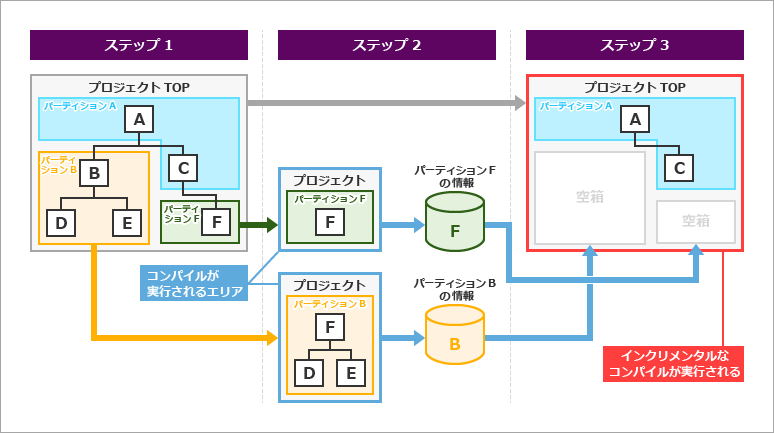

もう一つは、ボトムアップからアプローチする方法です。

デザイン設計の初期段階からモジュールごとに独立してコンパイル作業を進め、各モジュールが完成したら最上位プロジェクトにインポートしていく、まるでパズルを組み立てるような手法です。

この方法には、以下のメリットがあります。

- パーティション(モジュール)ごとにプロジェクトを作成し、個々にコンパイル作業を進めることができるので、未完成のモジュールを待つ必要がない

⇒ 作業のパラレル化により効率 UP!

- 完成した下位の各パーティションは、qxp フォーマット(バイナリ化されたネットリスト)に変換して最上位プロジェクトに統合するので、最上位プロジェクトにおけるデザイン・ファイル管理がシンプルになる

⇒ 例えば、自社開発のモジュール(例えばカスタム Intellectual property(IP)など)をパートナーに納品する際、qxp ファイルで提供できるので、下位パーティションの HDL ファイルを開示する必要がない

- 性能を維持したままで下位の各パーティションを組み込むことができる

Quartus Prime の操作フローはやや複雑ですが、

複数のグループで同時に設計をしている場合や、完成した下位モジュールからコンパイル作業に入りたい(かつ各モジュールの性能も維持したい)場合などに適した手法です。

インクリメンタル・コンパイルの主な作業はこの2つ

トップダウン・アプローチもボトムアップ・アプローチも、主な作業はこの2つ!

- デザインに対してパーティションを作成すること

- 各パーティションのネットリスト・タイプを指定すること

これらをどのような手順でどのように作業するかは、各アプローチ方法により異なります。

ここでは、各アプローチ共通の操作に関してざっくりとご紹介します。

パーティションを作成する

ユーザー自ら、最上位階層のプロジェクトに対して “パーティション” という境界(間仕切り)を作ります。

インクリメンタル・コンパイルでは、このパーティション単位でコンパイル結果の情報(データベース)を生成します。

そのため、次回のコンパイル時に、前回のデータベースを更新(再コンパイル)するか、流用(保持)するかをパーティションごとに指定できるので、変更のあったパーティションだけを再コンパイルさせることができるのです。

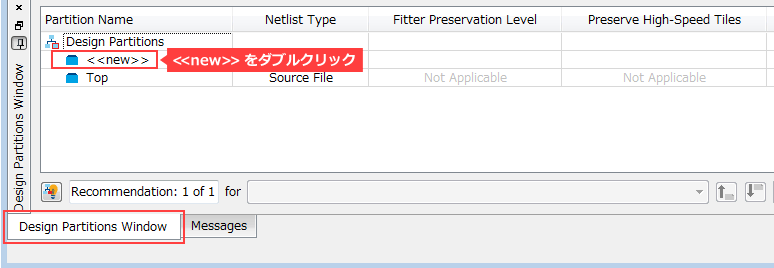

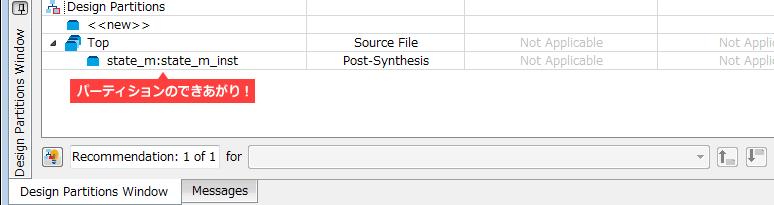

1. パーティションをコントロールするための Design Partitions Window (Assignments メニュー)を表示させて、<< new >> をダブルクリックします。

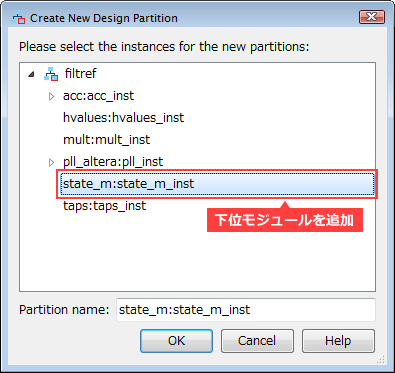

2. Create New Design Partition のウィンドウが立ち上がるので、下位モジュールを追加します。

3. これでパーティションの登録完了です!(プロジェクトの最上位デザインは、常に “TOP” としてパーティションに登録されます。)

プロジェクト内すべてのモジュールをパーティションに登録するかどうかは、ユーザーがどのようにプロジェクトのデザインを管理したいか、によります。

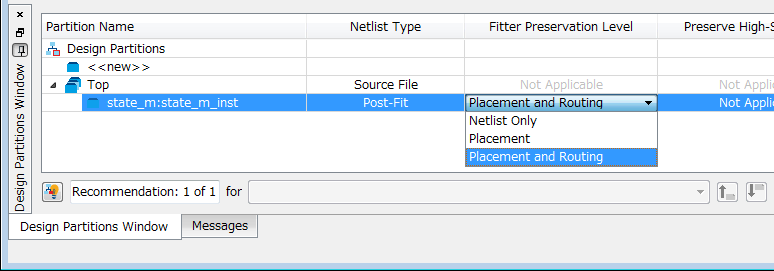

パーティションのネットリスト・タイプを指定する

作成したパーティションに対して、次回のコンパイル時に “前回のコンパイル結果のどの時点の情報” を適用するかを、Design Partitions Window の Netlist Type で指定します。

ネットリストの種類には、以下があります。

| Netlist Type | 概要 |

| Source File | ソース・ファイルを使用し、常にコンパイルが実行されます。 |

| Post-Synthesis | 前回のコンパイル(論理合成後)のネットリストを適用します。 |

| Post-Fit | 前回のコンパイル(配置配線後)のネットリストを適用します。 |

| Empty | ソースもネットリストも使用しません。パーティション間のポート接続のみ実行されます。 |

また、Post-Fit を指定した場合はさらに細かく配置配線状況のレベル(Fitter Preservation Level)を指定することが可能です。

インクリメンタル・コンパイルの操作方法

各アプローチ方法に応じた操作手順は、下記インテル® FPGA オンライン・トレーニングをご覧ください。

コース名は Quartus II ですが、現在の Quartus Prime も同様の操作フローです。

Quartus II インクリメンタル・コンパイル入門

Quartus II インクリメンタル・コンパイルによるチームベースのデザイン・フロー

なお、インテル® FPGA オンライン・トレーニングの受講方法は、下記ページを参考にしてください。

インテル FPGA テクニカル・トレーニングを無料で受講しよう

メーカーのホームページにインクリメンタル・コンパイルに関する技術資料やトレーニングおよびデモをまとめたポータルページがありますので、こちらもご利用ください。(※ 最新情報は英語サイトをご活用ください。)

インクリメンタル・コンパイル・リソース・センター(日本語サイト)

インクリメンタル・コンパイル・リソース・センター(英語サイト)

オリジナル資料も現在作成中です!(近日公開予定)

最後に

いかがでしたか、インクリメンタル・コンパイル。

簡易的にコンパイル時間を短縮したいなら スマート・コンパイル や ラピッド・リコンパイル、計画的に詳細なコントロールをしたい & そのついでにコンパイル時間も短縮したいなら インクリメンタル・コンパイル ですね。

知っているのと知らないのでは、コンパイル時間に大きな差があります。うまく活用して、効率アップを図ってください。

おすすめ記事/資料はこちら

FPGA デザインの一部だけを再コンパイルする方法

配置制約した下位エンティティを別プロジェクトへ適用させる方法(概要)

Quartus®Prime にはコンパイル時間を短縮させる こんな方法があった

Quartus® はじめてガイド - コンパイル・レポート・ファイルの見方

FPGA / CPLD の一般的な開発フロー