こんにちは。

マクニカでインテル® FPGA 製品の技術サポートをしている インテル・F・ハナコ です。

ここでは、Quartus® Prime Pro Edition において配置制約した下位エンティティを、別のプロジェクトで適用させる方法をご紹介します。

Notes:

・ 配置制約した下位エンティティを、別プロジェクトへ適用させる概要説明は、こちらの記事をご覧ください。

・ Quartus Prime Standard Edition では仕様や作業フローが異なります。こちらの記事 をご覧ください。

作業環境

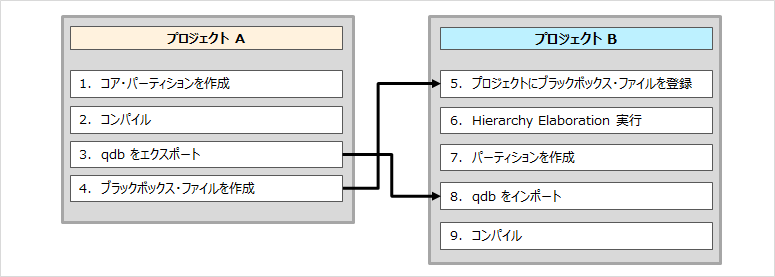

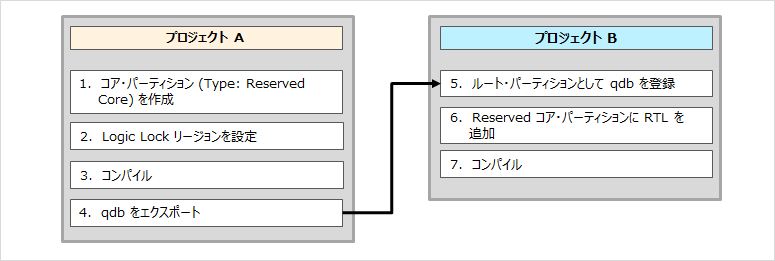

今回はわかりやすく説明するため、2つのプロジェクトを用意し、それぞれを [プロジェクト A]、[プロジェクト B] とします。

[プロジェクト A] で使用していた下位エンティティを、[プロジェクト B] にインプリメントさせるフローです。

その際、デバイス型番 および Quartus Prime Pro Edition の環境は、以下の必要があります。

|

プロジェクト A |

プロジェクト B |

|

| FPGA |

同じ型番 |

|

|

Quartus Prime Pro Edition |

同じバージョン (ビルド番号を含む) |

|

Pro Edition のパーティション仕様

Pro Edition のパーティション仕様は、以下の2パターンがあります。

|

タイプ |

概要 |

| コア・パーティション | コア・リソース(LUT、レジスタ、M20K メモリーブロック、および DSP)のみを含めることができます。 |

| ルート・パーティション | ルート・パーティションには、周辺リソース(I/O、HSSIO、PCIe、PLL を含む)、および関連するコア・リソースが含まれますが、コア・パーティションは今後の開発のために Open のままにします。 |

いずれも、パーティションに対してネットリスト・ファイル qdb をエクスポートし、別のプロジェクトで再利用します。

では、各フローを Quartus Prime Pro Edition のメニューで具体的にご案内します。

コア・パーティションの作業フロー

下図は、コア・パーティションを再利用する作業をフローチャート化したものです。

1.[プロジェクト A]コア・パーティションを作成する

① デザインを論理合成するため、Compilation Dashboard の Analysis & Synthesis を実行します。

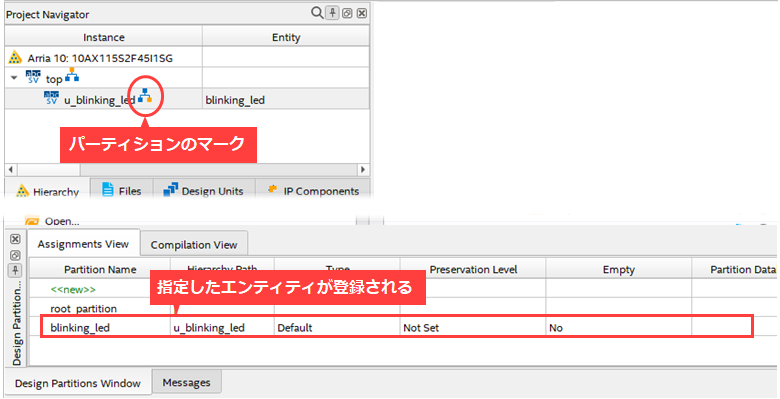

② パーティションを作成するための Design Partitions Window(Assignments メニュー)を表示します。

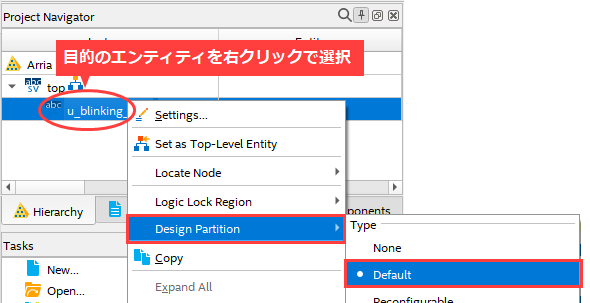

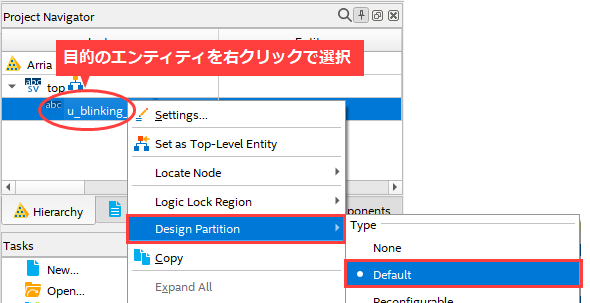

③ Project Navigator ウィンドウからパーティションを作成したいエンティティを右クリックし、Design Partition > Default (Type 内) を選択します。

指定したエンティティが登録されたことを確認します。

2.[プロジェクト A]コンパイル実行

Compilation Dashboardにおいて、コンパイルを実行します。

3.[プロジェクト A]qdb をエクスポート

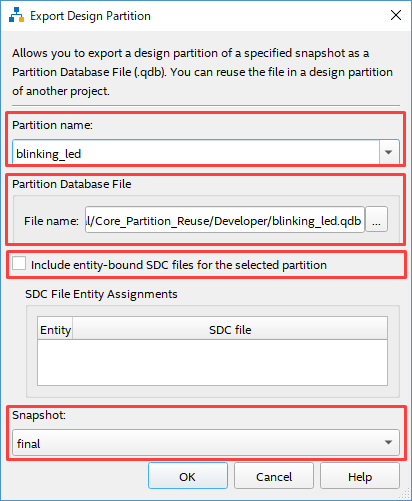

① Project メニュー > Export Design Partition を選択します。

② Export Design Partition ダイアログボックスにおいて、各項目を指定します。

|

項目 |

概要 |

| Partition name | プルダウンリストから、エクスポートしたいエンティティを指定します。 |

| Partition Database File | File name に、生成する .qdb ファイルと生成先のフォルダを指定します。(ファイル名は変更しないでください。) |

| Include entity-bound SDC files for the selected partition |

エクスポートする .qdb に対して、エンティティにバインドした SDC 情報を含ませるかを設定できます。 Stratix® 10 ターゲットの IP は、デフォルトでエンティティにバインドした SDC ファイルを使用します。 Arria® 10 ターゲットの IP は、エンティティにバインドした SDC ファイルをデフォルトで使用しません。Arria 10 でこのオプションを適用するには、最初に .qsf のエンティティに .sdc をバインドします。 詳細は、メーカーのドキュメントをご覧ください。 Intel® Quartus® Prime Pro Edition User Guide: Timing Analyzer : Using Entity-bound SDC Files |

| Snapshot | synthesized または final を選択します。 |

③ OK ボタンをクリックし、指定先のフォルダーに、目的のエンティティ用 qdb ファイルを生成します。

ハナコ's ポイント!

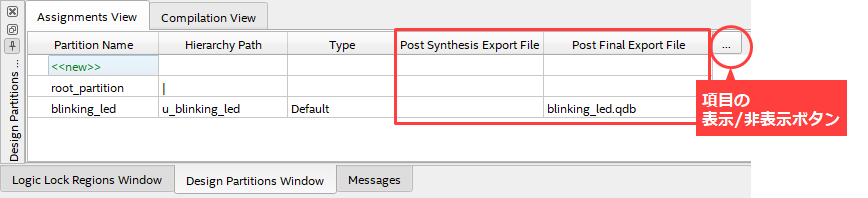

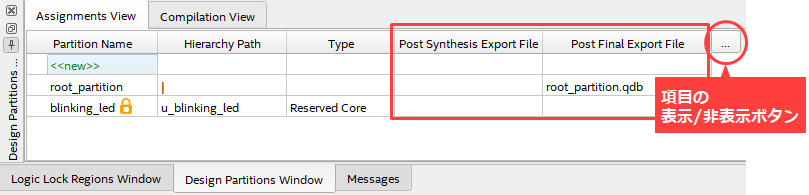

Design Partitions Window の Post Synthesis Export File あるいは Post Final Export File に .qdb を設定しておくと、

コンパイル実行の度に指定のパーティション生成が自動化できます。

4.[プロジェクト A]ブラックボックス・ファイルを登録

エクスポートするエンティティのブラックボックス・ファイルを作成します。

ファイル保存時に、プロジェクト A に登録しないように注意してください。

例)

module blinking_led (

output [3:0] value,

input clock

);

endmodule

5.[プロジェクト B]プロジェクトにブラックボックス・ファイルを登録

既存のプロジェクト B をオープンし、操作4で作成したブラックボックス・ファイルを Add/Remove Files in Project (Project メニュー) により、プロジェクトへ登録します。

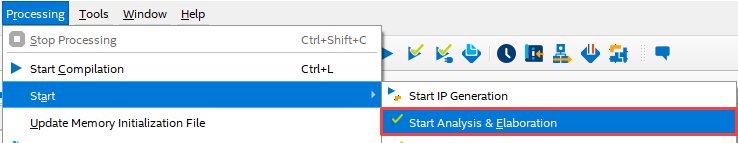

6.[プロジェクト B]Hierarchy Elaboration を実行

プロジェクト B のエンティティ構成を Quartus Prime に認識されるため、Hierarchy Elaboration を実行します。

7.[プロジェクト B]パーティションを作成する

Project Navigator ウィンドウから、ブラックボックスのエンティティを右クリックし、Design Partition > Default (Type 内) を選択します。

8.[プロジェクト B]qdb をインポート

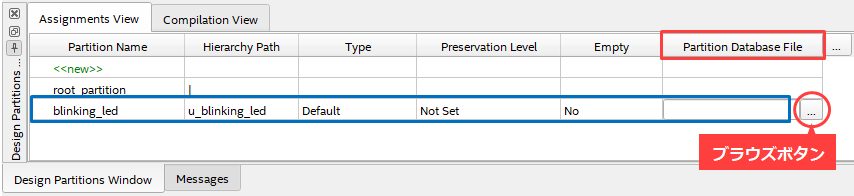

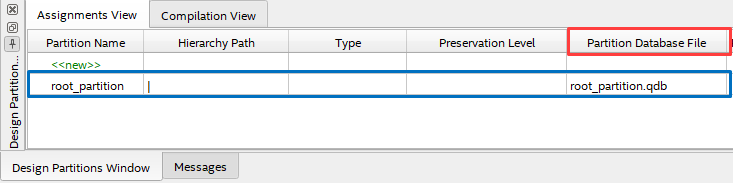

① Design Partitions Window(Assignments メニュー)を表示します。

② 該当するパーティションの Partition Database File 欄をダブルクリックし、ブラウズボタンにより プロジェクト A で生成した

.qdb ファイルを指定します。

9.[プロジェクト B]コンパイル実行

Compilation Dashboardにおいて、コンパイルを実行します。

実行後、コンパイル・レポートでコンパイルの結果を確認し、目的のパーティションが、プロジェクト A での配置およびルーティングを継承したまま、プロジェクト B へ適用できたことを確認します。

以上で、コア・パーティションの作業フローは終了です。

ルート・パーティションの作業フロー

下図は、ルート・パーティションを再利用する作業をフローチャート化したものです。

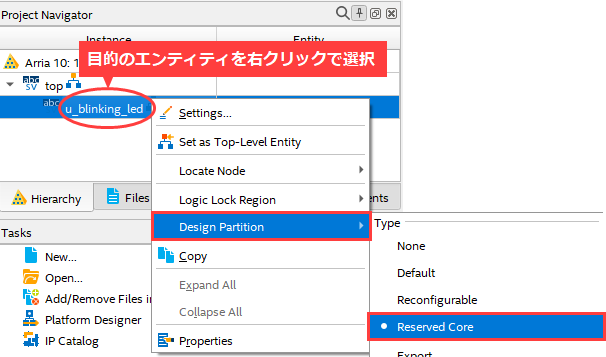

1.[プロジェクト A]コア・パーティション(Type: Reserved Core)を作成する

① Analysis & Elaboration を実行します。

② パーティションを作成するための Design Partitions Window(Assignments メニュー)を表示します。

③ Project Navigator ウィンドウからパーティションを作成したいエンティティを右クリックし、

Design Partition > Reserved Core (Type 内) を選択します。

④ Design Partitions Window 内のトップ・エンティティに対して、Post Synthesis Export File あるいは Post Final Export File を生成させる

.qdb ファイルを指定します。

もし、各パーティションに SDC ファイルをバインドさせる場合には、ここで .qdb ファイルを指定せず、

コンパイル後に Export Design Partition (Project メニュー) において生成させてください。

2.[プロジェクト A]Logic Lock リージョンを設定

① Assignments メニュー > Logic Lock Regions Windowを表示します。

② Project Navigator ウィンドウにおいて、コア・パーティションに Logic Lock 制約をするため、

右クリック > Logic Lock Region > Create New Logic Lock Region を選択します。

③ リージョンに各種設定をします。

・Origin :ユーザーの仕様に応じて任意

・Width/Height :ユーザーの仕様に応じて任意

・Reserved :On

・Core-Only :On

・Size/State :Fixed/Locked

・Routing Region :ユーザーの仕様に応じて、Unconstrained 以外の設定を選択

各カラムの詳細は、こちらの記事 の "表2. Logic Lock リージョンの属性" を参考にしてください。

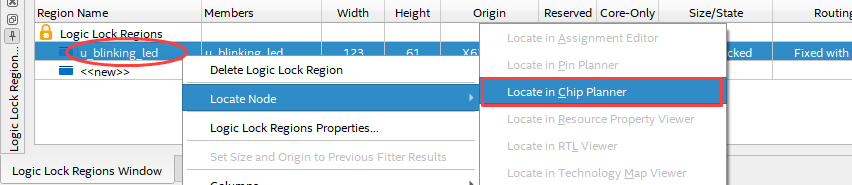

Logic Lock Regions Window のパーティションを右クリック > Locate Node > Locate in Chip Planner をクリックすると、

Chip Planner が起動します。

Logic Lock 領域は、網がけされています。

ペリフェラルを保存するには、Lock Lock リージョン外のすべてをエクスポートする必要があります。

3.[プロジェクト A]コンパイル実行

Compilation Dashboardにおいて、コンパイルを実行します。

4.[プロジェクト A]qdb をエクスポート

.qdb ファイルがプロジェクト・フォルダーへ生成されていることを確認します。

操作1.④ で .qdb ファイルを指定していない場合は、Project メニュー > Export Design Partition >Export Design Partition ダイアログボックスにおいて各項目を指定し、

.qdb ファイルを生成します。(コア・パーティションの作業フロー "操作3." を参考にしてください。)

5.[プロジェクト B]ルート・パーティションとして qdb を登録

① 既存のプロジェクト B をオープンします。

② Design Partitions Window(Assignments メニュー)を表示し、root_partition の Partition Database File 欄をダブルクリックします。

ブラウズボタンにより プロジェクト A で生成した .qdb ファイルを指定します。

6.[プロジェクト B]Reserved コア・パーティションに RTL を追加

Add/Remove Files in Project (Project メニュー) により、コア・パーティションの RTL および、必要なすべての SDC ファイルをプロジェクトに登録します。

7.[プロジェクト B]コンパイル実行

Compilation Dashboardにおいて、コンパイルを実行します。

実行後、コンパイル・レポートでコンパイルの結果を確認し、目的のパーティションが、プロジェクト A での配置およびルーティングを継承したまま、

プロジェクト B へ適用できたことを確認します。

以上で、ルート・パーティションの作業フローは終了です。

おすすめ記事/資料はこちら

配置制約した下位エンティティを別プロジェクトへ適用させる方法 (概要)

配置制約した下位エンティティを別プロジェクトへ適用させる方法 (Standard Edition)

Quartus® Prime にはコンパイル時間を短縮させる こんな方法があった