Altera® FPGA で PCI Express では、FPGA で PCI Express を実現する方法のイメージを説明しています。その中の 1つとして Avalon Memory Mapped (Avalon-MM) 構成がありますが、ここでは Arria® 10 での PCI Express Avalon-MM 構成サンプル・デザインを使用した動作確認方法について説明します。

このリファレンス・デザインを使用することで、ターゲットとなる PC、ボードの環境が動作することを簡単に確認できます。デバイス型番やピン配置などを変更することで、皆さんが作成したボードでの動作確認にも使用できます。

環境

- ツール:Quartus® Prime 開発ソフトウェア v17.1

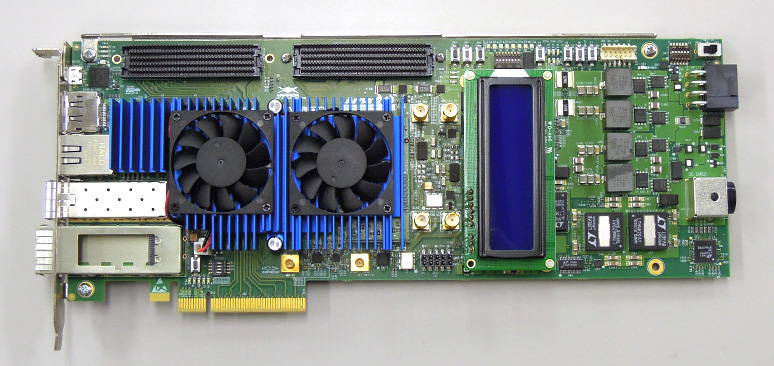

- 開発キット:Arria® 10 GX FPGA 開発キット <Macnica-Mouser 購入サイト>

- PC:PCI Express インタフェースを持ったデスクトップ PC

- OS:Windows® 7, Windows® 10

※ Qsys システム統合ツール は Quartus Prime v17.1 から Platform Designer へ名称変更されました。

手順

- リファレンス・デザインの紹介

- リファレンス・デザイン1:Gen2、8レーン構成、外部メモリ接続なし

- リファレンス・デザイン2:Gen3、4レーン構成、外部メモリ接続なし

- リファレンス・デザイン3:Gen2、8レーン構成、外部メモリ接続あり

- 動作確認

- ソフトウェアのインストール

- ハードウェアの設定

- 動作確認

- デザインの変更方法

- デザイン上の留意点

- address_span_extender について

- 選択する Hard IP mode について

1. リファレンス・デザインの紹介

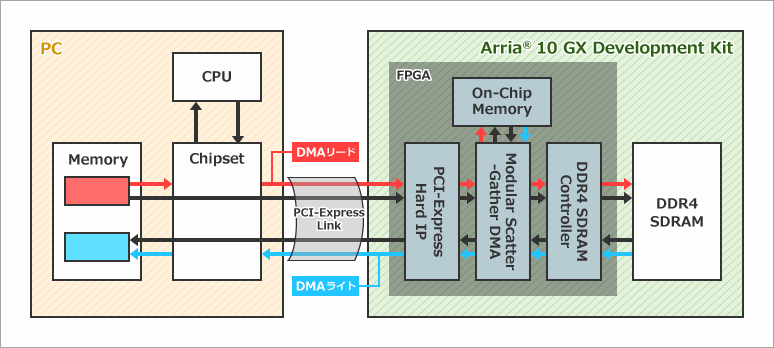

本デザインは、FPGA 内に実装された DMA エンジンを使用して DMA 転送を行います。DMA リードの場合は、PC ソフトウェアからの操作により PCI Express リンク経由でコマンドが発行されると DMA エンジンの設定レジスタに必要な情報が設定され、DMA エンジンがマスタとして動作します。DMA エンジンは、メモリ・リード・コマンドで PC 側のメモリからデータを読み出し、FPGA 内部のオンチップ・メモリ、または、FPGA に接続されている外部の DDR4 SDRAM メモリにデータを書き込みます。DMA ライトの場合は逆に、DMA エンジンは、FPGA 内部のオンチップ・メモリ、または、FPGA に接続されている外部 DDR4 SDRAM メモリからデータを読み出し、メモリ・ライト・コマンドで PC 側のメモリにデータを書き込みます。

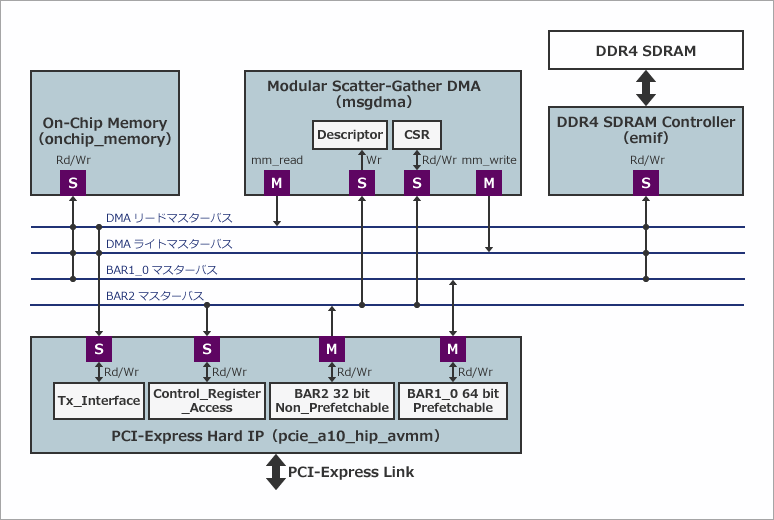

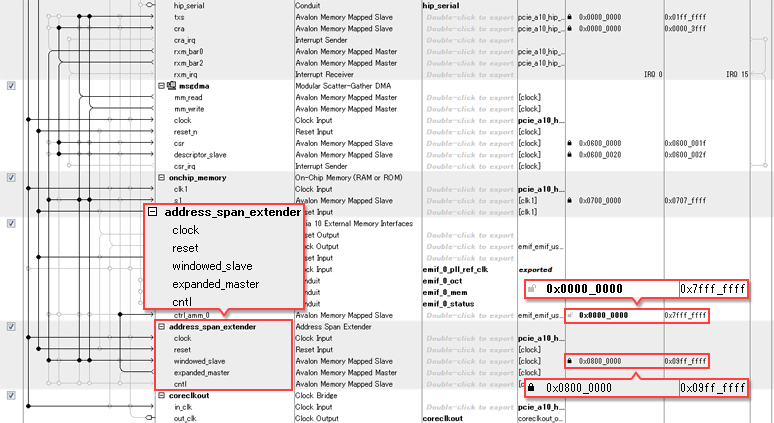

本デザインでは、Platform Designer のコンポーネントとして、PCI Express Hard IP、オンチップ・メモリ、DMA エンジン、外部メモリ(DDR4 SDRAM)コントローラを実装しています。PCI Express Hard IP は、PCI Express Link との接続を行っています。ベース・アドレスは、BAR1_0 で 64ビット・プリフェッチャブル・アドレス空間を BAR2 で 32ビット・ノンプリフェッチャブル・アドレス空間を実装しています。Contorol_Register_Access では PCI Express(PC 側)のアドレス空間と Avalon-MM(Platform Designer 側) のアドレス空間の変換を行う設定など、ブリッジ機能としての各種設定を行うためのレジスタ・アクセス用スレーブ・ポートとなっています。Tx_Interfaceは、DMA リード/ライト・マスタ(mm_read/mm_write)からの要求を受け付けるためのスレーブ・ポートの役割を担います。

オンチップ・メモリは、転送レート計測用ソフトウェアの転送モードを “Run OnChipMemory DMA Test“ とした場合に転送のターゲットとなります。外部メモリ・コントローラは、転送レート計測用ソフトウェアの転送モードを “Run DDR DMA Test“ とした場合に転送のターゲットとなります。これらのモードでは、各ターゲットメモリは、PCI Express の BAR1_0 マスタと DMA リード/ライト・マスタからアクセスされます。

DMA エンジンは、mSGDMA (Modular Scatter-Gather DMA) を使用しています。Platfrom Designer には、これ以外にDMA (Simple DMA) と SGDMA (Scatter-Gather DMA) の2種類のDMAエンジンがありますが、広帯域を要求する DMA 転送を行う場合には、mSGDMA が適しています。

リファレンス・デザイン1:Gen2、8レーン構成、外部メモリ接続なし

Gen2、8 レーン構成、外部メモリ接続なしのサンプル・デザインです。Arria® 10 FPGA 開発キット上ですぐに動作確認できます。外部メモリ接続がないので、容易に他のボードへの移植が可能です。

Gen2、8 レーンの場合、理論値としての総帯域は、4000MB/s となります。理論値に対する実効帯域は、多少余裕を見て、これの 50 ~ 60% と見積もってください(2000 ~ 2400MB/s 程度)。

a10_devkit_pcie_g2x8_msgdma_grd_17_1__1.qar

リファレンス・デザイン1

リファレンス・デザイン2:Gen3、4レーン構成、外部メモリ接続なし

Gen3、4 レーン構成、外部メモリ接続なしのサンプル・デザインです。Arria® 10 FPGA 開発キット上ですぐに動作確認できます。

Gen3、4 レーンの場合も、理論値としての総帯域は、4000MB/s となります。理論値に対する実効帯域は、多少余裕を見て、これの 50 ~ 60% と見積もってください(2000 ~ 2400MB/s 程度)。

a10_devkit_pcie_g3x4_msgdma_grd_17_1__1.qar

リファレンス・デザイン2

リファレンス・デザイン3:Gen2、8レーン構成、外部メモリ接続あり

Gen2、8 レーン構成、外部メモリ(DDR4 SDRAM)接続ありのサンプル・デザインです。Arria® 10 FPGA 開発キット上ですぐに動作確認できます。外部メモリへの接続機能があるので、後述の GUI ソフトウェアの外部メモリへの DMA 転送機能が確認できます。外部メモリを実装する場合のリファレンス・デザインとしてご使用ください。

a10_devkit_pcie_g2x8_msgdma_ddr4_grd_17_1__2.qar

リファレンス・デザイン3

動作確認

ここでは、上で紹介したリファレンス・デザイン3 を使用して、実際の動作確認の方法について紹介します。

ソフトウェアのインストール

まず、以下より、Windows® 用の GUI ソフトウェアをダウンロードします。

https://fpgawiki.intel.com/uploads/e/e7/GUI_for_AN431.zip

GUI_for_AN431.zip を適当なフォルダに展開して、Readme.txt の内容に沿ってドライバをインストールします。

ハードウェアの設定

まず、外部メモリ用の HILO コネクタに DDR4 SDRAM 用のドータカードを装着します。次に、ボードを PC に装着し、JTAG ケーブルを接続し、PC の電源を入れます。

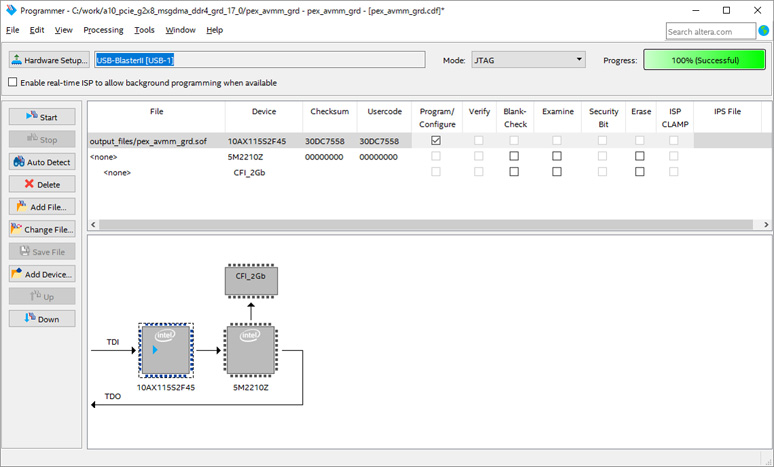

PC が起動したら、リファレンス・デザイン3 を適当なフォルダに展開し、Quartus® Prime ソフトウェアで開きます。Programmer を起動し、SOF ファイルを書き込みます。書き込みが完了したら、PC を再起動します。PC の再起動により、PC 側のルート・コンプレックスと FPGA 内のエンドポイント間で通信のための初期化処理が行われます。

動作確認

PC が再起動したら、GUI_for_AN431.zip を展開したフォルダ内にある altpcie_demo_Qsys_64.exe をダブルクリックで実行します。32ビット OS を使用している場合には、altpcie_demo_Qsys_32.exe を実行します。

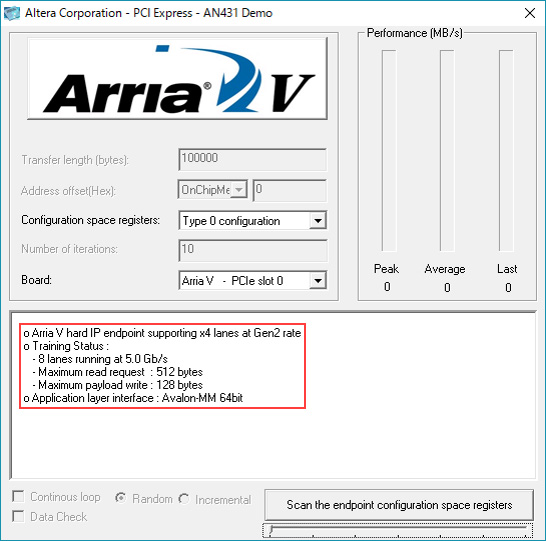

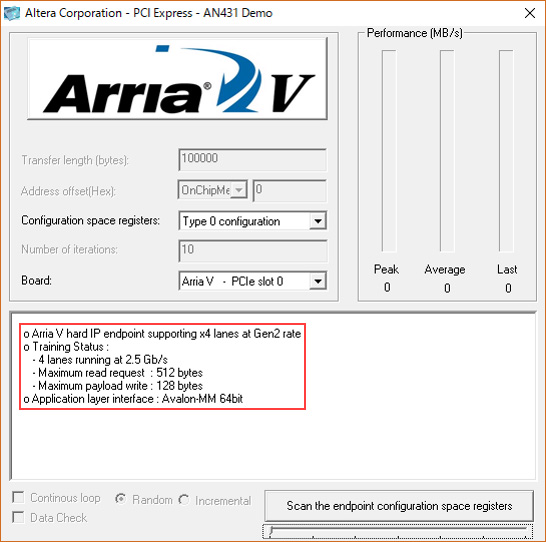

正しくリンクできると、赤枠で示したように、"8 lanes running at 5.0Gb/s" と表示されます。デバイス・シリーズの表示が、"Arria V" となっていますが、ソフトウェアの更新がされていないためで動作上の問題はありませんので、気にせず進めます。

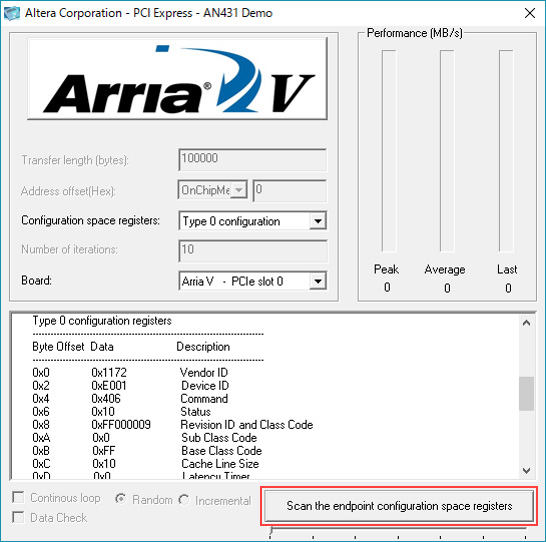

"Scan the endpoint configuration space registers" をクリックすると接続されているエンドポイントのコンフィギュレーション・レジスタの情報が表示されます。0x1172 は、旧アルテラ社のデバイスIDです。

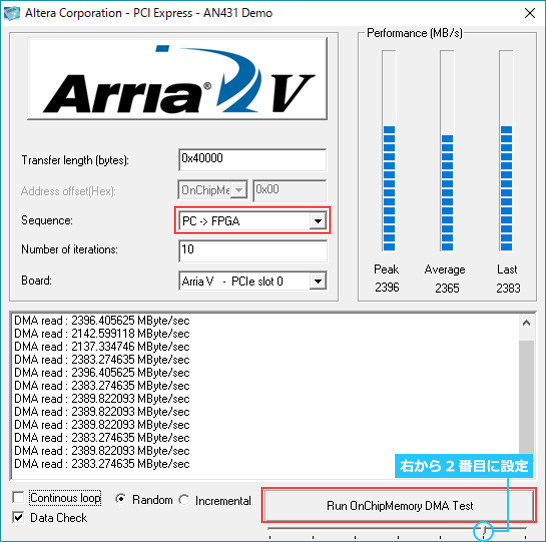

右下のスライド・バーを右から2番目(青丸)に設定すると、オンチップ・メモリをターゲットとした DMA 転送モードになります。Sequence が PC ⇒ FPGA となっているので、DMA リードとなります。"Run OnChipMemory DMA Test" をクリックすると、DMA転送が開始されます。デフォルトでは、0x40000バイトのデータ転送を実行し、Peak(最高値)、Average(平均値)、Last(最後のデータ)を表示します。

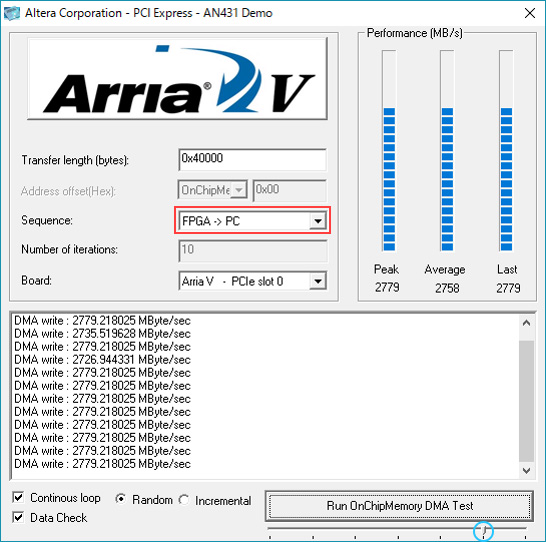

Sequence を FPGA ⇒ PC に変更すると、DMA ライトの実行となります。

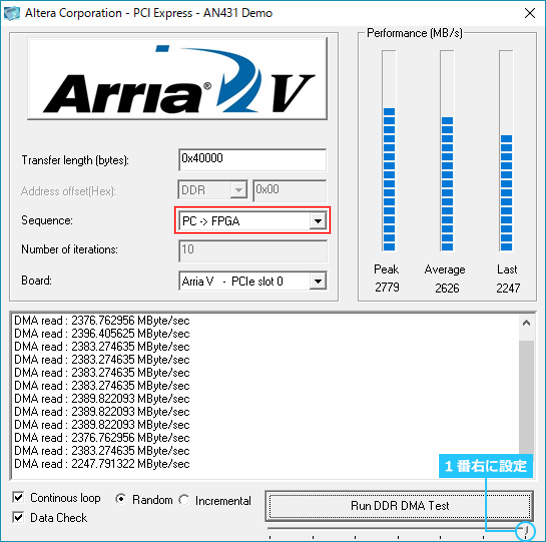

右下のスライド・バーを一番右(青丸)に設定すると、外部 DDR4 SDRAM メモリをターゲットとした DMA 転送モードになります。以下は、DMA リード実行時の結果です。

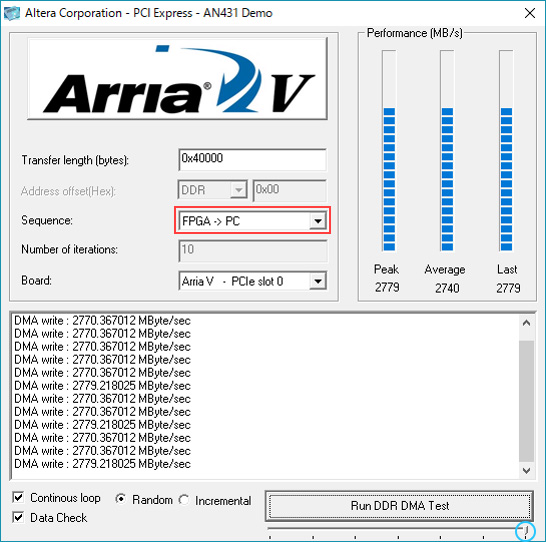

以下は、DMA ライト実行時の結果です。

デザインの変更方法

本デザインの転送レートとレーン数は、容易に変更が可能です。以下に、リファレンス・デザイン3 を Gen1 の 4レーンに変更する方法について説明します。

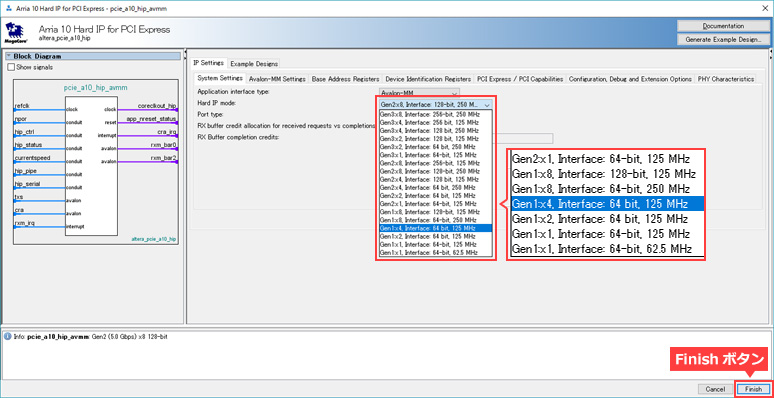

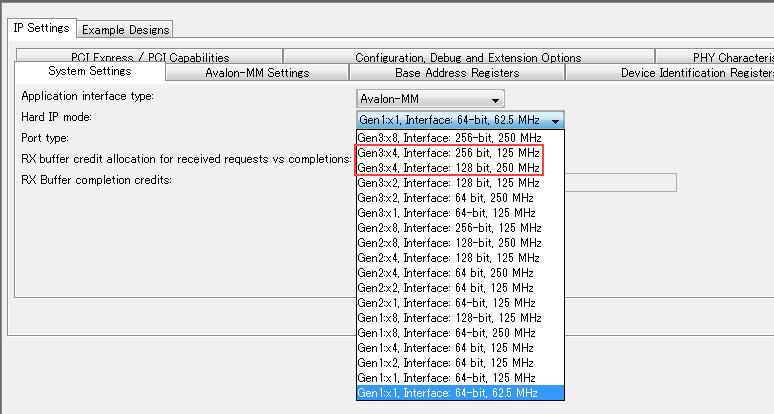

まず、Platform Designer から pex_avmm_grd.qsys を開き、pcie_a10_hip_avmm を開きます。図のように、"Gen1x4, Interface: 64 bit, 125MHz"を選択し、Finish ボタンをクリックします。

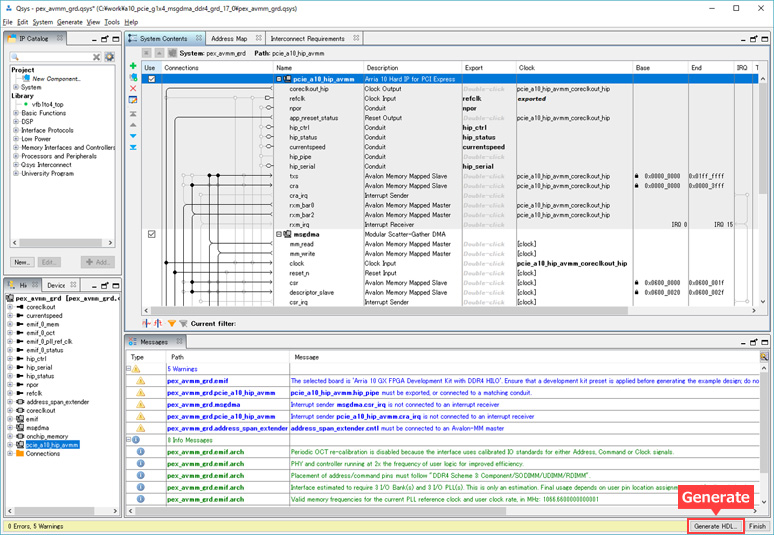

Platform Designer を Generate します。

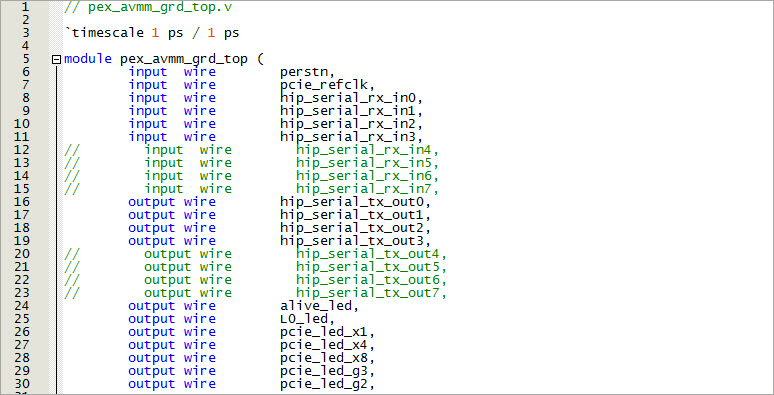

次に、トップ・ファイル(pex_avmm_grd_top.v)を編集します。8レーンから4レーンに変更するので、4~7レーンの記述を全てコメント・アウトします。

コンパイルを実行し生成された SOF ファイルで動作確認を行ってください。GUI のソフトウェア上で、"4 lanes running at 2.5Gb/s" と表示されれば、正しく編集できたことになります。

デザイン上の留意点

address_span_extender について

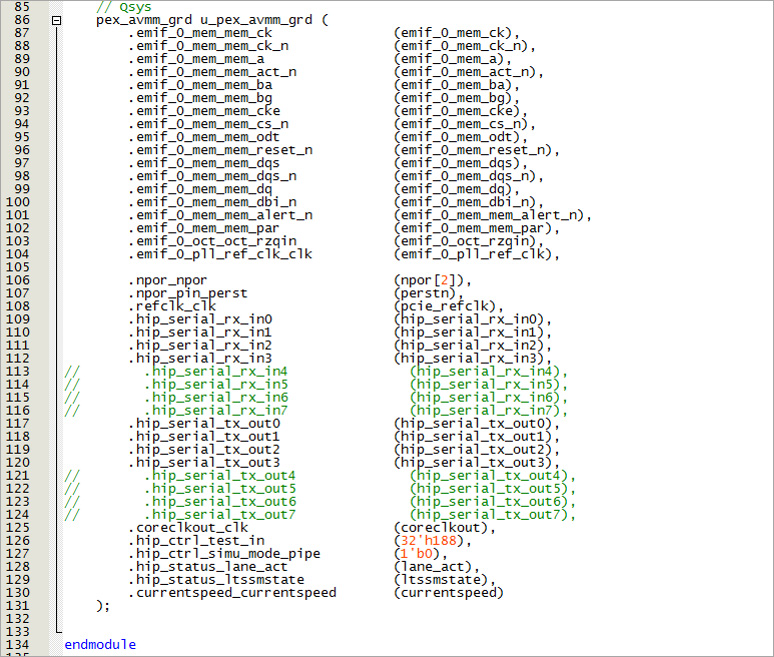

外部メモリ接続ありのリファレンス・デザイン3 では、Platform Designer から pex_avmm_grd.qsys を開くと、System Contents タブにて、"address_span_extender" が実装されていることが確認できます。ソフトウェアの GUI では、外部 DDR 系メモリの先頭アドレスを 0x08000000 と指定しているため、Platform Designer 上の DDR4 SDRAM メモリのベース・アドレスも 0x0800_0000 に合わせる必要があります。しかし、本評価用ボードに実装されている DDR4 SDRAM メモリのアドレス幅は、0x0000_0000~0x7FFF_FFFF(2GB)と大きいため、ベース・アドレスを 0x0800_0000としてしまうと Platform Designer 上で連続でアドレス値を指定することができません。

address_span_extender は、これを回避するための処置として実装されています。address_span_extender の windowed_slave のアドレスは、32MB:0x0800_0000~0x09FF_FFFF となっているので、実際には、2GB ある DDR4 SDRAM メモリの領域のうち、32MB 分のアクセスを行っています。

ユーザー様が本デザインを流用して大容量の外部メモリにアクセスする場合には、ベース・アドレスを例えば、0x0000_0000 などの値に変更してもらえれば、address_span_extender を使用する必要もなく、大容量のアドレス空間にアクセスが可能となります。

選択する Hard IP mode について

選択する転送レートとレーン数によって複数の選択肢が存在します。たとえば、Gen3x4 の場合、"Gen3x4, Interface: 256 bit, 125MHz" と "Gen3x4, Interface: 128 bit, 250MHz" の2つが選択できます。これは、生成されるAvalonバスのバス幅とスピード(Fmax)を表しますので、前者の場合には、バス幅は小さいがスピードが速い構成、後者の場合には、バス幅は大きいがスピードが遅い構成となります。

どちらを選択しても機能的には問題ありませんが、前者の場合には、タイミングのメットが厳しくなる傾向があります。後者の場合には、デバイス・リソースをより多く消費します。以上を考慮して選択するようにしてください。

ユーザー・ガイド

Arria 10 and Cyclone 10 Avalon Memory-mapped Interface for PCIe Design Example User Guide

Stratix V Avalon-MM Interface for PCIe Solutions User Guide

Arria V Avalon Memory-Mapped (Avalon-MM) Interface for PCI Express Solutions User Guide

Cyclone V Avalon Memory-Mapped (Avalon-MM) Interface for PCI Express Solutions User Guide

おすすめ記事/資料はこちら

Altera® FPGA で PCI Express

Altera® FPGA で PCI Express(Avalon-ST 編)

FPGA の PCI Express デザイン & デバッグ・ガイドライン

Altera® FPGA の開発フロー