最近の Altera® FPGA では、標準的に PCI Express (PCIe) をサポートしています。Altera® FPGA で PCI Express を実装しようと思った時に、まず何から手を付ければいいのか?悩んだ人も多くいると思います。例えば、

- どの FPGA デバイスが何をサポートしているのか?

- FPGA デバイス毎にどの程度の転送レートに対応しているのか?

- FPGA デザインの方法は?リファレンスデザインの有無は?

などなど、いろいろ気になることがあると思います。

ツールは、Quartus® Prime 開発ソフトウェアや、場合によっては Quartus® Prime にバンドルされている Platform Designer システム統合ツールを使うこともあります。

はじめて Altera® FPGA で PCI Express を実現する人向けに、選定からデザイン手法の概要までの流れを紹介します。

ステップ1:使用するデバイスの選択する

はじめに、Altera® FPGA サイトの PCI-Express IP Support Center ページをご覧ください。ここでは、PCI Express プロトコルの概要や機能、デバイス・サポート、スタート・ガイド、技術サポートの項目から、Altera® FPGA の PCI Express ソリューションの概要を確認できます。

デバイス・サポートの項目を見ると、実現したい構成がどのデバイスでできるかを確認できます。例えば、PCI Express Gen1 x4 の構成であれば、一覧にあるすべてのデバイスで実現できます。また、Gen3 x8 を実現したい場合には、実現できるデバイスが限られます。

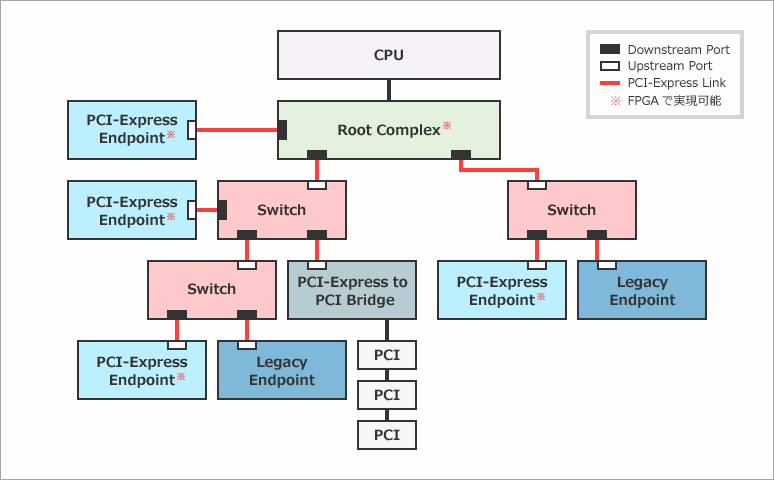

また、「デバイス・コンフィギュレーションと機能サポート」の中にエンドポイントやルート・ポートという記載がありますが、Altera® FPGA の PCI Express IP は、エンドポイントやルート・ポート(ルート・コンプレックスを実装する場合のポート)の両方が実現可能です。ルート・コンプレックスを実現する場合には、IP コアの設定をルート・ポートに設定してホスト・コントローラによる制御を追加することで実現できます。

ステップ2:データの転送形式で FPGA 内の構成を決定する

スタート・ガイドの項目の資料一覧を見ると、Avalon-Streaming (Avalon-ST) 用の資料と Avalon-Memory Mapped (Avalon-MM) 用の資料、Avalon-MM with DMA 用の資料が存在しますが、どれを選択するかは使用条件に依存します。簡単に説明すると以下の違いがあります。

なお、Avalon-ST や Avalon-MM について気になった人は、こちらをご覧ください。

【FAQ】Avalon-MM インターフェースと Avalon-ST インターフェースの違いは何ですか?

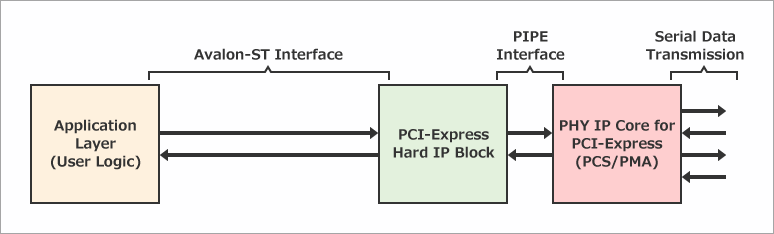

Avalon-ST 構成

PCI Express の FPGA ファブリック側のインターフェースは、Avalon-ST となります。Avalon-ST はデータをストリーム形式で転送する方式で、Start-of-Packet (SOP) と End-of-Packet (EOP) でデータの開始と終了を示します。データは PCI Express の TLP(トランザクション・レイヤ・パケット)そのものになっており、PCI Express の仕様により TLP の詳細を理解した上で実装する必要があります。その他の仕様上の制限はありません。Platform Designer 内での実装でも Platform Designer を使用しない実装でも可能です。

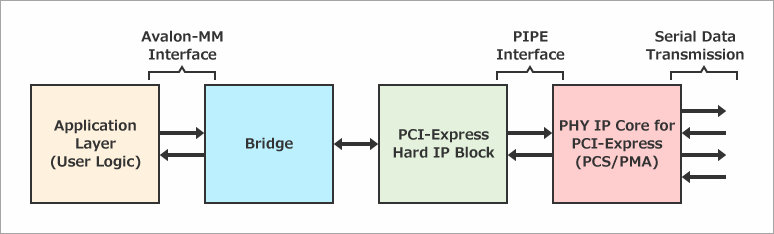

Avalon-MM 構成

PCI Express の FPGA ファブリック側のインターフェースは、Avalon-MM となります。Avalon-MM はデータをメモリ・マップド形式で転送する方式で、データの送受信時にはアドレスの指定が必要となります。実装上 Platform Designer の使用が必須となっており、Platform Designer 内部のアドレス空間とホスト PC のアドレス空間との間でアドレス変換の処理が必要となります。ただし、TLP の詳細を理解する必要なく比較的容易に実装が可能となります。仕様上の制限としては、Avalon-ST 構成に比べてタグのサポートが少ない、シングル・ファンクションのサポートのみ、ECRC forwarding 未サポート、Expansion ROM 未サポートとなります。

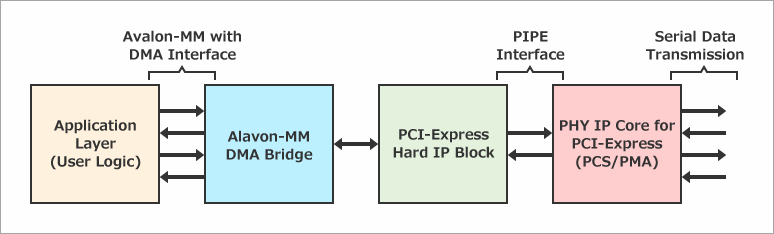

Avalon-MM with DMA 構成

基本的な構成は Avalon-MM 構成と同じですが、より高効率な転送を行うために、コアに DMA エンジンが実装されている構成となります。仕様上の制限は Avalon-MM 構成の制限と合わせて、ルート・ポートを実現できないことや TLP の対応に制限がある構成となります。詳細は各資料内に比較表があるので、そちらを参照してください。

上記を踏まえて、実現したいケースによりどの構成を選択するかを決定します。

ケース1

ルート・ポート/エンドポイントをシングル・ファンクションで実現するようなケースでは、Avalon-MM 構成での実現が一般的です。DMA を使用したい場合には、Platform Designer に標準で付属している modular Scatter-Gather Direct Memory Access (mSGDMA) を使用することで高速な DMA 転送も実現できます。タグのサポートが少ない、シングル・ファンクションのサポートのみ、ECRC forwarding 未サポート、Expansion ROM 未サポートなどの制限事項がありますが、その点に抵触しない限り、この構成での実現を推奨します。

ケース2

ルート・ポート/エンドポイントをマルチ・ファンクションで実現するようなケース、また、Platform Designer を使用したくないケースでは、Avalon-ST 構成での実装が必須となります。TLP の詳細を理解してAvalon-ST パケットの実装はユーザ・ロジックで行う必要があります。

ケース3

例えば、Gen3 x8 構成で可能な限り高効率な転送を実現したい場合には、Avalon-MM with DMA 構成を選択します。DMA エンジンが Avalon-MM ブリッジ内にあるため、より高効率な転送が実現できます。

ステップ3:リファレンス・デザインで試す

以下には、Avalon-MM 構成のリファレンス・デザインが纏まっています。

Altera FPGA Developer Site

PCI Express* IP Support Center - 2. User Guides and Reference Designs

以下は、Avalon-MM with DMAのデザインとなります。

Cyclone® V FPGA – PCIe* 2.0 x4 Avalon® Memory-Mapped DMA Design Example

Cyclone® V FPGA – PCIe* 2.0 x4 Avalon® Memory-Mapped DMA On-Chip and External Memory Design Example

Arria® V GX FPGA – PCIe* 2.0 x4 Avalon® Memory-Mapped Interface DMA Design Example

Gen3x8 Avalon-MM DMA Reference Design with Internal Memory (AN 690)

Gen3x8 Avalon-MM DMA with External DDR3 Memory (AN 708)

Gen3x8 Avalon -MM DMA with External DDR3/DDR4 Memory (AN 829)

各リファレンス・デザインは、Altera® FPGA の各デバイス・シリーズの評価用ボードで動作するように作られています。以下の開発キット用のデザインが用意されています。ソフトウェアのサンプルも用意されているので、評価用ボードがあれば実機での動作確認がすぐにできます。

参考情報

Avalon-ST 構成の実装資料

Quartus® Prime にて生成可能なリファレンス・デザインを使用することができます。Arria® 10 FPGA を例にすると、IP Catalogから Arria 10 Hard IP for PCI Express を選択し起動します。Example Designs タブから操作することで、Quartus® Primeプロジェクトが生成されます。このデザインは、Avalon-ST 構成となります。

Altera® FPGA で PCI Express(Avalon-ST 編)

Avalon-MM 構成の実装資料

Altera® FPGA で PCI Express(Avalon-MM 編)

PCI Express ハード IP を使用した DMA 転送の実現

おすすめ記事/資料はこちら

Altera® FPGA で PCI Express(Avalon-ST 編)

Altera® FPGA で PCI Express(Avalon-MM 編)

FPGA の PCI Express デザイン & デバッグ・ガイドライン

Altera® FPGA の開発フロー