Altera® FPGA で PCI Express では、FPGA で PCI Express を実現する方法のイメージを説明しています。その中の 1つとして Avalon Streaming (Avalon-ST) 構成がありますが、ここでは Arria® 10 での PCI Express Avalon-ST 構成サンプル・デザインの生成方法について説明します。

このリファレンス・デザインを使用することで、ターゲットとなる PC、ボードの環境が動作することを簡単に確認できます。デバイス型番やピン配置などを変更することで、皆さんが作成したボードでの動作確認にも使用できます。

環境

- ツール:Quartus® Prime v17.0

- 開発キット:Arria® 10 GX FPGA 開発キット <Macnica-Mouser にてご購入>

- PC:PCI Express インタフェースを持ったデスクトップ PC

- OS:Windows® 10

手順

- ハードウェアの作成

- デスクトップ PC の OS にドライバをインストール

- 動作確認

1. ハードウェアの作成

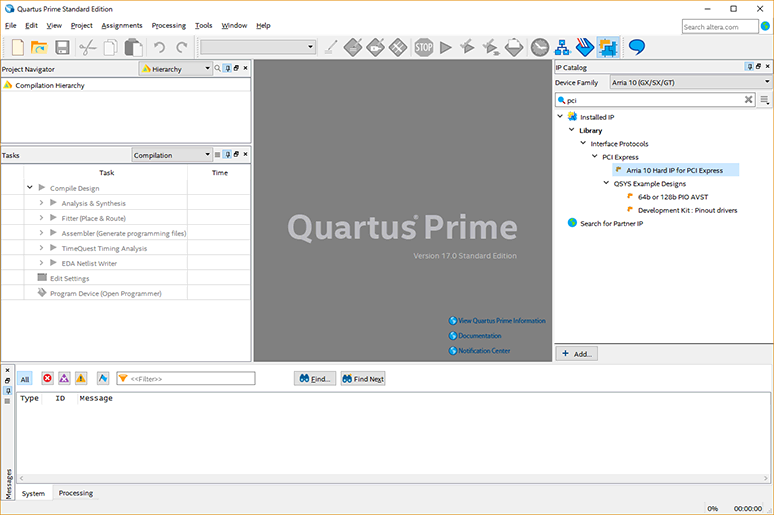

まず、Quartus® Prime を起動し、IP Catalog から Device Family を Arria® 10 に設定し、検索ボックスに PCI と入力します。

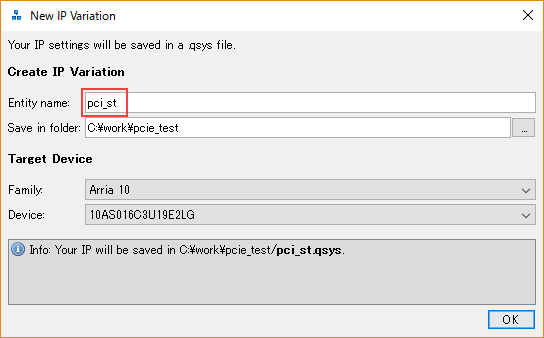

Arria® 10 Hard IP for PCI Express をダブルクリックして Qsys を起動します。New IP Variation が表示されるので、Entity Name を適当に入力します。ここでは、pci_st としました。

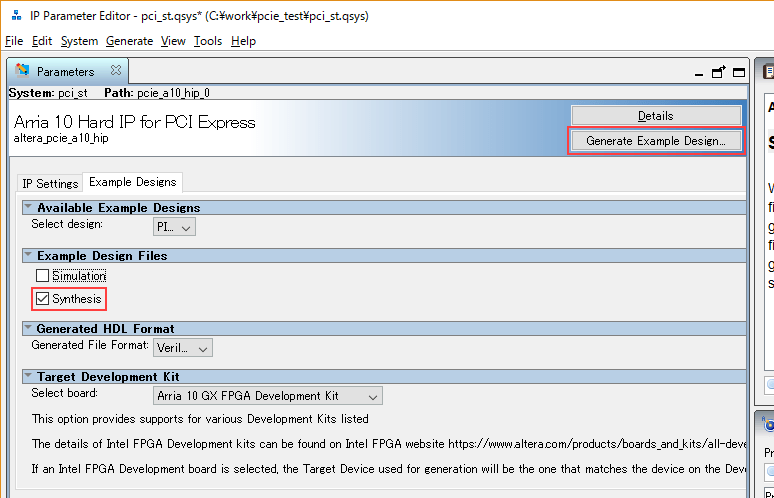

OK ボタンをクリックすると、Qsys ファイルが保存されます。Qsys 画面は、以下のようになっています。ここでは、サンプル・デザインを生成するので、Example Design タブを選択します。実機での動作確認を行うため、Synthesis にチェックを付けて、Generate Example Design ボタンをクリックします。

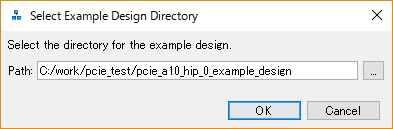

ファイルの保存場所を求められるので、保存したいフォルダを指定して OK ボタンをクリックします。

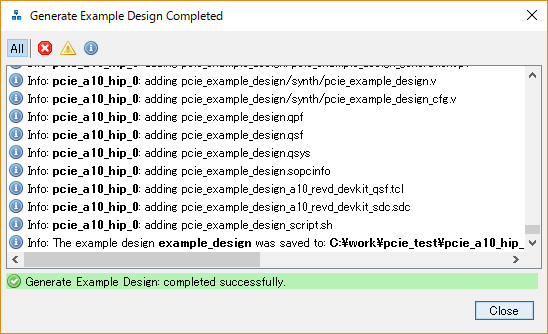

サンプル・デザインが生成されます。

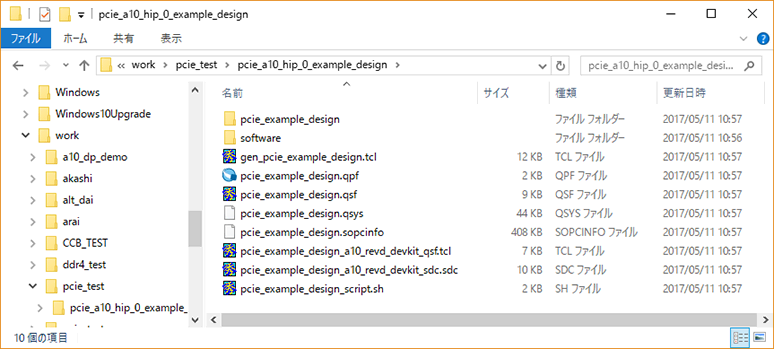

生成されたフォルダの内容は、以下のようになっています。

Quartus® Prime の File メニュー ⇒ Open Project から、pcie_example_design.qpf を選択して、生成されたプロジェクトを開きます。Arria® 10 GX Development Kit のデバイスが予め設定されています。

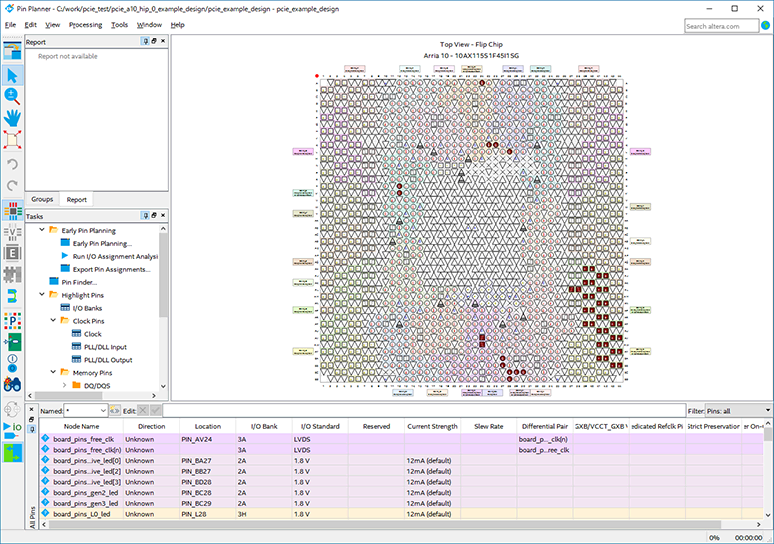

Quartus® Prime の Pin Planner を開くと、既に必要なピン・アサインがされていることが確認できます。

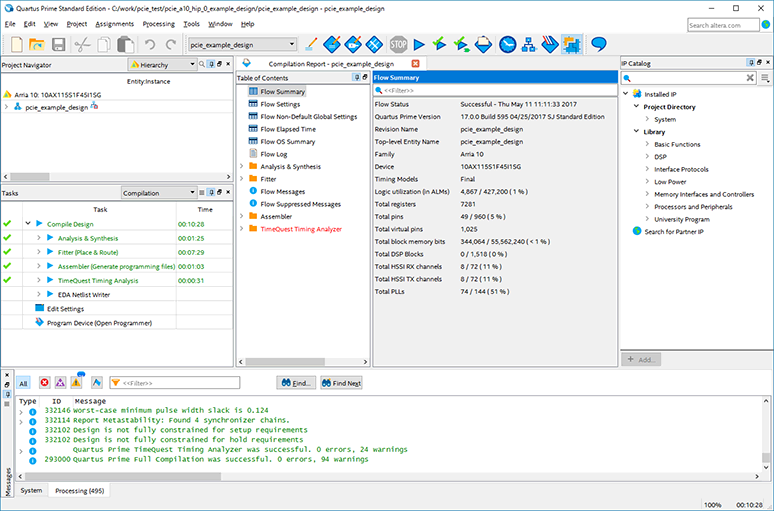

デザインをコンパイルします。コンパイルが完了すると、以下のようになります。タイミング制約ファイルも本来は手動で作成する必要があります。ここでは、タイミングは満たしていませんが、このまま進めます。

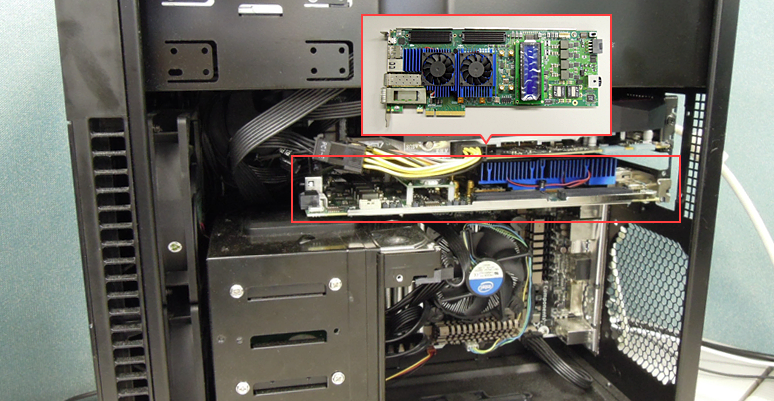

PC に評価用ボードを挿入して電源を投入します。

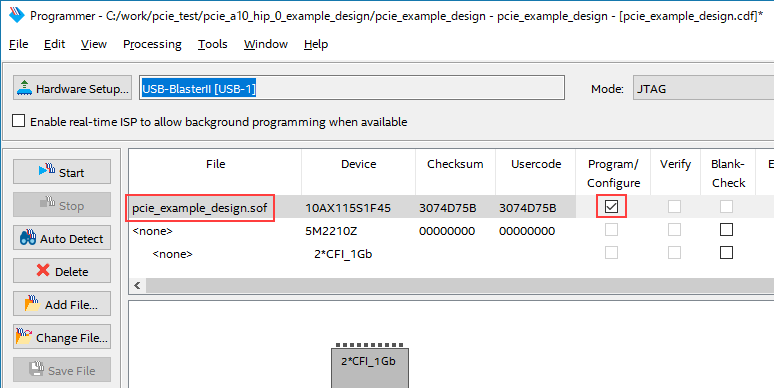

JTAG 用のケーブル(USB ケーブル)を接続して、生成した SOF ファイルを書き込みます。書き込みが完了したら、PC を再起動します。ここでは、PC を再起動することに注意してください。再起動することで、PC のシステムが書き込んだ PCI Express のデザインを正しく認識して、再度 PC を起動します。

2. デスクトップ PC の OS にドライバをインストール

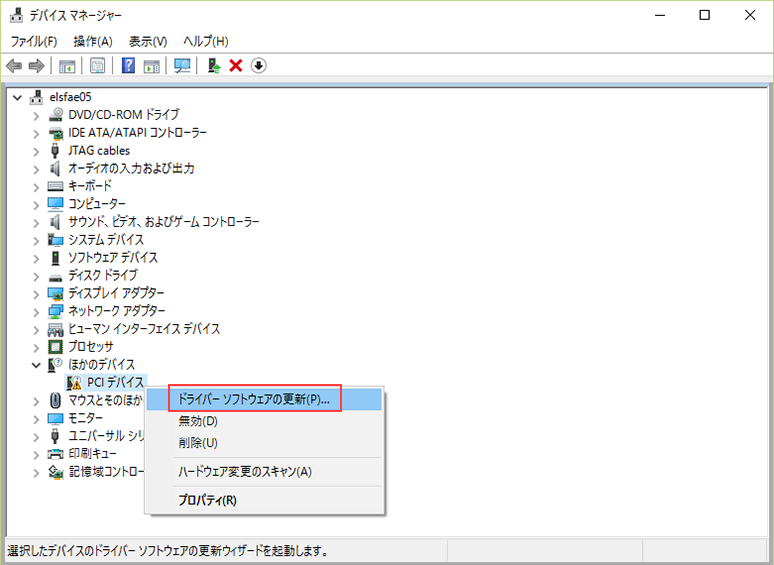

PC が起動したら、デバイス・マネージャを起動します。下図のように、不明な PCI デバイスが認識されていますので、ドライバ・ソフトウェアの更新を実行します。

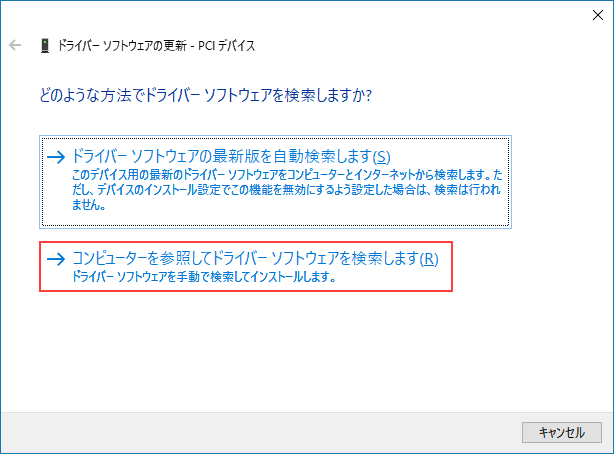

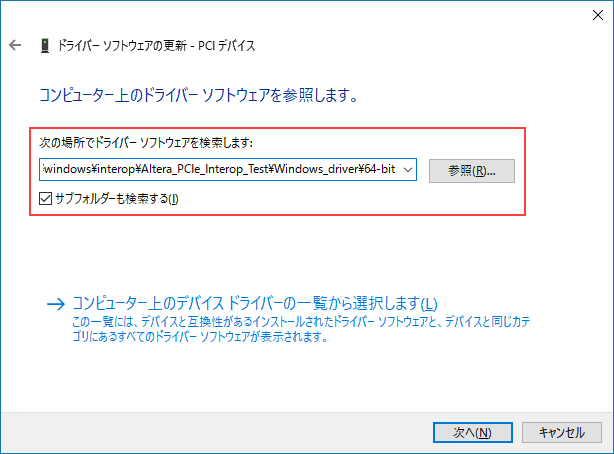

コンピュータを参照してドライバーソルトウェアを検索します(R) を実行します。

ドライバ・ソフトウェアの場所を指定します。生成したサンプル・デザインのフォルダ内の以下のパスに、Altera®_PCIe_Interrop_Test.zip があるので、予め解凍しておいてください。

pcie_a10_hip_0_example_design\software\windows\interop

解凍後の以下のフォルダをドライバ参照場所に指定してください。

pcie_a10_hip_0_example_design\software\windows\interop\Altera_PCIe_Interop_Test\Windows_driver\64-bit

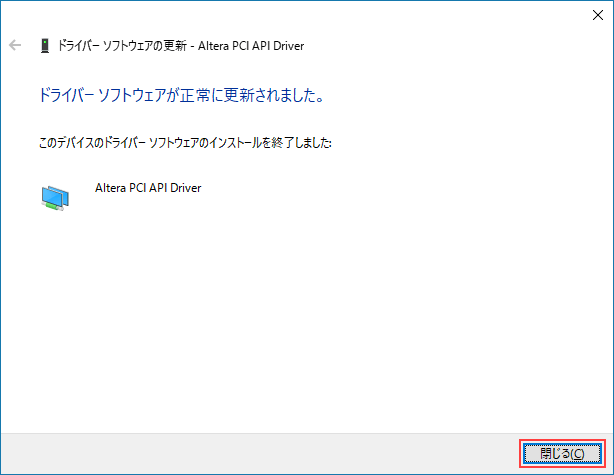

次へをクリックすると、ドライバ・ソフトウェアがインストールされます。閉じるで画面を閉じます。

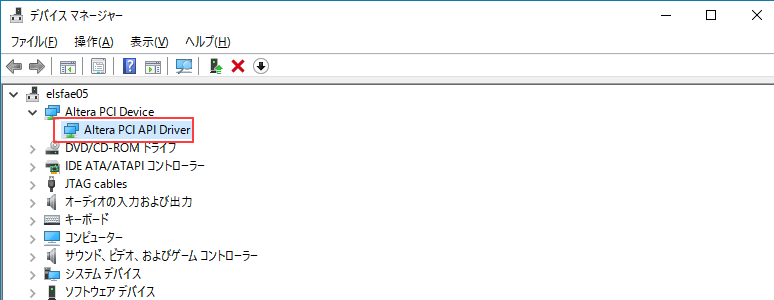

デバイス・マネージャ上で正しく認識されていることを確認します。

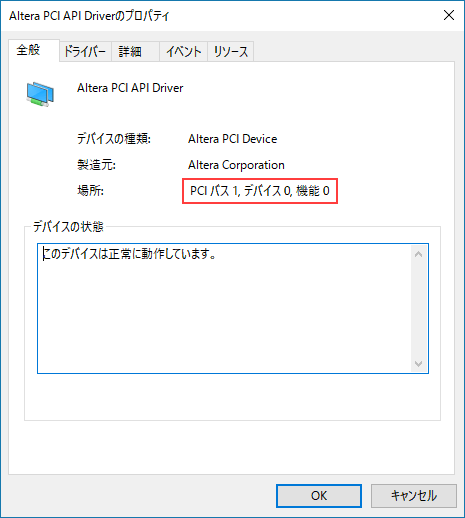

Altera® PCI API Driver のプロパティを開き、バス番号、デバイス番号、機能番号を確認します。

3. 動作確認

以下のフォルダにある、Alt_Test.exe をダブルクリックで起動します。

pcie_a10_hip_0_example_design\software\windows\interop\Altera_PCIe_Interop_Test\Interop_software

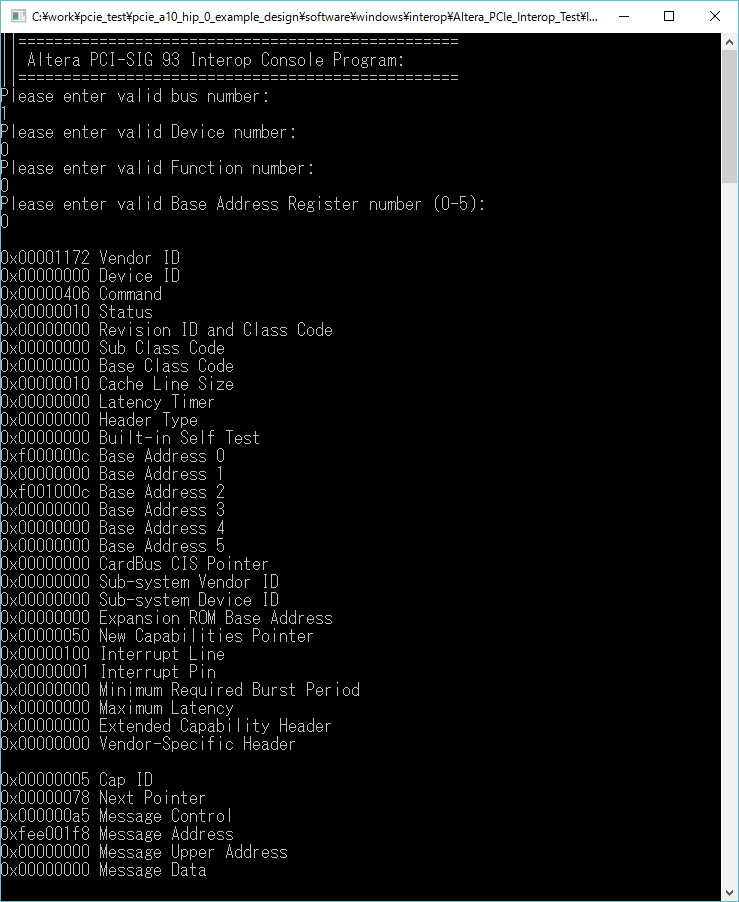

バス番号、デバイス番号、ファンクション番号の入力を求められるので、予め確認した値を入力します。次に、Base Address Register Number の指定を求められるので、ここでは、0 を指定します。

正しくアクセスできると、下図のように FPGA 内の PCI レジスタ情報を読み出して表示します。

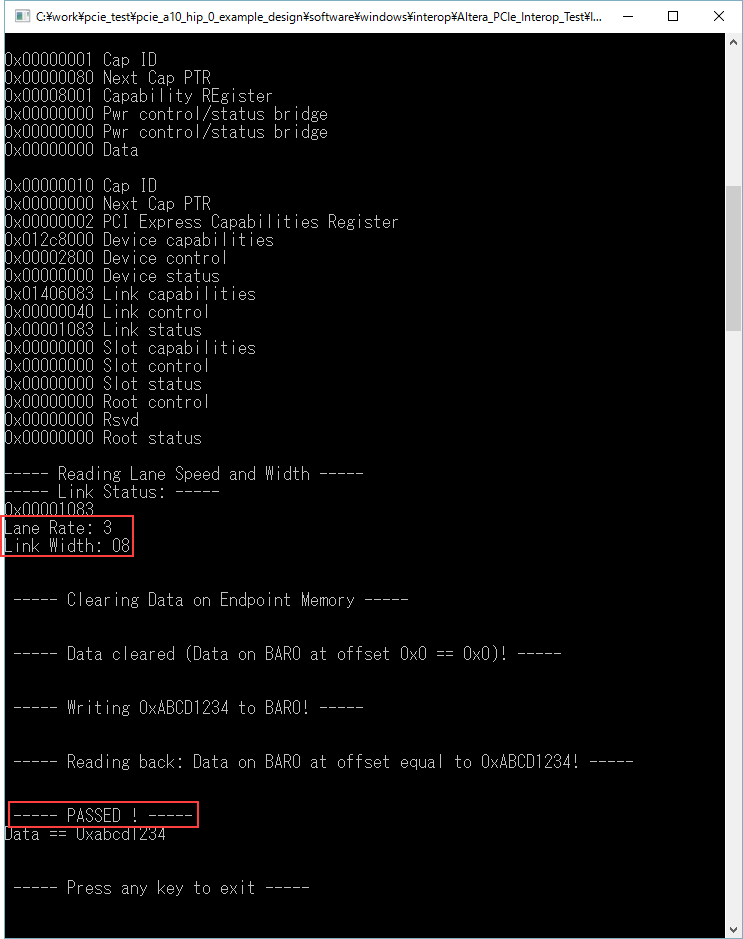

以下の、ログを見ると、Gen3(=Lane Rate:3)、x8(=Link Width : 08)が確認できます。

また、最後に、PASSED! と表示されると、簡単なデータの書き込み&読み出し&ベリファイが正常に終了したことになります。

Base Address 0 経由でのアクセスの確認ができたので、基本的なアクセスができたことが確認されました。

ユーザ・ガイド

Arria® 10 / Cyclone® 10 GX (Avalon-ST)

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug_a10_pcie_avst.pdf

Stratix® V (Avalon-ST)

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug_s5_pcie_avst.pdf

Arria® V (Avalon-ST)

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug_a5_pcie_avst.pdf

Cyclone® V (Avalon-ST)

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug_c5_pcie_avst.pdf

Stratix® IV / Arria® II / Cyclone® IV

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug_pci_express.pdf

おすすめ記事/資料はこちら

Altera® FPGA で PCI Express

Altera® FPGA で PCI Express(Avalon-MM 編)

FPGA の PCI Express デザイン & デバッグ・ガイドライン

Altera® FPGA の開発フロー/トップページ