Cyclone V SoC の Hard Processor System (HPS) には、Cortex-A9 MPCore をはじめとして ARM 社の IP ブロックが多く搭載されていますが、これら ARM 社の IP ブロックのレジスタ仕様やレジスタ・マップについては、ARM 社の技術ドキュメントを参照する形式を採っています。

インテル® FPGA の Web ページに HPS のレジスタ・マップが公開されていますが、この資料も ARM 社 IP のレジスタ仕様については ARM 社のドキュメントへリンクが掲載されるのみとなっています。

インテル® FPGA の Web ページの HPS レジスタ・マップは、下記リンク先を参照。

https://www.intel.com/content/www/us/en/programmable/hps/cyclone-v/hps.html

『ARM 社の IP ブロックのレジスタ仕様を知りたいが、参照すべきドキュメントが判らない。』という場合には、添付の PDF ファイルをご利用ください。

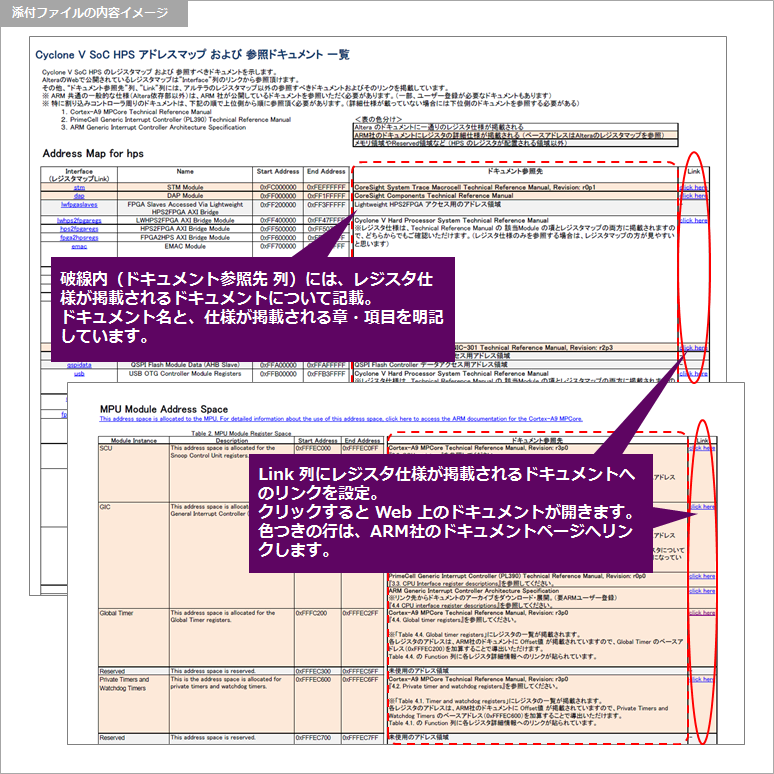

添付の PDF ファイルは、インテル® のレジスタ・マップをベースにした表の右側に「ドキュメント参照先」情報を追加した内容になっています。「Link」列をクリックすることで、参照すべき Web 上のドキュメントを直接開くことができます。

下図は、PDF ファイルの内容のイメージです。

おすすめ記事/資料はこちら

DS-5 活用テクニック ~ レジスタ・ビュー[1/3]基本設定

DS-5 活用テクニック ~ レジスタ・ビュー[2/3]レジスタ定義の自作

DS-5 活用テクニック ~ レジスタ・ビュー[3/3]FPGA 側のレジスタ表示