こんにちは。マクニカで Altera® FPGA 製品の技術サポートをしている アルテラ ハナコ です。

FPGA は、中身の論理回路をユーザーがゼロから設計します。そのため、さすがに全く何も知らない状態では設計できません。

では、一体どんなことを学べば良いのでしょうか。

Note: インテルのプログラマブル・ソリューションズ・グループは、2024年1月 インテル企業である Altera® になりました。

とりあえず手始めに、このあたりを学びましょう。

- デジタル論理回路についての知識

- ハードウェア記述言語とのコーディング能力

- I/O規格についての知識

- 静的タイミング解析(STA:スタティック・タイミング・アナライザー)についての知識

他にも知っていればもっともっと便利ですが、まずはこのあたりを知っておけば設計はスタートできます。

それぞれに関して、もう少しお話ししていきましょう。

デジタル回路についての知識

FPGA ではデジタル回路を設計します。ちなみに、FPGA の業界ではデジタル回路を 論理回路 と言うのが一般的です。

論理回路を構成するには、

- AND、OR、NOT、フリップフロップなどの基本論理回路

- 2進数、2進数演算

- 組み合わせ回路、順序(フリップフロップ)回路

- 同期式順序回路、非同期式順序回路

このあたりのことを勉強しておけば、基本的な回路は設計できます。(みなさんからリクエストがあれば、この辺の技術記事も書きますよ。)

ハードウェア記述言語のコーディング能力

論理回路を設計するためには、ハードウェア記述言語のコーディング能力が必要です。ハードウェア記述言語は通称 HDL (Hardware Description Language) と言われ、現在では主に以下の3種類が使用されています。

- VHDL(ブイエイチディーエル)

- Verilog-HDL(ベリログ・エイチディーエル)

- SystemVerilog(システム・ベリログ)

通常 ユーザーはどれか1種類を使用して設計します。(それぞれの特徴については、また別の機会に紹介します。)どのタイプの言語を選択するかは個人の自由です。会社で決められている人もいれば、設計依頼元の注文によって使い分けるために両言語をマスターする人もいます。それらの言語で、実現したい論理回路を記述します。

まずは基本的な文法を勉強してください。あとはサンプル回路をマネるなどして “言語で論理回路を表現すること“ に慣れてください。言語の文法習得はそれほど難しくはありません。それよりも、実現したい論理回路をどう言語で表現したら良いか、の方が頭を悩ませるかもしれませんね。

言語設計は、AND や OR、フリップフロップなどの最小単位のゲートロジックをスケマティック(回路図)設計のようにコツコツと記述するのではなく、もう少し大きな規模で “回路の動作” を記述します。

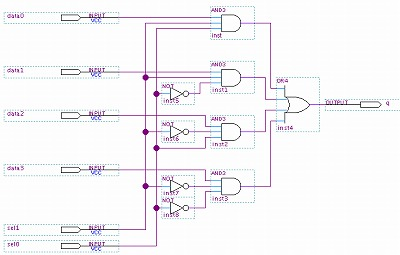

例えば、4入力1出力のマルチプレクサー(セレクター)はゲートで構成すると図1のようになります。

一方、同じ回路を VHDL で記述するとこのようになります。

Library ieee;

use ieee. std_logic_1164.all;

entity mux4to1 is

port (

data :in std_logic_vector (3 downto 0);

sel :in std_logic_vector (1 downto 0);

q:out std_logic

);

end mux4to1;

architecture logic of mux4to1 is

begin

process (data,sel)

begin

case sel is

when "00" => q <= data(3);

when "01" => q <= data(2);

when "10" => q <= data(1);

when others => q <= data(0);

end case;

end process;

end logic;図1のような AND や NOT などのゲートは一切記述されていませんよね?

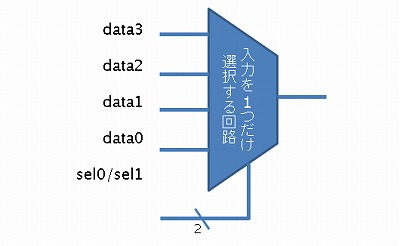

“4入力1出力のマルチプレクサー” と聞いて まず皆さんが頭に思い描いたのは、下のようなイメージ図ではないでしょうか。ユーザーは、どのような入力に対してどのように動作(出力)して欲しいかを記述し、箱の中のゲート構成は Quartus® Prime に考えさせればいい、これが言語設計なのです!

論理回路設計を学ぶ本やサイトを参考にする場合には、言語で設計することを前提としたものを見てください。そうでないと、せっかく効率的に論理回路を書ける言語を使っているのに、論理を式で表して回路記号(AND や OR)を並べて設計するような効率の悪い設計になってしまいます。基礎の勉強は大切なことですが、実務で求められているところはそこではありません。“動くもの(論理回路)を作る” と言うことが重要なんです。

とは言え、まずは言語に慣れましょう。その手始めに、“無料で受講できるトレーニング・コンテンツ” をご紹介します。

| トレーニング・コース名 | 概要 |

| VHDL 基礎編 (68分) (Altera® HPより) [日本語/無料] |

メーカー公式のオンライン・トレーニングです。 VHDL 言語の概要およびロジック・デザインでの使用例を学習します。 ★関連情報★ Altera® FPGA テクニカル・トレーニングを無料で受講しよう |

| Verilog HDL 基礎編 (49分) (Altera® HPより) [日本語/無料] |

メーカー公式のオンライン・トレーニングです。 Verilog HDL 言語の概要およびロジック・デザインでの使用例を学習します。 ★関連情報★ Altera® FPGA テクニカル・トレーニングを無料で受講しよう |

| はじめてみよう!VHDL はじめてみよう!Verilog-HDL [日本語/無料/演習問題つき] |

はじめて VHDL、Verilog-HDL でハードウェア論理回路の設計を行う方向けのページです。基礎の基礎から学習でき、演習を実施して理解を深めることができます。 |

ハードウェア記述言語の使い道は、論理回路を記述する以外にもう一つあります。”記述した論理回路のシミュレーション(動作検証)を実施するための言語”、いわゆる “テストベンチ” を記述するために使用します。

シミュレーションについては、下記ページをご覧ください。

テストベンチの記述については、下記ページをご覧ください。

I/O 規格についての知識

FPGA はデジタル IC です。I/O ピンに入力してきた信号(受信)に対して、それが「High(1)」なのか「Low(0)」なのかを判断し、接続先の IC に信号を出力(送信)することで、「High(1)」か「Low(0)」かを判断させ、周辺デバイスと通信します。High、Low とひとことで言っても、実際基板上では電圧値が関係します。“何V(ボルト)以上が High、何V以下が Low” と言うような電圧値の範囲に規定を設け、それぞれに名称を付けたもの、それが I/O 規格 です。

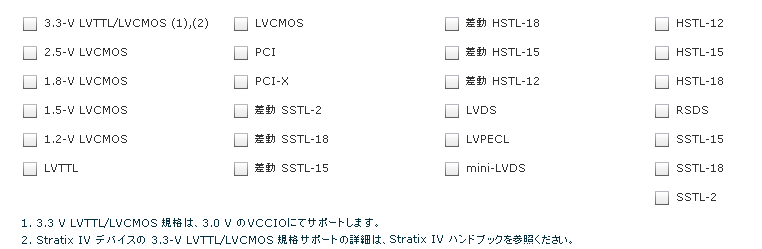

I/O 規格には様々な種類があり、現在 Altera® のデバイスでは、シングルエンド規格や差動規格など多彩な I/O 規格をサポートしています (下図は一部)。ただし全ファミリーが以下を全てサポートしているわけではありませんので、各ファミリーのハンドブックを確認してください。

先程お話しした “何V(ボルト)以上が High、何V以下が Low” と言うのはシングルエンド規格の考え方で、1つの信号がその規格で定められた電圧値よりも高いか低いかで High か Low かを判断させます。シングルエンド規格には LVTTL、LVCMOS などがあります。また、シングルエンド規格の中には、外部からリファレンス電圧を供給し その基準値との差で High か Low かを確定する規格もあります。

LVDS、LVPECLなどは差動規格です。2つの信号の電位差が規定値以上か以下かで High か Low かを確定させます。

Quartus® Prime で FPGA を開発する際、作成した論理回路の入力、出力、双方向ピンをターゲット・デバイスの各ピンに割り当て(アサイン)します。その際にピン番号だけでなく、各ピンをどの I/O 規格に準拠させたいのかオプション設定します。そのため、ユーザーは必要な I/O 規格の特徴を知っておいてください。

FPGA は1チップで複数の I/O 規格に対応させることができます。それは、FPGA が内部を動作させるための電源(通称 コア電源)と、I/O 端子が外部デバイスと通信するための電源(通称 I/O 電源)を別々に持っているからです。各 I/O 電源でドライブできる I/O ピンの領域(グループ)を “I/O バンク” と呼んでいて、Altera® FPGA は1チップ内に複数の I/O バンクを保有しています。I/O バンクごとに異なる電源電圧が供給できるため、FPGA は1チップで I/O 規格の異なる様々な周辺デバイスと接続することができます。

ユーザーは、FPGA と接続する周辺デバイスの I/O 規格は何か、またその I/O 規格の電気的特性を確認し、その I/O 規格をサポートできる FPGA ファミリーを選定します。また、選定した(または選定予定の) FPGA のデータシートを Altera® のホームページからダウンロードし、入出力の DC 特性を確認しなければなりません。

静的タイミング解析(STA:スタティック・タイミング・アナライザー)とタイミング制約についての知識

タイミング解析とは、自分が作成した論理回路が要求するクロック周波数で“正しく”動作するか、など タイミング仕様を満足するかどうかを確認することを言います。その解析手法のうち、QuestaSim などのシミュレーターを使い、入力信号データ(テスト・パターンあるいはテストベンチとも言います。)を用いて回路を疑似動作させるシミュレーションとは対照的に、テスト・パターンを使用せず、ユーザーが設定したタイミング要求(制約)に対して解析(比較検証)する手法を “スタティック(静的な)タイミング解析” と言います。

FPGA の回路素子には固有の遅延があるため、要求するクロック周波数が高速だったり論理回路の規模が大きいと、論理回路の一部が動かない可能性があります。そこでタイミング解析をおこない、仕様通り正しく動くことを確認しなければなりません。タイミング解析を「はぁ、面倒くさい。」と怠ると、FPGA はまず実機では動かないと言っても言い過ぎではないくらい、STA は現在の FPGA 開発において重要な作業の一つです。

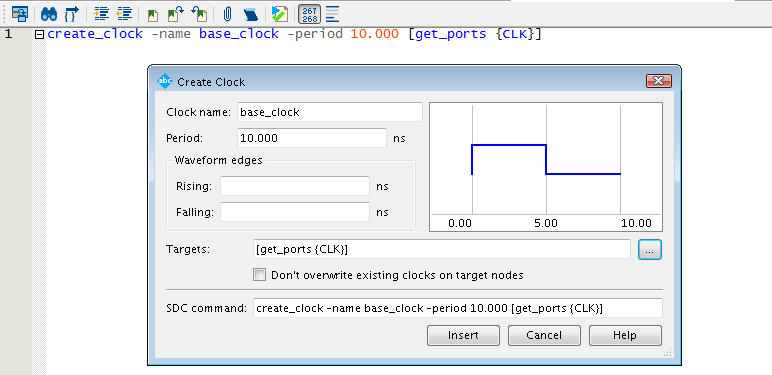

スタティック・タイミング解析をするには、ユーザーの回路に対するタイミング要求情報(タイミング制約)が必須です。そのタイミング制約を FPGA 開発ツールである Quartus® Prime に対して指示することで、ツールはそれを目標値として論理合成や配置配線(いわゆる “コンパイル”)を実行します。Quartus® Primeはタイミング制約に、ASIC 開発で標準的に使用されている “SDC(Synopsys Design Constraints)” ファイル・フォーマットを採用しています。

最も基本的なタイミング制約の例は、クロック周波数の指定です。これ以外にも、設計要求に応じてさまざまな制約が必要です。例えば、FPGA (ユーザー回路)の入出力ピンには入出力データの遅延制約が必要ですし、論理回路に複数のクロックがあれば、そのクロック同士の相関関係を制約として定義することが必要です。その内容を SDC ファイルに記述します。

「HDL で論理回路を書く他に、SDC も覚えなきゃならないの~?」と警戒しなくても大丈夫!SDC は HDL 言語のようにゼロから覚える必要はありません。開発ソフトウェア Quartus® Prime には、タイミング制約(SDC)を書くための専用エディターがあって、用意されたダイアログボックスに必要事項を入力すれば、コマンドがさらりと書けてしまいます。

ただし、SDC を書く前に、タイミングの基本概念(例えばセットアップタイムやホールドタイムと言った考え方)を知っておく必要があります。これを知らないと、どういった内容で制約を書けば良いかわかりませんし、回路構造に応じた適切なタイミング制約を与えないと正しい解析結果が得られません。

タイミング解析は FPGA 設計での必須の作業工程です。正しく動作する製品を作るために、タイミング制約や解析の知識を習得しましょう。

タイミング制約や解析に関する初心者向けオンラインセミナーが開催中です。

詳しくは 下記ページをご確認ください。

[オンラインセミナー] Altera® FPGA のタイミング解析 ~導入編~

今回は、どんなことを勉強しておいた方が良いのか ザックリとご紹介しました。これをきっかけに、知識を徐々に深めて行ってください。

次回は、FPGA 開発の流れ(手順)をご紹介します。

Note:

本記事では 読者に親しんでいただくためメーカーサイトは日本語ページをご案内していますが、併せて英語ページも必ずご確認ください。日本語ページは情報の更新が遅れる場合がありますので注意してください。サイト内の言語切り替えは、ページ下の REGION(地域)により行えます。なお、言語を切り替えてもすべてのページが日本語になるわけではありませんのでご了承ください。

おすすめ記事はこちら

ほんとのほんとの導入編 その1.FPGA 開発をはじめるための環境づくり

ほんとのほんとの導入編 その2. FPGA 開発をはじめるために準備するもの

ほんとのほんとの導入編 その3. FPGA 開発をはじめるために必要な知識

ほんとのほんとの導入編 その4. FPGA 開発の流れ

ほんとのほんとの導入編 その5. 役立つコンテンツの紹介