こんにちは。マクニカで Altera® FPGA 製品の技術サポートをしている アルテラ ハナコ です。

その1~その3と進んできて、FPGA を開発するための環境が整ったこところで、早速実践です。作業の進め方(フロー)をここで説明します。

FPGA 開発の流れ

FPGA の開発はざっくり 8工程(下図の2~9)あります。そのうち3および5~9番目の工程を Quartus® Prime で作業し、4番目の工程を Questa* - Intel® FPGA Edition などの EDA シミュレーターで作業します。

各工程のツールの操作マニュアルは、Altera® FPGA の開発フロー のページを参考にしてください。

1. 準備

FPGA 開発ソフトウェア Quartus® Prime を使用するためのパソコン環境の整備や、開発ソフトウェアのセットアップなど、準備をします。

詳細は以下のページを参考にしてください。

開発に必要なパソコン環境について

開発ソフトウェアのセットアップについて

2. 機能仕様の検討

システム仕様書に基づいて、FPGA に実装する機能(どのように処理させるか)を検討し、ブロック図、外部インターフェース、ブロック間インターフェースなど、仕様書にまとめます。

また、その仕様に見合った FPGA のファミリーを選定します。

予定している FPGA が固有に持つ内部機能、例えば PLL(ピーエルエル: Phase Locked Loop)や乗算器ブロック、RAM ブロックなどの機能や性能を採用する場合には、事前に FPGA 開発ソフトウェアの Quartus® Prime や、Questa* - Intel® FPGA Edition などのシミュレーターを使用し、簡単なサンプルデザインを作成したり論理検証(RTL シミュレーション)を実行して動作確認をおこなうなどしておきましょう。

3. 論理回路の設計

VHDL(ブイエイチディーエル)、Verilog-HDL(ベリログ・エイチディーエル)、SystemVerilog(システム・ベリログ)などの HDL(ハードウェア記述言語)を使い、論理回路の動作を記述します。専用の回路図(スケマティック)エディターでも設計できますが、近年は言語による設計が主流になってきています。これら、記述したものを主に “デザイン” と呼びます。

HDL は 汎用のテキスト・エディターでも記述できますが、Quartus® Prime に内蔵されたテキスト・エディターは、テンプレートやサンプル・デザインの挿入、文法に従い文字を色分けで表示する便利な機能など、汎用テキスト・エディターには無い工夫が施されていますので、おすすめです。

また、HDL は C プログラムのように記述の仕方によって回路の規模や速度が異なります。Quartus® Prime は ユーザーが設計したデザインをターゲット・デバイスのアーキテクチャー(構造)に応じて自動で最適に処理します。

FPGA に搭載されている機能ブロック(乗算器、メモリー、PLL、トランシーバーなど)を使用するには、Quartus® Prime の IP Catalog と言うツールを使います。IP Catalog にあらかじめ用意されている専用ブロックを選択し、ポート構成やパラメーターを選択および変更してカスタマイズします。その後ファイルを生成し、ユーザーのデザインに接続して組込みます。(IP: Altera® FPGA Intellectual Property の略)

Altera® FPGA Intellectual Property に関する情報は、以下をご覧ください。

4. 論理シミュレーション

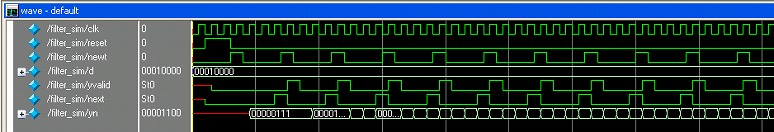

設計した論理回路(デザイン)の動作がユーザーの仕様要件を満たしているか、Questa* - Intel® FPGA Edition などのシミュレーターを使いパソコン上で論理動作の確認(検証)をします。

シミュレーション実行結果の確認方法は主にグラフィカルに表示された波形でもし仕様と異なる動作箇所があった場合には、設計した論理回路の記述が間違っていることになりますので、記述に修正を加え、再びシミュレーションで動作を確認します。この作業を繰り返し、論理回路の記述を仕上げます。

このとき、FPGA で実現する論理回路のデザイン以外に、検証対象回路への入力信号データ(テストパターンあるいはテストベンチとも言います。)が必要です。テストベンチは、仕様に応じたテストパターンの情報をユーザーが HDL 言語で記述し、これらをシミュレーターに読み込ませます。

テストベンチはユーザーが記述するため、この入力パターンが仕様と異なっていると、検証自体が無駄な作業になってしまいます。

初めて HDL 設計をするユーザーは、参考書などのサンプルソースを参考に、書き上げてください。

テストベンチの記述に関しては、以下の記事も是非ご覧ください。

5. 制約の設定

FPGA の開発では、デバイスのピンレイアウトをユーザー自らおこないます。

基板上の FPGA と周辺デバイスの配置環境に応じて、配線が短くなるように FPGA 側のピンの場所を決めます。

また、FPGA のピンには様々な機能(例えば、出力ピンのドライブ電流を変える機能や内部プルアップ抵抗、内部終端抵抗を有効にする機能など)が内蔵されています。そのピン機能をデバイスに適用させるには、Quartus® Prime においてオプションを設定しコンパイルすることで実現されます。

その他、FPGA の動作速度もユーザーがタイミング制約として設定します。FPGA は ASSP のように動作周波数が確定しているデバイスではなく、ユーザーの作成した論理回路の構成に依存します。勿論 FPGA の速度にも限界はありますので、採用を検討する段階で、投入するクロック周波数や周辺デバイスとのデータ転送速度などが実現可能なスペックを持つファミリーを選定する必要はありますが、希望のタイミング条件を設定することで Quartus® Prime のコンパイラーが最適なゲート構成と配置を実現してくれます。

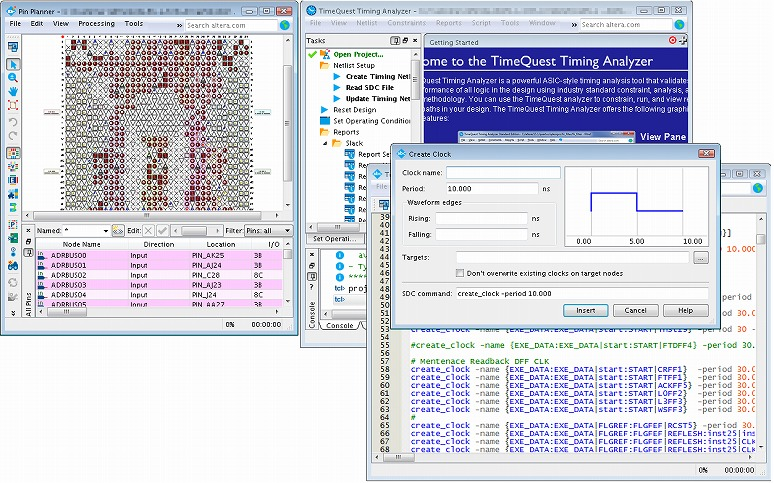

これらの制約は、コンパイル(論理合成と配置配線)の実行前に Quartus® Prime で設定入力しておく必要があるのですが、Quartus® Prime を初めて使うユーザーでも簡単に操作できるよう、Pin Planner(ピン・プランナー:左図)や Timing Analyzer(タイミング・アナライザー:右図)と言うグラフィカルなツールを採用しています。また、タイミング制約には、ASIC 設計で標準的に使われている SDC フォーマットが採用されています。その SDC コードを作成するためのウィザードも補助機能として用意されているので、SDC フォーマットを知らないユーザーも簡単にタイミング制約を記述することができます。

6. コンパイル

デザイン作成が終了し各種制約の設定を行った後、“コンパイル” を実行します。

コンパイルとは主に「論理合成」と「配置配線」をおこなう作業の総称です。Quartus® Prime では、画面上のアイコンをクリックするだけでこれら一連の作業が始まり、そのあとは自動的に実行されます。

“論理合成” とは、ユーザーが HDL 記述言語や回路図で作成したデザインを、AND やフリップフロップなどの具体的なゲート回路に変換する作業のことで、Quartus® Prime が使用する FPGA の構造に最適なゲート構成で自動的に変換します。

その後、使用する FPGA の構造に応じて内部のロジック配置や、ユーザーの指定通りにピンの位置を決め、ロジック同士やロジックとピン間の配線を自動で行います。これを “配置配線” と言います。

コンパイルが終了すると各種コンパイルの処理結果がレポートとして生成され、内容の確認ももちろん GUI でおこなうことができます。

7. タイミング検証

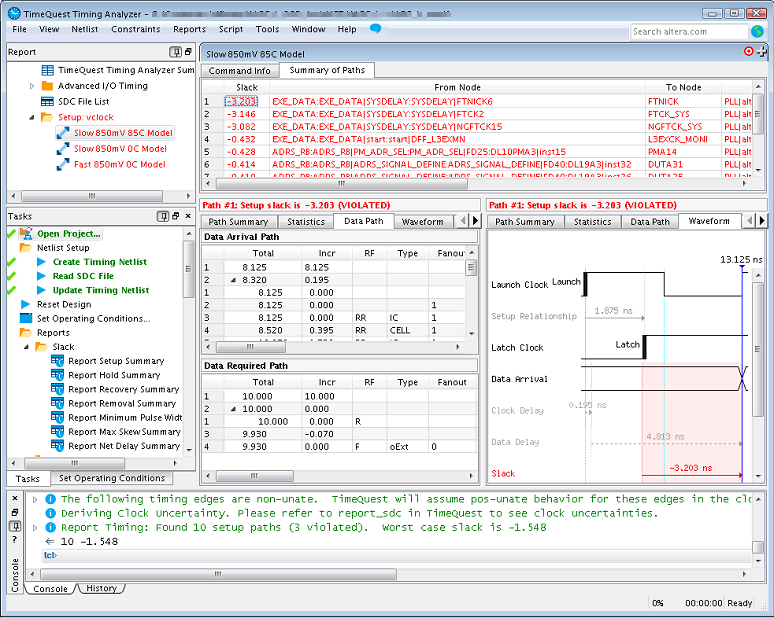

コンパイルレポートの中にはタイミング解析結果も記録されています。

ユーザーは、デバイスに実装する回路が要求した速度で動作するか(タイミング制約で設定した要求値を満たせたか)を確認しなければなりません。コンパイルレポート内のタイミング解析結果はサマリー情報だけなので、詳細な結果を確認するには Quartus® Prime に搭載された Timing Analyzer(タイミング・アナライザー)を使用し、スタティックに検証します。

もし要求値を満足していない結果の場合には、Quartus® Prime のオプションを活用し、配置配線のアルゴリズムを変えたり、デバイスの機能を適用させて再度コンパイルを実行し、内部のレイアウト変更をおこなうことで改善を図ります。

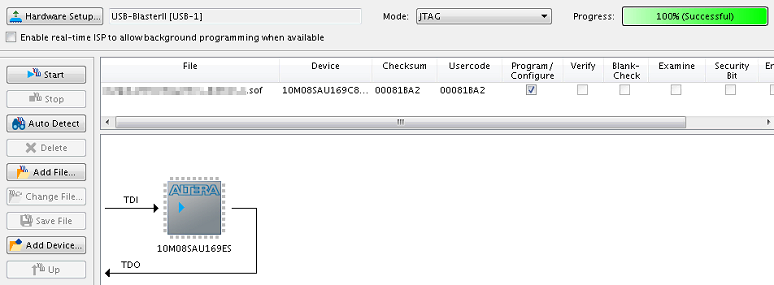

8. プログラミングする

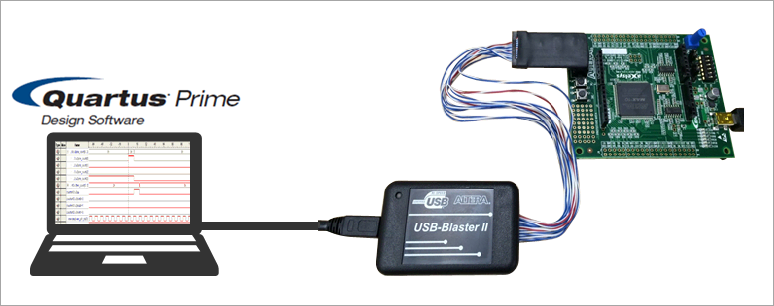

タイミング解析でユーザーの要求どおりに回路が正しく動作することが分かったら、開発基板上の FPGA を実際に動作させるため Quartus® Prime で生成された回路データをパソコンから FPGA に転送します。このことを “プログラミング” (ダウンロードともいう)といいます。

ユーザーは Altera® FPGA ダウンロード・ケーブルの USB-Blaster™ II と Quartus® Prime に付属した Programmer というユーティリティーを使ってプログラミングをおこないます。

多くの FPGA はプログラム素子に SRAM を使用しているため、ボード上にブートメモリー用の不揮発性メモリーを用意しなければなりません。Altera® では不揮発性メモリー用デバイスを “コンフィグレーション ROM” といい、このメモリに対してプログラミングをおこないます。FPGA はボード上でこのコンフィグレーション ROM からデータを転送してもらい、はじめて動作します。このことを “コンフィグレーション” と言います。

ただし MAX® 10 FPGA ファミリーだけは例外です。MAX® 10 はブートメモリーをデバイスに内蔵しワンチップ化した新しいタイプの FPGA です。そのため、MAX® 10 の場合は、外付けのブートメモリーは必要ありません。

9. 実機検証

ボードの電源を再投入し、コンフィグレーションROMから FPGA にデータが正常に転送されれば、FPGAの動作を確認するフェーズに入ります。

動作に不具合があった場合に、一般的にはロジックアナライザーやオシロスコープで信号検証をおこないますが、簡易的な信号検証であれば、Quartus® Prime には Signal Tap と言うオンチップデバッグ機能があります。これは、Altera® の FPGA 内部でロジアナを構成するようなデバッグ方法(仕組み)で、特殊な機器は一切必要なく、Quartus® Prime のインストールされたパソコンと、検証する FPGA が搭載した基板、ダウンロード・ケーブルの USB-Blaster™ II があれば、すぐにデバッグ作業ができます。SignalTap はライセンス不要で利用することができ、無償の Quartus® Prime Lite Edition でも使用可能です。

Signal Tap についてざっくり知りたい人、やってみたい人は、以下の記事をご覧ください。

Signal Tap の詳細は、下記のメーカー資料および メーカーのホームページで公開されているオンライン・トレーニング(無料)をご覧ください。

- Design Debugging with the Signal Tap Logic Analyzer (Quartus Prime Standard Edition)

- Design Debugging with the Signal Tap Logic Analyzer (Quartus Prime Pro Edition)

なお、オンライン・トレーニングの受講方法は、下記コンテンツをご覧ください。

10. 量産

実機検証が完了すれば すぐに量産へ移ることができます。

以上が一般的な FPGA 開発の流れです。

さぁやってみましょう!

・・・と言っても、FPGA の開発をしたことがないのに仕様を考えるところからいきなり始めるのは無謀です。まずは真似ることから始めてみましょう。

Altera® や Mpression(マクニカのオリジナル・ブランド)がリリースしている評価ボードには、リファレンス・デザイン(サンプルデザイン)とユーザーガイド(マニュアル)が用意されています。購入前でも後でも、あるいは購入しなくてもホームページの評価ボードの掲載ページからサンプルデザインのデータをダウンロードできます。

この他、評価ボードのページ以外でもサンプルデザインを入手する方法があります。詳しくは、下記コンテンツをご覧ください。

評価用基板が手元にまだなくても、作業3~作業7までの工程なら すぐに作業に取り掛かれます。

まずは、ツール操作に慣れましょう。

Quartus® Prime を使いこなせるかが FPGA 開発の近道と言っても過言ではありません。

いち早く使用方法を習得するには、講師付きのトレーニングがおすすめです。

ご不明点がございましたら、弊社の担当者 または 半導体製品専用 お問い合わせフォーム へお問い合わせください。

「ほんとのほんとの導入編」、このシリーズは次回で終了です。最終回の “その5” では、FPGA や CPLD を勉強するために便利な WEB サイトをご紹介します。

Note:

本記事では 読者に親しんでいただくためメーカーサイトは日本語ページをご案内していますが、併せて英語ページも必ずご確認ください。日本語ページは情報の更新が遅れる場合がありますので注意してください。サイト内の言語切り替えは、ページ下の REGION(地域)により行えます。なお、言語を切り替えてもすべてのページが日本語になるわけではありませんのでご了承ください。

おすすめ記事はこちら

ほんとのほんとの導入編 その1. FPGA 開発をはじめるための環境づくり

ほんとのほんとの導入編 その2. FPGA 開発をはじめるために準備するもの

ほんとのほんとの導入編 その3. FPGA 開発をはじめるために必要な知識

ほんとのほんとの導入編 その4. FPGA 開発の流れ

ほんとのほんとの導入編 その5. 役立つコンテンツの紹介