こんにちは。

マクニカでインテル® FPGA 製品の技術サポートをしている インテル・F・ハナコ です。

みなさんは、インテルの FPGA を実機デバッグするときに、オシロやロジアナ以外のデバッグ方法があるのを知っていますか?

それは Signal Tap(シグナル・タップ)です!!

※ SignalTap® II は Quartus Prime 17.1 から Signal Tap へ名称変更されました。

正式名は Signal Tap ロジック・アナライザー。

簡単に説明すると、FPGA にインプリメントしたユーザー回路の内部信号をモニタリングする Quartus® Prime のロジアナ機能です。

その特徴は

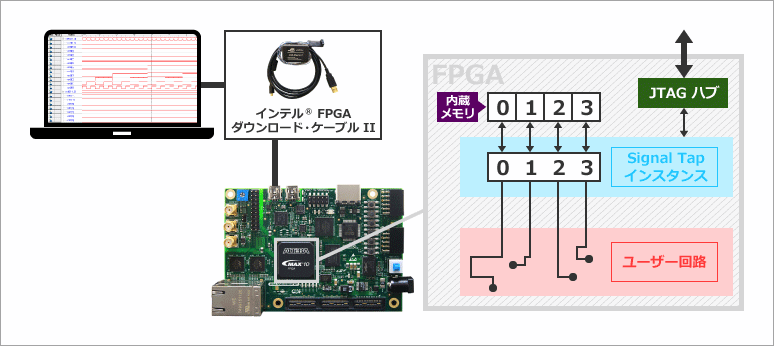

- FPGA 内部のロジック・エレメント(LE)とメモリの空き領域に、Signal Tap の IP をインプリメント

- Quartus® Prime の画面で観測データを表示

- 基板と Quartus® Prime の通信手段は、インテル® FPGA ダウンロード・ケーブル II などのプログラミングに使用するダウンロード・ケーブルを使用

- 観測信号のモニターピンは FPGA の JTAG ピンを使用

- デバッグ用にユーザー I/O ピンを確保する必要なし!

- ロジアナやオシロなどの外部機器も不要!

- 無償で使える!

準備しよう

FPGA で Signal Tap ロジック・アナライザーを実行するには、これらが必要です。

|

FPGA の搭載されたボード |

対象デバイス Intel® Agilex シリーズ / Stratix® シリーズ / Arria® シリーズ / Cyclone® シリーズ / MAX® 10

|

|

開発ソフトウェア |

Quartus® Prime Pro Edition / Quartus® Standard Edition / Quartus® Lite Edition

|

|

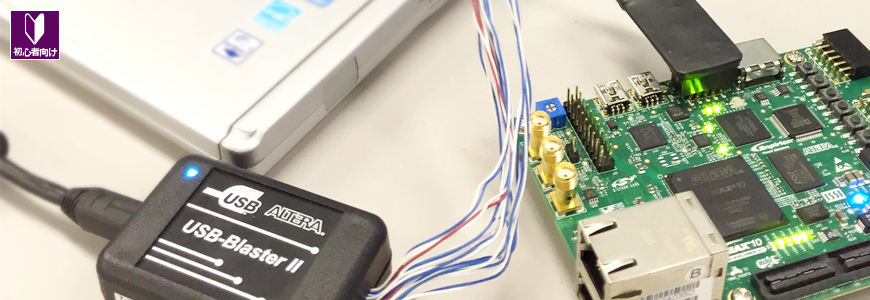

ダウンロード・ケーブル |

インテル® FPGA ダウンロード・ケーブル II(旧 USB-Blaster™ II)

|

どんな作業をするのか

作業はたったの 4ステップ!

|

Step 1 |

Step 2 |

Step 3 |

Step 4 |

なお Signal Tap を実施するユーザーデザインは、事前に論理合成あるいは配置配線が完了している必要があります。

実際にやってみよう

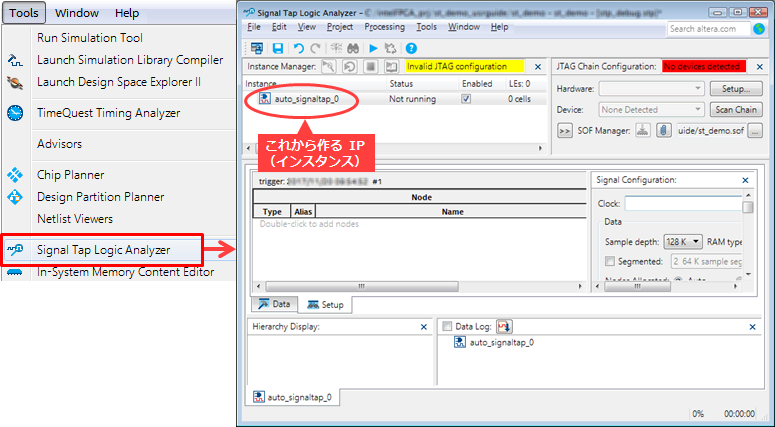

1. Signal Tap IP の作成

STP ファイルを新規に作成します。このシートに条件を設定していくと、IP が作れちゃうんです。

- サンプリング・クロックを指定

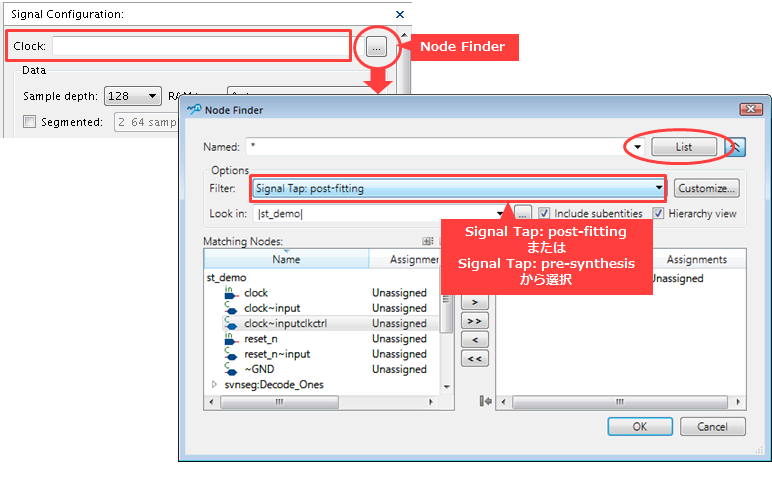

Signal Configuration ウィンドウにおいて Signal Tap が動作するためのクロックをユーザー回路から選びます。

Signal Tap は立ち上がりエッジでモニター信号をサンプリングします。

通常のロジアナと同様、モニター信号の観測精度はサンプリング・クロックの周波数に依存します。

FPGA 外部からクロックを別途供給することも可能です。

Node Finder の使い方は、下記ドキュメントを参考にしてください。( “Node Finder” をキーワードに検索してください。)

Quartus® Prime - 制約の方法(Assignment Editor)

- モニター信号を選択

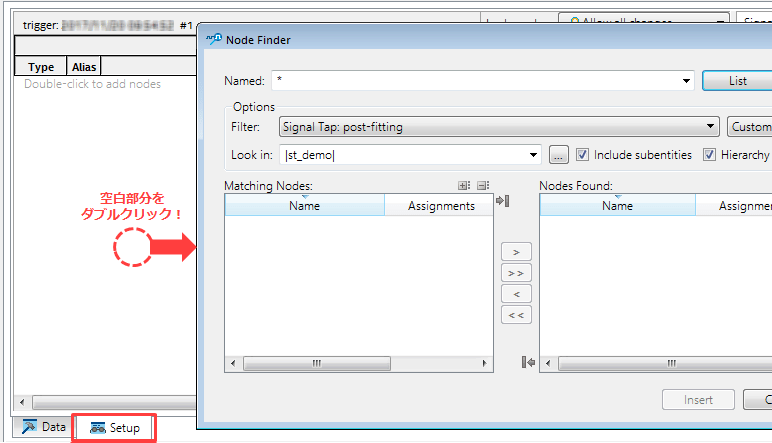

NodeFinder を使って観測する信号を選択します。選択した信号はトリガー条件にも使用できます。ただしサンプリング・クロックに指定した信号はモニターできません。

ハナコのちょこっとポイント♪

観測する内部信号を STP ファイルに登録するときに、Node Finder を使わない方法があるんです。

それは Technology Map Viewer の活用!

視覚的に信号を選択してヒョイッと簡単に登録できますよ。私がオススメの方法です。

詳しくは、こちらの記事をご覧ください。

Signal Tap でキャプチャしたい内部信号を簡単に STP ファイルに登録する方法

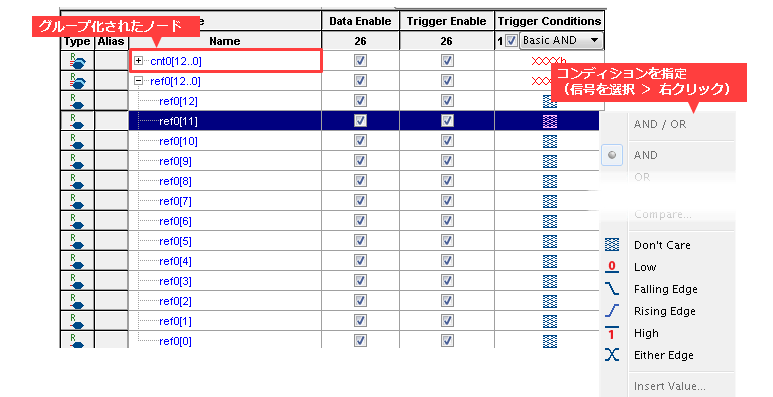

- トリガー・コンディションを設定

トリガー条件に用いたい信号に対して、コンディションを選択します。

2. ユーザーデザインに Signal Tap IP をインプリメント & コンパイル実行

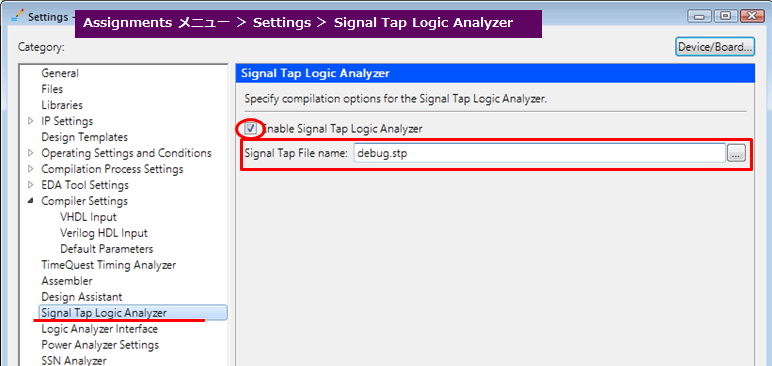

STP ファイル上の File メニュー > Save As で STP ファイルに名前を付け保存します。

「Do you want to enable Signal Tap File “ファイル名.stp” for the current project?」とメッセージが表示されるので、Yes を選択するとプロジェクトに登録されます。(下図は確認方法)

これで Signal Tap のインプリ完了!!コードによる接続作業は一切ありません。

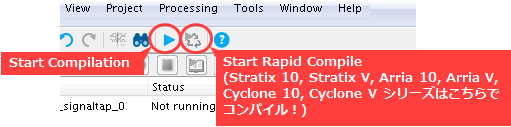

その後、STP ファイル上のアイコンをクリックして Signal Tap IP を含んだユーザー・デザインのコンパイルを実行します。

3. .sof を FPGA へダウンロード

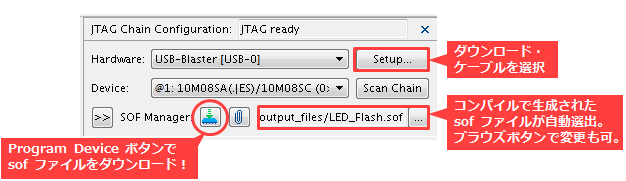

STP ファイル内(右上)の JTAG Chain Configuration ウィンドウでダウンロード・ケーブルを選択、および転送する sof ファイルを確認します。その後、Program Device ボタンをクリックしてダウンロード開始!

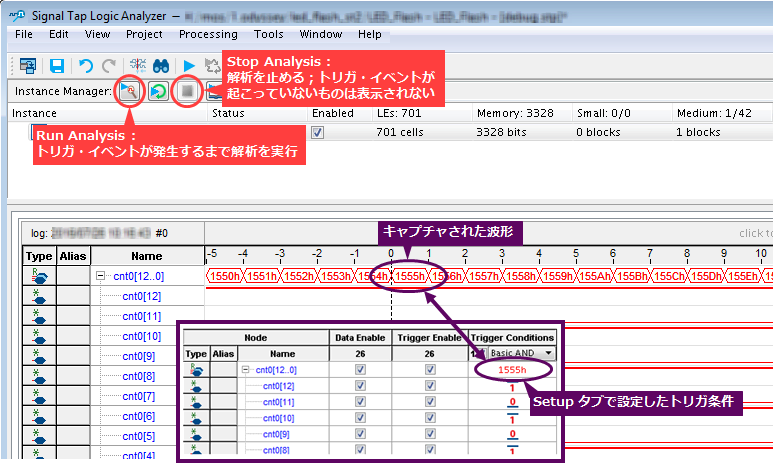

4. サンプリング・データの 取得および観測

Run Analysis ボタンをクリックすると、トリガーのイベントにヒットした最新のサンプリング・データが STP ファイルに表示されます。

トリガー・コンディションの High や Low を変更するだけなら、再コンパイルの必要はありません。

値を変更後に即座に Run Analysis ボタンをポチッ♪とするだけです。

ね、簡単でしょ♪

FPGA の内部信号をちょこっと観測したいだけだったら、ロジアナなどの大型機材を引っ張りださずに Signal Tap で手軽にデバッグができます。

ハナコのちょこっとポイント♪

Signal Tap IP をインプリメント後の再コンパイルは、コンパイル時間の拡大とレイアウトへの影響がデメリットとして考えられますが、Quartus® Prime のインクリメンタル・コンパイル機能を併用することによりユーザーはこのストレスを軽減することができます。(Lite Edition はインクリメンタル・コンパイルをサポートしていないため併用できません。)

また デバッグ中に、Signal Tap インスタンスの追加/削除、サンプリングする信号やトリガー条件に用いる信号の追加/削除、サンプリング・クロックの変更などの Signal Tap IP の回路構成に影響のある変更をした場合は、再びコンパイルが必要です。

詳しくは、下記ドキュメントをご覧ください。

Design Debugging with the Signal Tap Logic Analyzer (Quartus Prime Standard Edition)

Design Debugging with the Signal Tap Logic Analyzer (Quartus Prime Pro Edition)

最後に

今回は Signal Tap ロジック・アナライザーをご紹介しました。

Signal Tap ロジック・アナライザー機能をいち早く試したいそこのアナタ!

以下のチュートリアル、サンプルデザイン、対応した評価キットおよび開発キットを用いて、Signal Tap IP の作成から実機デバッグ実行までの作業フローを簡易的に体験してみましょう。ぜひご活用ください。

◆ チュートリアル : ドキュメント

quartus_signaltap_tutorial_v1710_r1__1.pdf

◆ チュートリアル : Cyclone® 10 LP FPGA 評価キット用サンプル・デザイン

◆ チュートリアル : MAX® 10 FPGA 評価キット用サンプル・デザイン

◆ チュートリアル : デザインのみのプロジェクト

Quartus® Prime Lite Edition 16.0 以前のバージョンで SignalTap® II (現 Signal Tap) を使えるようにするには、"おまじない" が必要です。

そのおまじないとは 「TalkBack 機能を有効にする」 こと!

以下の手順に従い、TalkBack 機能を有効にしてください。

- Tools メニュー ⇒ Options を選択

- Options ウィンドウ内の Category から Internet Connectivity を選択

- Internet Connectivity ダイアログ・ウィンドウで、TalkBack Options ボタンをクリック

- TalkBack Options ウィンドウで、Enable sending TalkBack data to Altera オプションに ✔ (On)

たったこれだけ!

[関連 FAQ] TalkBack 機能とは何ですか?

おすすめ記事/資料はこちら

Quartus® はじめてガイド - Signal Tap ロジック・アナライザの使い方

Signal Tap(旧 SignalTap® II)に関する FAQ 一覧

商品の購入はこちら

インテル® FPGA ダウンロード・ケーブル II(旧 USB-Blaster™ II)

インテル® FPGA ダウンロード・ケーブル (旧 USB-Blaster™)

インテル® FPGA イーサネット・ ケーブル II(旧 EthernetBlaster™ II)