この「Quartus® はじめてガイド」シリーズは、インテル® Quartus® Prime / Quartus® II 開発ソフトウェアを初めてご利用になるユーザ向けの資料です。

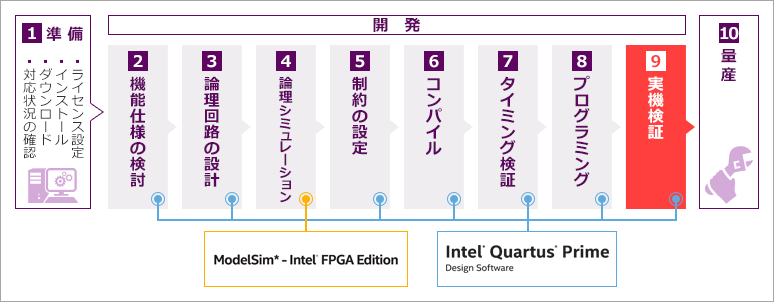

FPGA / CPLD の開発フローについては、こちらを参照してください。

説明

この資料は、FPGA / CPLD 開発の『9. 実機検証』フェーズで参考になります。

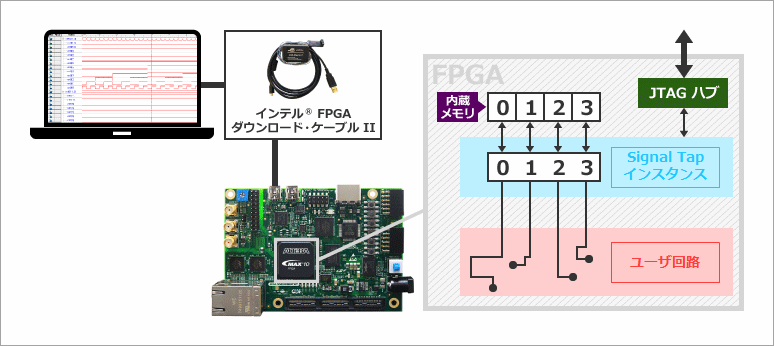

Quartus® Prime には、ユーザ・デザインを FPGA 上で動作させながら未使用の I/O ピンを活用することなく内部信号の動作を検証できるオンチップ・デバッグ環境 Signal Tap ロジック・アナライザが標準搭載されています。

この資料は、Signal Tap ロジック・アナライザの使い方について説明しています。

現在の FPGA は大規模で高性能となっている反面、パッケージや未使用 I/O ピンの制限などにより、デバッ

グは困難になっています。インテルではその現状を緩和するために、デザインを FPGA 上で動作させながら未

使用の I/O ピンを活用することなく内部信号の動作を検証できるオンチップ・デバッグ環境 Signal Tap ロジッ

ク・アナライザ(以下、Signal Tap)を提供しています。

この Signal Tap 機能は、Quartus® Prime に標準搭載されたオンチップ・デバッグ・ツールで、ロジック・アナラーザやオシロスコープなどの外部測定装置を使用せずに、ボード上で動作する FPGA の内部信号の状況をキャプチャおよび表示することができます。

無償の Signal Tap 用 IP コアをユーザ・デザインに組み込みデバイス内部に配置配線し、データをプログラミング後ボード上で動作させます。キャプチャされたデータはデバイスの内部メモリ領域に一度格納され、その後、ボード上の JTAG ピンから通信ケーブルを経由して Quartus® Prime に転送され、パソコンの画面上に波形表示されます。Signal Tap は、1 つの JTAG チェーン内に複数の FPGA デバイスを含んだボード環境でも実行できます。

なお この Signal Tap は、Quartus® Prime v17.0 以前のバージョンで搭載されていた SignalTap II と同じ機能で

す。v17.1 より名称が変更されました。(【TIPS】参照)

資料

「Quartus Prime はじめてガイド - Signal Tap ロジック・アナライザの使い方(ツール・バージョン:Ver.17.1 用ドキュメント)

おすすめ記事/資料はこちら

FPGA オンチップ・デバッグ "Signal Tap" をやってみよう

Quartus® Prime 関連の記事や資料

インテル® FPGA の開発フロー/FPGA トップページ

おすすめ FAQ はこちら

おすすめセミナー/ワークショップはこちら

Quartus®Prime 入門編トライアル・コース <無料>

カスタムマイコン設計トライアル ~MAX® 10 FPGA を使った組込み設計を体感!~ <無料>