こんにちは。

マクニカで インテル® FPGA 製品の技術サポートをしている インテル・F・ハナコ です。

Quartus Prime に標準搭載されているオンチップ・デバッグ機能 Signal Tap ロジック・アナライザ ですが、

みなさんは、どのようにして FPGA の内部信号を線選出していますか?

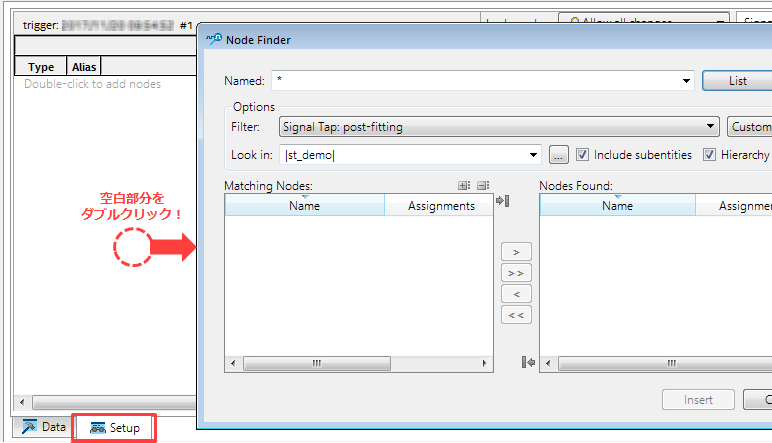

STP ファイルにユーザー回路のモニタしたい内部信号を登録するとき、通常だと Node Finder というノード検索ウィンドウを使用して選択します。

でも Node Finder で信号を見つけ出すのって、信号名が文字だけなので

自分のデザインのどの部分なのかがイメージしにくいし、Quartus® Prime 作業経験があまりないユーザーさんには正直言って選び難いですよね。

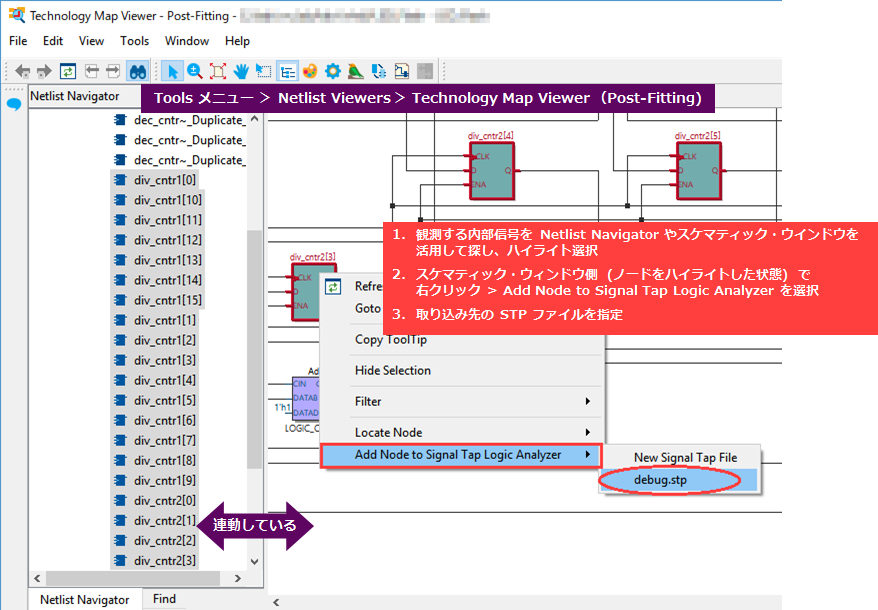

そんなとき、私がオススメする内部信号の選択方法は Technology Map Viewer の活用 です!!!

Technology Map Viewer は、自分のデザインの論理合成前および配置配線後のネットリストがグラフィカルに表示されるビューワです。

Post-Mapping と Post-Fitting の2タイプが用意されていて、今回 Signal Tap で活用するのは Post-Fitting のビューワです。

上図のように、Technology Map Viewer(Post-Fitting) でモニタしたい内部信号を視覚的に検索し、STP ファイルにインポートさせます。

このビューワをはじめて使うユーザーさんもいるかもしれませんが、Signal Tap 以外にもタイミング解析など様々なデバッグと連動して利用できるビューワ機能なので、是非是非使ってみてください。

Technology Map Viewer をはじめとする各 Netlist Viewer を使いこなせると、もっとデバッグが楽になりますよ♪

お試しあれ!