デバイスの遅延時間の条件が 0pF ではなく、25pF や 50pF などの大きな負荷容量で規定されていることがありますが、なぜでしょうか?話は、TTL (Transistor Transistor Logic) の時代にさかのぼります。

また、『クランプダイオードによる反射抑制』も参照下さい。

標準ロジックのデータシート(Texas Instruments 社)

例)SN7400(クワッド 2入力 正論理 NAND ゲート)

ファン・インとファン・アウト

今ではほとんど用いない用語ですが、TTL 時代には常に気をつけていました。(脚注1)ハイ側でも同様ですが、ロー側で説明します。

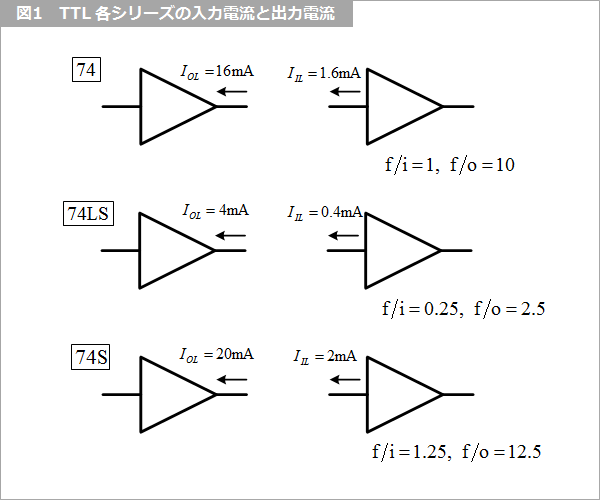

図1 は、TTL の入力電流と出力電流です。第一世代の 74シリーズと、第二世代の低消費電力の 74LS および高速の 74S シリーズについて示します。74LS と 74Sはショットキークランプのため VOL が高くなって、特に、74 の 0.4Vに対して、74S は 0.5V となっており、整合がとれませんが、ノイズバジェットで調整をとっていました。最初に現れた、74 シリーズの入力のファン・イン(f/i)を 1、出力のファン・アウト(f/o)を 10 と定義しました。第一世代の 74 と第二世代の 74LS および 74S との相互接続が必要なので、74LS のファン・インを 0.25、ファン・アウトを 2.5 とし、74S のファン・インを 1.25、ファン・アウトを 12.5 としました。

表1 は、この関係を示したもので、それぞれのファミリー内は、10個の負荷を接続出来、例えば、74S に 74 の負荷は 12.5 個接続出来ます。個数に 12.5 のように小数点以下が生じるのは、74 を 12 個と 74LS を 2個のような場合を想定しています。

| 入 力 | ||||

| 74(1) | 74LS(0.25) | 74S(1.25) | ||

| 出 力 |

74(10) | 10 | 40 | 8 |

| 74LS(2.5) | 2.5 | 10 | 2 | |

| 74S(12.5) | 12.5 | 50 | 10 | |

※( )内は、ファン・インとファン・アウト

入力容量

74 シリーズの TTL の入力は、およそ1.5pF です。ファン・アウトが 10 なので、負荷を最大に接続すると、1.5×10=15pF となります。この容量を適用して、当初の TTL の遅延時間の測定条件は、負荷容量 15pF で規定されていました。表1 において、最大の負荷の個数を接続出来るのは、74S の出力に 74LS の入力を接続した場合で、74S の出力は、74LS を 50個接続することが出来ます。

ここからは一部推測ですが、74LS シリーズは、入力容量が 74 シリーズより小さく、1pF とすると、負荷容量 50pF となります。74 シリーズの遅延時間の測定は、入力波形の立ち上がり時間が 7ns と規定されていたので、ほとんど集中定数と考えられました。(脚注2)

TTL は標準ロジックと呼ばれていたので、世代が変わっても、相互に接続する必要があるので、昔の規格との上位互換の必要がありました。さらに、昔のデータシート(今でもときどき)には、負荷容量には、ジグ(jig)とプローブの容量も含むと注意書きがあります。これはさすがに改めるべきでしょう。

どうすればよいか

実使用ではパターンが接続されるだけなので、負荷容量は 0pF です。したがって、無負荷の状態の遅延時間を、保証値ではなく、標準値(typ)として記載すればよいと考えます。一時期、このような規定がありましたが、いつの間にかなくなってしまったのは残念です。ないものねだりしても仕方がないので、負荷容量が 0pF のときの遅延時間を推測します。ibis データの [Pulldown] または [Pullup] から、ドライバの出力抵抗を求めます。

『特性インピーダンスとドライバの駆動能力』を参照下さい。

さらに、『IBIS モデルを用いた反射の解析 ~その2』を参照して、ibis データの [Ramp] データから、出力波形の立ち上がり時間を求めて、複数の負荷容量 CL に対して SPICE 解析して遅延時間を求めます。このときの SPICE は、フリーで提供されているもので十分です。または、ランプ波形と CR 積分波形の過度現象を解いても求めることが出来ます。

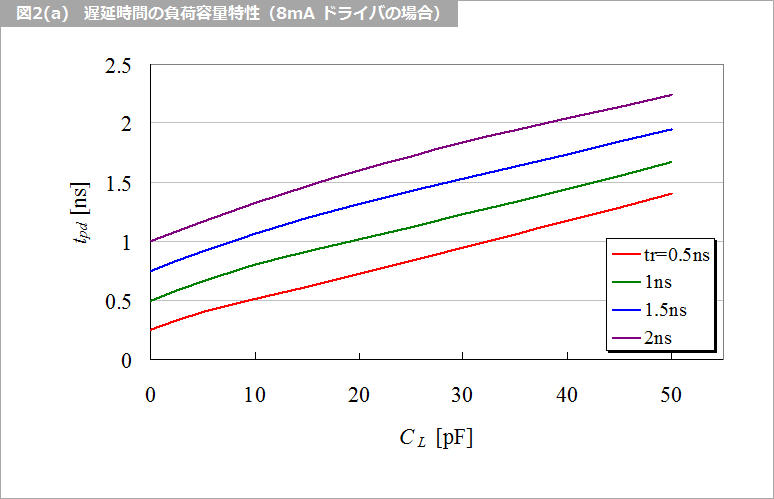

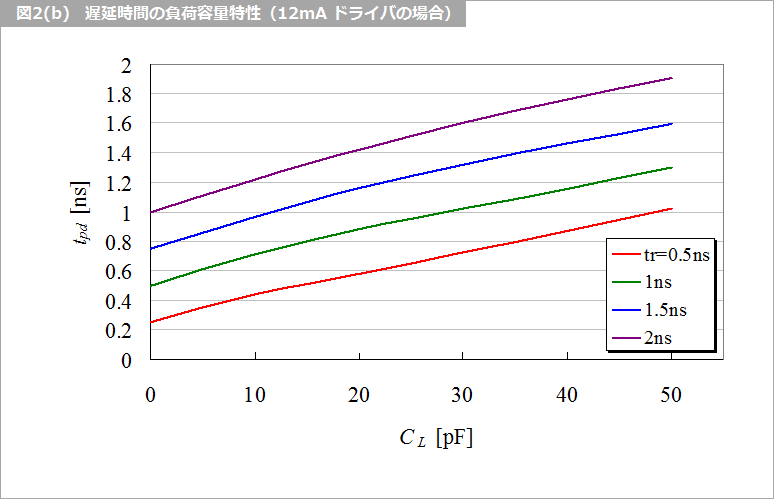

図2(a) はドライバの出力抵抗が 33Ω、すなわち 8mA の例で、図2(b) は 22Ω すなわち 12mA ドライバの例です。負荷容量が 50pF で規定されていれば、この解析結果から、負荷容量が 0pF との遅延時間の差を求めて、データシートの値から差し引けば、0pF のときの遅延時間を求めることが出来ます。

脚注1

TTL 時代には、数ゲートの IC を組み合わせて論理を構成していました。したがって、一つの出力に、数個の入力を接続する必要がありました。TTL は CMOS と違って、比較的大きな入力電流が存在し、入力を複数個接続すると、合計の電流値が大きくなり、接続出来る入力の数を規定する必要がありました。現在は、ゲートを組み合わせて論理を組み立てることはほとんどなく、主力の CMOS は入力電流が小さいので、このようなことを考えることはほとんど必要なくなりました。

脚注2

配線パターンの遅延時間は、7ns/m 程度なので、立ち上がり時間が 7ns の場合、分布定数線路とみなす配線長は 50cm で、通常の配線はこれ以下なので、配線は集中定数とみなすことが出来ます。

『分布定数回路と集中定数回路の境界線』もあわせて参照下さい。

碓井有三のスペシャリストコラムとは?

基礎の基礎といったレベルから入って、いまさら聞けないようなテーマや初心者向けのテーマ、さらには少し高級なレベルまでを含め、できる限り分かりやすく噛み砕いて述べている連載コラムです。

もしかしたら、他にも気になるテーマがあるかも知れませんよ!