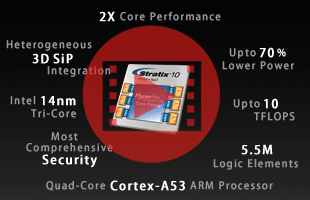

Stratix® 10 FPGAs & SoCs deliver industry-unprecedented breakthrough advantages in performance, power efficiency, density, and system integration. Built on Intel's 14nm Tri-Gate process with innovative HyperFlex™ core fabric architecture, Stratix 10 devices deliver 2x core performance and up to 70% less power than previous generation high-performance FPGAs achieve reductions.

View Stratix 10 Family List >>

Stratix 10 FPGA & SoC system integration includes the following breakthroughs:

- Heterogeneous 3D SiP (System-in-Package) integration

- Up to 5.5M LE equivalent logic, industry's highest density monolithic FPGA fabric

- IEEE 754 compliant single-precision floating-point DSP with up to 10 TFLOPS throughput

- Secure Device Manager (SDM) with the most comprehensive security features

- Powered by a quad-core 64-bit ARM® CortexTM-A53 hard processor system up to 1.5 GHz

- Optimized and Validated Complementary Enpirion® Power Solutions

These unprecedented capabilities make Stratix 10 devices the next-generation high-performance systems in virtually every end market, including wireline/wireless communications, computing, storage, military, broadcast, medical, and test & measurement equipment. address the design challenges of

Features of Stratix 10 FPGAs and SoCs

Industry's Highest Performance FPGA & SoC for Performance Breakthroughs

- Breakthrough HyperFlex Architecture Delivers 2x Core Performance Increase

- Up to 10 TFLOPS of single precision floating point DSP performance

- Quad-core 64-bit ARM Cortex-A53 hard processor subsystem up to 1.5 GHz

Eliminate bandwidth barriers

- Up to 144 transceivers with data rates up to 30 Gbps, delivering 4x the serial transceiver bandwidth of previous generation FPGAs for high port count designs

- 30Gbps backplane capability for general purpose data switching applications

- Up to 56Gbps chip-to-chip/chip-to-module performance for leading-edge interface standards

- Over 2.5Tbps serial memory bandwidth with Hybrid Memory Cube support

- Over 2.3Tbps parallel memory interface bandwidth with support for DDR4 at 2666Mbps

Reduce operating expenses (OpEX)

- Stratix 10 leverages Intel's leadership in process technology to deliver the most power efficient technology

- Up to 70% less power consumption than previous generation high-end FPGA & SoC

- Power efficiency up to 80 GFLOPs/W for single precision floating point arithmetic

- Quad-core ARM Cortex-A53 processor optimized for performance per watt

Highest level of system integration

- Industry's highest density monolithic FPGA device with 5.5M logic elements

- Heterogeneous 3D SiP solution integrating transceivers and other advanced components

- Power efficiency up to 80 GFLOPs/W for single precision floating point arithmetic

- 64-bit quad-core ARM Cortex-A53 enables hardware virtualization, system management and monitoring functions, acceleration and preprocessing, and more

Includes the most comprehensive high-performance FPGA security features

- Includes Secure Device Manager (SDM) for flexible configuration code updates

- 多要素認証

- PUF (Physically Unclonable Function)

Faster time to market

- Start development with Arria 10 devices and migrate to footprint-compatible Stratix 10 devices

- Complementary Enpirion PowerSoCs offer a complete and validated power solution that enables Stratix 10 FPGAs & SoCs to improve performance, reduce system power consumption, improve reliability, reduce footprint and speed time to market

High design productivity with optimized FPGA & SoC design software

- New Spectra-Q™ engine optimized for multi-million LE FPGA designs

- Compile time reduced by up to 8x

- デザインのイタレーションを大幅に削減

- Hyper-Aware design flow to optimize designs for HyperFlex architecture

- C-based design entry using the Altera SDK for OpenCL™, providing an FPGA-friendly design environment

- Heterogeneous C-based modeling and hardware design with Altera SDK for OpenCL

- Heterogeneous debug, profiling and whole-chip visualization with Altera SoC EDS with ARM Development Suite™ (DS-5™) Altera Edition Toolkit

- Stratix 10 FPGA & SOC Documentation: Stratix 10 FPGA & SOC Documentation

- White Paper: FPGA Breakthrough Advantages with Tri-Gate Technology (PDF)

- White Paper: What Breakthroughs Will Next-Generation FPGAs Bring? (PDF)

- White Paper: Altera Generation 10 Products Meet Performance and Power Requirements of the Zettabyte Era (PDF)

- White Paper: Meeting the Power/Performance Imperative of the Zettabyte Era with Generation 10 (English/PDF)