RTL 設計者にとって便利な機能を豊富に搭載した開発支援ツールで、RTL や仕様書の作成期間が短くなるだけでなく、デザインの視認性が高まるので、ブロックの再利用やチーム設計に最適です。

▶ 紹介動画

▶ 機能の紹介 ( HDL 生成 / HDL の可視化 / HDL コードの品質検証 / バージョン管理 )

▶ 関連情報

▶ セミナー/ワークショップ

▶ お問い合わせ

紹介動画

グラフィカルビュー変換 チュートリアル

HDL Designer は、HDL 言語設計に関する様々な便利機能が備わっています。その中でも、再利用時などに効率よくコードを理解するためのドキュメントの文書化に役立つグラフィカルビュー変換を紹介します。

DesignChecker 機能の実施

HDL Designer は HDL 言語設計に関する色々な便利な機能が備わっており、その中でも RTL 設計の均一化や設計品質向上に使えるリント・チェック・ツール DesignChecker を紹介します。

HDL Designer ~RTL Simulator 連携~

HDL Designer 上で RTL シミュレーターと連携させるフローを紹介します。

機能の紹介

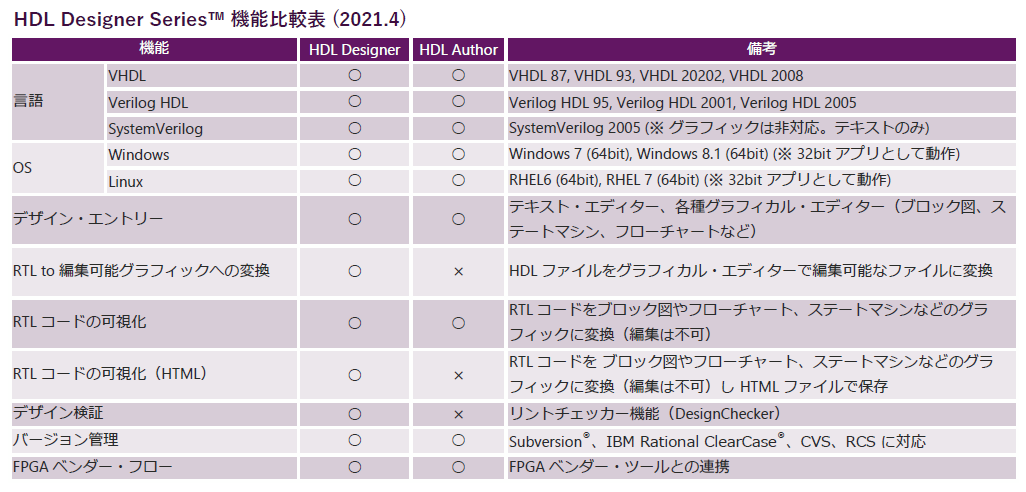

HDL Designer シリーズには、2種類のツールがあります。機能比較は、以下をご覧ください。

・ HDL Designer

・ HDL Author

関連情報

▶ Siemens EDA ツールのダウンロード方法

▶ HDL Designer のインストール方法

▶ Siemens EDA ツールのライセンス設定方法

セミナー/ワークショップ

HDL Designer で効率化! FPGA 設計の品質向上と設計資産活用

▶ Siemens EDA セミナー

お問い合わせ

メーカー情報 Top へ

メーカー情報 Top ページへ戻りたい方は、以下をクリックください。

シーメンス(Siemens)が所有する商標や登録商標:こちら