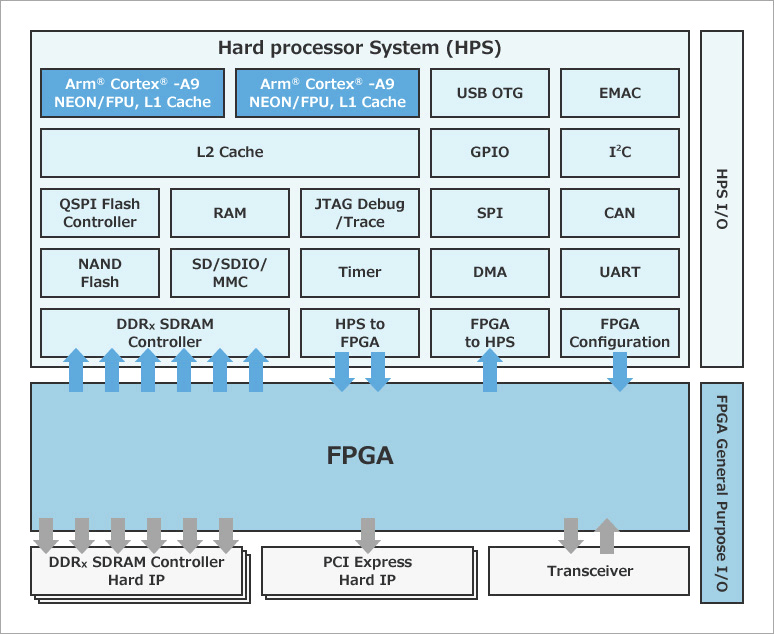

インテル® SoC FPGA は、Arm® Cortex® プロセッサーによるマイクロ・プロセッサー・ユニット(MPU)を搭載したハード・プロセッサー・システム(HPS)で、豊富なペリフェラル群、マルチポート・メモリー・コントローラー、および FPGA ファブリックで構成されるデバイスです。

このページでは、SoC FPGA を使用するユーザー向けに、最適な情報を紹介します。

1. SoC FPGA とは?

簡単に言うと、FPGA がペリフェラルの 1 つとしてメモリーマップされた Arm® プロセッサーです。SoC FPGA は、Arm® プロセッサー、ペリフェラル、およびメモリー・インターフェースで構成される HPS ファブリックと、FPGA ファブリックを 1 つのチップに統合した製品です。SoC FPGA により、素早い商品化、低消費電力、低コスト、設計リスクの低減、および基板の小型化を実現することができます。

2. SoC FPGA の開発に必要なツール

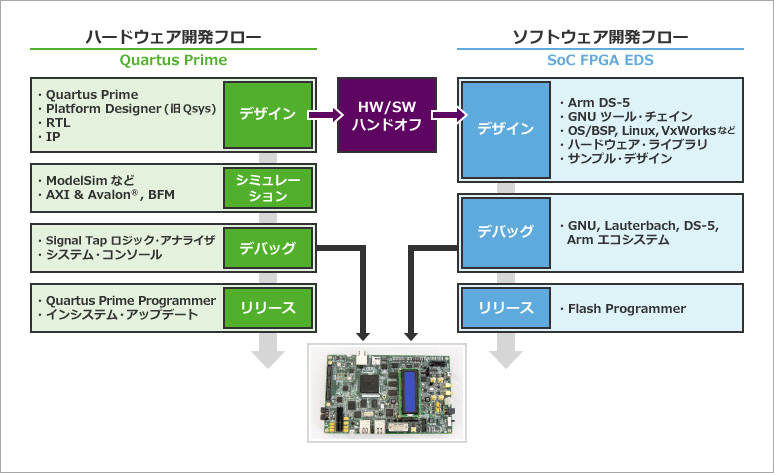

SoC FPGA の開発フローとしては、下図のように「FPGA ハードウェア開発フロー」と「ソフトウェア開発フロー」に分けられます。

2-1. FPGA ハードウェア開発フロー

開発環境であるインテル® Quartus® Prime 開発ソフトウェアやシステム構成ツールであるインテル® Platform Designer(旧 Qsys)システム統合ツール、ModelSim® シミュレーター、Signal Tap ロジック・アナライザーなどの FPGA 開発フローとデザインツールを利用することができます。

2-2. ソフトウェア開発フロー

インテル® SoC FPGA エンベデッド開発スイート(SoC EDS)は、インテル® SoC FPGA 用のエンベデッド・ソフトウェア開発のための包括的なツールスイートです。

また、インテル® SoC FPGA デバイスは、エンベデッド・ソフトウェア業界で広範にサポートされている Arm® プロセッサーを中心としています。インテル® とエコシステム・パートナーは、各開発ニーズに応じて幅広い選択肢を提供します。オペレーティング・システム(OS)については、オープンソースの Linux に加え、多数の商用 OS が利用できます。

ハードウェアからソフトウェアへの情報のハンドオフについては、SoC EDS に含まれるハードウェア-ソフトウェア・ハンドオフ・ユーティリティー を使用します。このユーティリティーは、Quartus® Prime および Platform Designer が生成する出力ファイルからソフトウェア・デザインフロー用のハンドオフファイルを生成します。これにより FPGA デザインチームとソフトウェア・デザインチームがそれぞれのデザインフローに従って、別々に作業を進めることが可能とになり生産性が向上します。

3. SoC FPGA のドキュメント公開サイト

3-1. インテル® の SoC FPGA 関連ページへのリンク集

|

名 称 |

概 要 |

| Intel® FPGA Support Resources (日本語ページ) |

インテル® のサポートリソース入口はこのページから |

| Intel® FPGAs & SoC FPGAs (日本語ページ) |

インテル® の FPGA デバイス別情報の入口はこのページから |

| Embedded Software and Tools for Intel® SoC FPGA (日本語ページ) |

Tools and Software のページです。 Quartus®、SoC EDS、DS-5 などの開発ツール情報はこのページから |

| SoC FPGA の Documentation ページ |

対象 SoC FPGA デバイス向けの各種ドキュメントが公開されています。

|

| Hard Processor System(HPS) Register Address Map |

対象 SoC FPGA デバイス向けのハード・プロセッサー・システム(HPS)レジスター・アドレスマップが公開されています。 |

| Intel® SoC EDS Support ページ (日本語ページ) |

Intel® SoC EDS のサポートページです。Documentation、Videos、Design Examples、Training Courses を公開しています |

| Intel® Community | Intel® Community は、Intel® FPGA、テクノロジー、ツール、およびそれらの使用法に関するコミュニティーの知識を提供することを目的とした Wiki サイトです |

| Intel® FPGA Knowledge Base (日本語ページ) |

Intel® FPGA 製品を使いこなすためのヒントや問題解決の方法などが公開されています |

3-2. Arm® 関連情報

Arm® 関連のリンクを下表に示します。Arm® 社のプロセッサーやペリフェラル、Arm® 純正のデバッガー(Arm DS / DS-5™)やコンパイラー(armcc)の詳細情報は以下のサイトをご参照ください。

|

名 称 |

概 要 |

| Arm® Developer(ドキュメント公開サイト) | Cortex®-A9、Cortex®-A53 他、Arm® 社の CPU/ペリフェラル/ツールのマニュアルはこちらを参照ください |

| APS(初心者講座) | Arm® 関連の技術情報サイトです。Cortex®-A 初心者講座 や 組み込み Linux 初心者講座 などがあります |

4. インテル® のコンテンツ

4-1. インテル® の SoC FPGA 関連デザインサンプル

● 以下のような SoC FPGA 向けの各種デザインサンプルが公開されています。

|

名 称 |

概 要 |

ファイル / Webページ |

対応ボード |

| SDMMC GSRD | Golden System Reference Design(GSRD)は、さまざまなカスタム・ユーザーデザインの開始点として使用できる重要なハードウェアおよびソフトウェア・システム・コンポーネントを提供します。 |

(最新はこちら) |

Arria® 10 SoC 開発キット |

| QSPI GSRD |

(最新はこちら) |

Arria® 10 SoC 開発キット | |

| SGMII GSRD |

(最新はこちら) |

Arria® 10 SoC 開発キット | |

| NAND GSRD | (最新はこちら) | Arria® 10 SoC 開発キット | |

| Remote Debug | この例では、System-Level Debugging(SLD)ツールを使用してリモートシステム・デバッグを実行する方法について説明します。 | Example Arria 10 | Arria® 10 SoC 開発キット |

| HPS-to-FPGA Bridges | FPGA ファブリックに接続されたハード・プロセッサー・システム(HPS)のメモリーマップされたインターフェースを実行します。HPS のさまざまなポートを使用して HPS メモリーをリード/ライトすることによってメモリーテストを実行し、データ転送のパフォーマンスを測定します。 | Example Readme Arria 10 Readme Cyclone V |

Arria® 10 SoC 開発キット Cyclone® V SoC 開発キット |

| PCIe Root Port | このリファレンス・デザインは、Arria® 10 SoC 開発キット上で動作する PCIe ルートポートを Cyclone® V GT FPGA 開発キットの PCIe エンドポイントまたは一般的に利用可能な Intel® PCIe Ethernet アダプターカードのエンドポイントに接続したものです。また、Cyclone® V SoC 開発キットおよび Arria® V SoC 開発キットにも適用できます。 | Example | Arria® 10 SoC 開発キット Arria® V SoC 開発キット Cyclone® V SoC 開発キット |

| Secure Boot | このドキュメントでは、インテル® Arria® 10 SoC FPGA Authentication Signing Utility ツールを使用して インテル® Arria® 10 SoC セキュアブート・システムを実装し、first-stage ブートローダー・イメージを保護する方法とデザイン例を示します。 | User Guide & Example | Arria® 10 SoC 開発キット |

| HPS DMA HWLIB | DMA API を使用して DMA を初期化し、メモリーからメモリーへの転送をおこなう方法を示しています。 | Example Arria 10 Readme Arria 10 |

Arria® 10 SoC 開発キット Arria® V SoC 開発キット Cyclone® V SoC 開発キット |

| Example Arria V Readme Arria V |

|||

| Example Cyclone V Readme Cyclone V |

|||

| ECC HWLIB | オンチップ RAM、SD/MMC、クワッドシリアル・ペリフェラル・インターフェース(SPI)、DMA および L2 キャッシュの Error Correction Code(ECC)API 機能をデモしています。この例では、各 RAM の ECC のセットアップと有効化、シングル/ダブルビット・エラーのインジェクション、シングル/ダブルビット・エラー検出のための割り込みのセットアップ方法を示しています。 | Arria® 10 SoC 開発キット Arria® V SoC 開発キット Cyclone® V SoC 開発キット |

|

| Example Arria V Readme Arria V |

|||

| Example Cyclone V Readme Cyclone V |

|||

| GPIO HWLIB | General-Purpose Input/Output(GPIO)API を使用して、HPS LED を駆動する出力ポートとして GPIO を設定し、HPS プッシュボタンの入力ポートとして GPIO を設定する方法を示しています。 | Example Arria 10 Readme Arria 10 |

Arria® 10 SoC 開発キット Arria® V SoC 開発キット Cyclone® V SoC 開発キット |

| Example Arria V Readme Arria V |

|||

| Example Cyclone V Readme Cyclone V |

|||

| I2C HWLIB | I2C API を使用してマスターとスレーブのリード/ライトを実行する方法を示します。この例では、LCD スクリーン、EEPROM メモリーとの I2C 通信、および 2 つの I2C モジュール間の通信をデモしています。 | Example Arria 10 Readme Arria 10 |

Arria® 10 SoC 開発キット Arria® V SoC 開発キット Cyclone® V SoC 開発キット |

| Example Arria V Readme Arria V |

|||

| Example Cyclone V Readme Cyclone V |

|||

| Quad SPI HWLIB | クワッド SPI API を使用して、一般的なブロック I/O 関数でクワッド SPI のリード/ライトを実行し、間接モードと DMA モードを使用してデータ・トランザクションを実行する方法を示しています。この例では、MMU やキャッシュの設定など、追加の API 機能も示しています。 | Example Arria V Readme Arria V |

Arria® V SoC 開発キット Cyclone® V SoC 開発キット |

| Example Cyclone V Readme Cyclone V |

|||

| SD/MMC HWLIB | SD/MMC カードの初期化、ブロック I/O 関数を用いたリード/ライトをおこなうための SD/MMC API の利用方法を示しています。 | Example Arria V Readme Arria V |

Arria® V SoC 開発キット Cyclone® V SoC 開発キット |

| Example Cyclone V Readme Cyclone V |

|||

| Timer HWLIB | フリーランニング・タイマー、ワンショット・タイマー、ウォッチドッグ・タイマー、およびグローバル・タイマー測定のための Timer API の使用方法を示しています。 | Example Arria 10 Readme Arria 10 |

Arria® 10 SoC 開発キット Arria® V SoC 開発キット Cyclone® V SoC 開発キット |

| Example Arria V Readme Arria V |

|||

| Example Cyclone V Readme Cyclone V |

|||

| Unhosted HWLIB | セミホスティングの代わりに UART を使って printf 出力をおこなう方法を示しています。また、SD カードからベアメタルプログラムを起動する方法も示しています。 | Example Arria V Readme Arria V |

Arria® V SoC 開発キット Cyclone® V SoC 開発キット |

| Example Cyclone V Readme Cyclone V |

|||

| SPI HWLIB | SPI API を使用して FPGA ファブリッ クを介して接続された 2 つの SPI モジュール間で通信する方法を示しています。 | Example Arria 10 Readme Arria 10 |

Arria® 10 SoC 開発キット Arria® V SoC 開発キット Cyclone® V SoC 開発キット |

| Example Arria V Readme Arria V |

|||

| Example Cyclone V Readme Cyclone V |

|||

| HPS Peripheral Mapping to FPGA | このデザイン例では、ハード・プロセッサー・システム(HPS)の EMAC および I2C ペリフェラルを FPGA ファブリックに配線し、FPGA I/O に接続する方法を示しています。 | Example Readme |

Cyclone® V SoC 開発キット |

| Power Optimization HWLIB | 消費電力を節約するために、呼び出し元のプロセッサー・コアをクロック・ゲーティング・モードにする WFI または WFE コールの使用を示しています。 | Example Readme |

Cyclone® V SoC 開発キット |

| Shared Memory Partition | このデザイン例では、ハード・プロセッサー・システム(HPS)SDRAM コントローラーのメモリー保護ルールの構成とテスト方法を説明します。 | Example Readme |

Cyclone® V SoC 開発キット Terasic Atlas SoC キット |

● インテル® の FPGA Design Store ページは、条件を設定して Design Examples を探せる新しいページです。

SoC FPGA 開発キット向けの各種デザインが公開されているリンク

・ Intel® Stratix® 10 SoC 向けデザイン

● Embedded Software Developer Center は、以下に挙げる特定の開発ロール向けにカスタマイズされた

各種資料やデザイン例が公開されているページです。

例えば、上記デバイス別のページからはなかなかたどり着けない HPS SoC Boot Guide などの資料のリンクも見つけられます。

特定の開発ロール向けにカスタマイズされた各種資料やデザイン例が公開されているページ

4-2. インテル® の SoC FPGA 関連ドキュメント

Intel® FPGAs & SoC FPGAs(日本語ページ)ページは、FPGA と SoC 製品に関する資料を探すための入り口です。

■ 入門資料

・ SoC FPGA 製品カタログ(日本語)

・ Design Considerations for SoC FPGAs Checklist(英語)

■ ユーザーガイド

■ ホワイトペーパー

4-3. 無料の SoC FPGA オンライン・トレーニング・コース

以下のページ では、インテル®が公開している SoC FPGA 関連の開発者トレーニングが表示されます。

5. その他のコンテンツ

5-1. RocketBoard.org コミュニティー・ポータルサイト

RocketBoards.org コミュニティー・ポータルサイト では、SoC FPGA 向けの Linux に関する各種情報を提供しています。

- 各種デザインサンプルは、RocketBoards.org の Projects ページ で公開されています。

- 各種ドキュメントは、RocketBoards.org の Documentation ページ で公開されています。

- インテル® およびパートナーが提供する開発キット(ボード)に関する情報は、RocketBoard.org の Boards のページ で公開されています。

例えば、マクニカ Mpression の Sodia ボードのページ では日本語リソースが公開されており、また各種のドキュメント、リファレンス・デザイン、デモなどが公開されています。

5-2. YouTube で公開しているビデオ

YouTube では各種の インテル® SoC FPGA 向けの各種動画 が公開されています。

6. SoC EDS に付属されているサンプル

SoC EDS には、SoC FPGA 開発キット向けのゴールデン・ハードウェア・リファレンス・デザイン(GHRD)、U-Boot、Linux、およびベアメタル・リファレンス・サンプルが付属しており、これらを使用した素早い開発が可能となっています。

SoC EDS v18.0 の examples/software フォルダーには、以下のような Linux および ベアメタルサンプルがあります。

|

名 称 |

概 要 |

備 考 |

| Altera-SoCFPGA-Blinking-LED-Linux-GNU | Linux 向け: LED 点滅サンプル | Linaro Linux GCC コンパイラー用 |

| Altera-SoCFPGA-HardwareLib-16550-CV-ARMCC | ベアメタル向け: Cyclone® V SoC + 16550 UART API 使用例 | Arm® コンパイラー用 |

| Altera-SoCFPGA-HardwareLib-16550-CV-GNU | ベアメタル向け: Cyclone® V SoC + 16550 UART API 使用例 | GCC コンパイラー用 |

| Altera-SoCFPGA-HardwareLib-ECCL2-CV-ARMCC | ベアメタル向け: Cyclone® V SoC L2キャッシュでのECC API使用例 | Arm® コンパイラー用 |

| Altera-SoCFPGA-HardwareLib-ECCL2-CV-GNU | ベアメタル向け: Cyclone® V SoC L2キャッシュでのECC API使用例 | GCC コンパイラー用 |

| Altera-SoCFPGA-HardwareLib-FPGA-CV-ARMCC | ベアメタル向け: Cyclone® V SoC FPGA Manager API使用例 | Arm® コンパイラー用 |

| Altera-SoCFPGA-HardwareLib-FPGA-CV-GNU | ベアメタル向け: Cyclone® V SoC FPGA Manager API使用例 | GCC コンパイラー用 |

| Altera-SoCFPGA-HardwareLib-SPI-CV-ARMCC | ベアメタル向け: Cyclone® V SoC SPI API を使用した EEPROM のリード/ライト・サンプル | Arm® コンパイラー用 |

| Altera-SoCFPGA-HardwareLib-SPI-CV-GNU | ベアメタル向け: Cyclone® V SoC SPI API を使用した EEPROM のリード/ライト・サンプル | GCC コンパイラー用 |

| Altera-SoCFPGA-HardwareLib-Timer-A10-ARMCC | ベアメタル向け: Arria® 10 SoC Timer API 使用例 | Arm® コンパイラー用 |

| Altera-SoCFPGA-HardwareLib-Timer-A10-GNU | ベアメタル向け: Arria® 10 SoC Timer API 使用例 | GCC コンパイラー用 |

| Altera-SoCFPGA-HardwareLib-Timer-AV-ARMCC | ベアメタル向け: Arria® V SoC Timer API 使用例 | Arm® コンパイラー用 |

| Altera-SoCFPGA-HardwareLib-Timer-AV-GNU | ベアメタル向け: Arria® V SoC Timer API 使用例 | GCC コンパイラー用 |

| Altera-SoCFPGA-HardwareLib-Timer-CV-ARMCC | ベアメタル向け: Cyclone® V SoC Timer API 使用例 | Arm® コンパイラー用 |

| Altera-SoCFPGA-HardwareLib-Timer-CV-GNU | ベアメタル向け: Cyclone® V SoC Timer API 使用例 | GCC コンパイラー用 |

| Altera-SoCFPGA-HelloWorld-Baremetal-ARMCC | ベアメタル向け: Hello World サンプル | Arm® コンパイラー用 |

| Altera-SoCFPGA-HelloWorld-Baremetal-GNU | ベアメタル向け: Hello World サンプル | GCC コンパイラー用 |

| Altera-SoCFPGA-HelloWorld-Linux-GNU | Linux 向け: Hello World サンプル | Linaro Linux GCC コンパイラー用 |

| Altera-SoCFPGA-Push-Button-Linux-GNU | Linux 向け: Push-Button サンプル | Linaro Linux GCC コンパイラー用 |

【注記】 Minimal Preloader(MPL)のベアメタルサンプル Altera-SoCFPGA-HardwareLib-MPL は、SoC EDS Standard Edition バージョン 18.0 には含まれていません。MPL を使用する場合は、Standard Edition バージョン 17.1 に付属のサンプルを使用する必要があります。詳細は、SoC EDS の Release Notes のページ を参照ください。

7. SoC FPGA のエコシステム(パートナーリンク)

SoC FPGA は Arm® プロセッサー・ベースであり、Arm® エコシステムの強みを継承しています。インテル® とエコシステム・パートナーは、各開発ニーズに応じて幅広い選択肢を提供します。

詳細は、Intel® SoC FPGAs Ecosystem(日本語ページ)をご参照ください。

7-1. SoC FPGA のオペレーティング・システム

SoC FPGA デバイスは、オープンソースの Linux に加え、多数の商用オペレーティング・システムが利用できます。以下に商用オペレーティング・システムのパートナーリンクを紹介します。

|

オペレーティング・システム(OS) |

会社名 |

| Abassi | Code Time Technologies |

| Bare-Metal/Hardware Libraries(インテル® SoC EDS 内) | インテル® |

| Carrier Grade Edition 7(CGE7) | MontaVista |

| DEOS | DDC-I |

| eCosPro | eCosCentric |

| eT-Kernel | イーソル株式会社 |

| FreeRTOS | FreeRTOS.org |

| INTEGRITY RTOS | Green Hills Software(日本代理店: アドバンスド・データ・コントロールズより提供) |

| Nucleus | Siemens |

| QNX Neutrino RTOS | QNX |

| RTXC | Quadros Systems Inc. |

| ThreadX | Microsoft |

| µC/OS-II、µC/OS-III | Micrium(日本代理店: テクノ・ロジックより提供) |

| µC3 | イー・フォース株式会社 |

| VxWorks | Wind River |

| Wind River Linux | Wind River |

7-2. SoC FPGA 向け開発ツール

JTAG デバッガーとインストラクション・トレース機能を含む専門性の高い開発ツールについては、以下をご検討ください。

|

製 品 |

供給ベンダー |

詳 細 |

| Arm® Development Studio for Intel® SoC FPGA | インテル® | Arm® Development Studio をベースにしたインテル® SoC FPGA デバイス向けソフトウェア開発およびデバッグツール。JTAG のデバッグおよび高速命令トレースのために FPGA ダウンロード・ケーブル II JTAG デバッガーツールまたは Arm® DSTREAM ツールとともに使用します。 |

| Multi | Green Hills | Green Hills INTEGRITY リアルタイム・オペレーティング・システム向けのソフトウェア開発およびデバッグツール。MULTI は JTAG デバック向けで Green Hills Probe で接続されます。 |

| Poly-Platform、 uC/OS-II |

PolyCore Software、 Micrium(日本代理店: テクノ・ロジックより提供) |

PolyCore ソフトウェアと Micrium は、マルチコアソリューションで Cyclone® V SoC をサポートします。この開発環境は、実績のあるメッセージの受け渡しプログラミング・モデルおよびトラステッド・リアルタイム・オペレーティング・システム(RTOS)を提供し、新しいマルチコアデザインの作成を容易にします。 |

| Simulink Embedded Coder | MathWorks | MathWorks の Simulink と Embedded Coder を使用して、Cyclone® V SoC 用の C/C++ コードを生成します。このソリューションは、HDL Coder によるインテル® SoC FPGA サポートと併用することで、シミュレーション、プロトタイプ作成、検証、および実装にまたがるインテル® SoC FPGA のハードウェア / ソフトウェア・ワークフローに利用できます。 |

| Sourcery CodeBench | Siemens | GNU ツールチェーンは、デュアルコア Arm® Cortex®-A9 MPCore プロセッサー・ベースの SoC バーチャル・ターゲットをサポート。 |

| TRACE32 | Lauterbach | Lauterbach TRACE32 は、Nios® II プロセッサーとデュアルコア Arm® Cortex®-A9 MPCore プロセッサー・ベースの SoC をサポートするデバッグ、トレース、および命令セット・シミュレーターを含むモジュラータイプのプロセッサー開発ツールのファミリーです。 |

| Workbench | Wind River | Cyclone® V SoC および Arria® V SoC のデュアルコア Arm® Cortex®-A9 MPCore プロセッサーで動作する VxWorks 用のソフトウェア開発ツール。 |

7-3. SoC FPGA IP コア

インテル® SoC FPGA は、さまざまなサードパーティーおよびソフト知的財産(IP)コアでサポートされています。こうした IP ブロックは、SoC デバイス上の FPGA でのインスタンス化が可能です。

主要な SoC ソフト IP コアの例は次のとおりです。

|

IP |

供給ベンダー |

詳 細 |

| グラフィックス・レンダリング | TES Electronic Solutions | 2D、2.5D、3D および HD グラフィックス・レンダリング(EGL 1.3、OpenGL ES 1.1、OpenVG 1.01 API までをサポート) |