こんにちは。

マクニカでインテル® FPGA 製品の技術サポートをしている インテル・F・ハナコ です。

インテル FPGA 向けのデザインを RTL レベル・シミュレーションするには、ModelSim® – Intel® FPGA Edition のようなサードパーティー・ツール (EDA ツール) を使用します。

デザインに、Quartus® Prime で作成した IP が組み込まれている場合は、その IP 用のシミュレーション・モデルを生成し、モデルに対応したシミュレーション・ライブラリをセットアップする必要があります。

つまりユーザーは、以下の3点を知っていなければなりません。

✔ 使用する IP 向けのシミュレーション・モデルはどのファイルか

✔ シミュレーション・モデルに対応させるシミュレーション・ライブラリはどれか

✔ EDA ツールでそのライブラリをどう使うのか

これらの取り扱いを簡単にした方法を、下記コンテンツでご紹介しています。

|

Quartus Prime Standard Edition Quartus Prime Lite Edition |

Quartus Prime Pro Edition |

| FPGA のファンクション・シミュレーションは NativeLink で解決しよう |

これらの方法は、デザインに使用されているすべての IP に向けたシミュレーション用スクリプトファイル msim_setup.tcl の内容を、自動で統合してくれる機能で、オススメの方法なのです!

(しかも、NativeLink は、IP 以外のユーザーデザインおよびテストベンチ・ファイルも一緒にスクリプト化してくれます。)

上記のコンテンツ情報で、すべての作業はカバーできますが、

今回は、この msim_setup.tcl を手動で編集する方法と、編集後のスクリプトファイルを ModelSim で実行する方法をご紹介します。

(やや面倒な作業ですので、上級者向けの内容です。ご注意ください。)

対象環境

| Quartus Prime |

Quartus Prime Pro Edition Quartus Prime Standard Edition Quartus Prime Lite Edition |

| シミュレーション・ツール(注1) |

ModelSim PE / ModelSim SE / Questa ModelSim - Intel FPGA Edition (Starter Edition を含む) |

注1: 各ツールの対応バージョンは、ご利用になるバージョンの Quartus Prime のリリースノートをご確認ください。

注2: スケマティックのデザイン (.bdf) は、すべて HDL に変換する必要があります。

<参考 FAQ> Q: 回路図を含んだデザインを ModelSim でシミュレーションしたいのですが、うまくいきません。

msim_setup.tcl とシミュレーション・モデルを生成

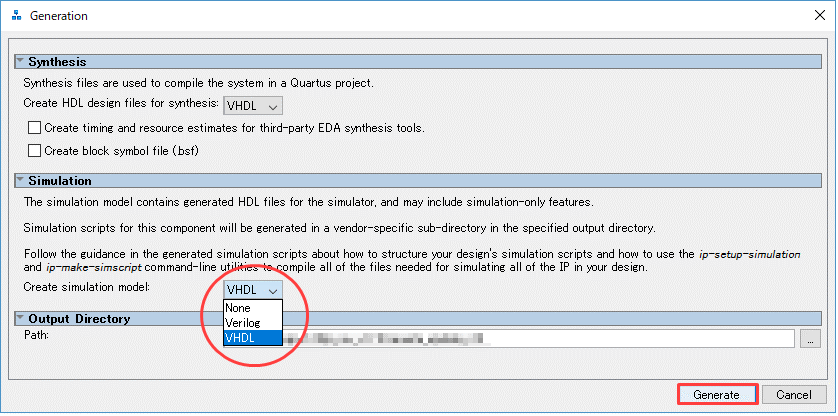

デザイン内に Platform Designer、あるいは IP Catalog で作成したモジュールが "Platform Designer GUI ベースで起動されるもの" の場合には、Generate 時に "シミュレーション・モデル生成オプション" があるので、言語を選択してから Generate を実行してください。(選択していないと、シミュレーション・モデルや msim_seutp.tcl ファイルが生成されず、シミュレーションが実行できません。)

IP Catalog において Wizard 形式で作成する IP の場合には、自動でシミュレーション・モデルと msim_setup.tcl ファイルが生成されます。

また、IP Catalog で作成する IP によっては、シミュレーション・モデルを専用に生成しないものもあります (例えば、ALTLVDS_RX/TX、ALTPLL、RAM: 2-PORTなど)。その場合は、msim_setup.tcl も生成されません。よって、スクリプトは自作してください。

msim_setup.tcl の基本構成

msim_setup.tcl ファイルは、モジュール Generate 実行後に以下のフォルダーに生成されます。(例外あり)

| IP Catalog で作成した IP モジュール | <ip_name>_sim フォルダー ➤ mentor フォルダー内 |

| Platform Designer で作成したモジュール | <ip_name> フォルダー ➤ simulation フォルダー ➤ mentor フォルダー内 |

TCL スクリプトは 「#」 マークで開始される行をコメントアウトと見なします。

msim_setup.tcl ファイルの各セクションの冒頭には、実行する内容の要約が # によってコメントアウトで記述されています。

ここでは、コメントアウトされている要件部分の内容 (代表的な基本構成) を見ていきましょう。

|

要件(コメント部分) |

概要 |

|

# Initialize variables # Initialize simulation properties - DO NOT MODIFY! |

変数の設定 (Quartus Prime のインストール・フォルダーのパス指定、IP 生成フォルダー・パスなど) が記載されています。 |

| # Copy ROM/RAM files to simulation directory | 必要なメモリ初期化ファイルをシミュレーション・フォルダーにコピーする指示が記載されています。 |

|

# Create compilation libraries # Compile device library files |

シミュレーションに必要な各種ライブラリの作成およびコンパイルを実行する指示が記載されています。 |

| # Compile the design files in correct order | IP のコンパイルを実行する指示が記載されています。 |

|

# Elaborate top level design # Elaborate the top level design with novopt option |

デザインをロードする指示が記載されています。 ※ "デザインのロード実行" を、"シミュレーション実行" と言う人もいます。 ※ ModelSim – Intel FPGA Edition ユーザーは、"# Elaborate the top level design with novopt option" を使用してください。 |

|

# Compile all the design files and elaborate the top level design # Compile all the design files and elaborate the top level design with –novopt |

必要なすべてのデザインファイルをコンパイル、およびシミュレーションの実行が一括で行える指示が記載されています。 ※ ModelSim – Intel FPGA Edition ユーザーは、"# Compile all the design files and elaborate the top level design with –novopt" を使用してください。 |

※ これは一例です。すべての msim_setup.tcl が同じ構成ではありません。

msim_setup_edit.tcl を作成および編集

msim_setup.tcl は IP 専用に自動生成されたスクリプトなので、IP 自身がトップ・モジュールとして指定されており、ユーザーが作成したデザインファイルやテストベンチを適用させる場合は、情報が不足しています。

msim_setup.tcl を編集し、プロジェクト・デザインに適用させます。

[Note]

msim_setup.tcl は、生成されたフォルダー位置のまま使用することを推奨しています。

もし別フォルダーへ移動して使用する場合には、デフォルトで記載されたライブラリや IP ファイルなどのパス環境が崩れるため、

変数の設定を修正して、使用するファイルパス環境に対応させて利用してください。

また、IP を複数使用している場合は、msim_seup.tcl も複数存在します。すべての msim_setup.tcl の必要箇所を手動でマージしてください。

1) msim_setup.tcl を複製し、リネーム

編集用に msim_setup.tcl を複製し、ファイル名を変更してください。

ここでは、msim_setup_edit.tcl とします。

2) ユーザーのデザインおよびテストベンチを追加

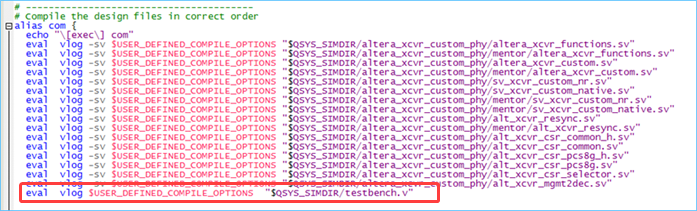

① msim_setuip_edit.tcl を開き、"alias com" の箇所を検索します。

(ここは、ModelSim がデザインファイルをコンパイルする指示が書かれた箇所です。)

② ユーザーのデザインファイルおよびテストベンチをコンパイルする以下の実行コマンドを追記します。

コンパイル実行コマンドはそれぞれ、VHDL は vcom、Verilog HDL は vlog です。

<コマンドの基本構成>

[VHDL] eval vcom $USER_DEFINED_COMPILE_OPTIONS "ファイルのパス"

[Verilog] eval vlog $USER_DEFINED_COMPILE_OPTIONS "ファイルのパス"

ファイルのパスは、絶対パス、相対パス、いずれでも可能です。

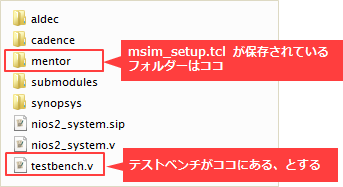

例えば、Verilog HDL テストベンチ (testbench.v) の保存フォルダーが、下図の構成 (msim_setup.tcl の一つ上のフォルダー) である場合

eval vlog $USER_DEFINED_COMPILE_OPTIONS "./../testbench.v"こちら (↓) でも OK。

eval vlog $USER_DEFINED_COMPILE_OPTIONS "$QSYS_SIMDIR/testbench.v"[Note]

msim_setup_edit.tcl 内で、変数 "QSYS_SIMDIR" は set QSYS_SIMDIR "./../" と設定されています。

このようになります。

同様に、シミュレーションに必要なユーザーデザイン用のコンパイル・コマンドを追記します。

編集中の msim_setup_edit.tcl で使用されている IP 以外の IP 情報を追記する場合は、転写元の IP 用 msim_setup.tcl の下記コメント部分の

実行内容をコピーし、転写先の msim_setup_edit.tcl の各所へペーストして、スクリプトをマージしてください。

以下は、コピー & ペーストする参考箇所です。

# Copy ROM/RAM files to simulation directory

# Create compilation libraries

# Compile device library files

# Compile the design files in correct order

3) デザインのロードを実行する対象デザインを、テストベンチに変更

msim_setup_edit.tcl は、デフォルトで IP や Platform Designer で作成したモジュールがトップ・デザイン扱いになっています。

そのため、テストベンチを最上位モジュールにします。

変更方法は、以下2通りあります。どちらかで対応してください。

<方法1: vsim コマンド部分を直接編集>

① "vsim" コマンドを検索します。(ここは、デザインのロードを実行する指示が書かれた箇所です。)

② vsim コマンド部分の末尾に記載されている変数 "$TOP_LEVEL_NAME" を "work.テストベンチ名" に変更します。

例えば

変更前

eval vsim -novopt -t ps <途中省略> $TOP_LEVEL_NAME変更後

eval vsim -novopt -t ps <途中省略> work.testbenchこのようになります。

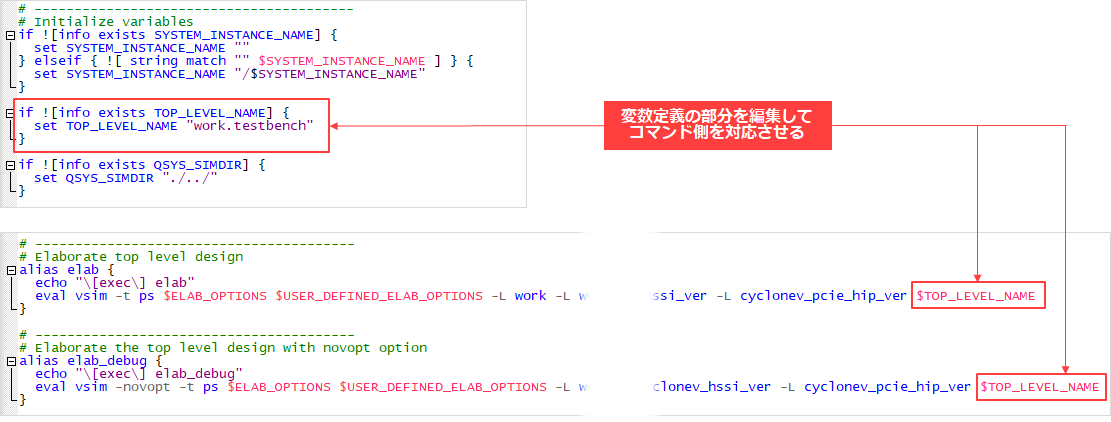

<方法2: 変数 "$TOP_LEVEL_NAME" の宣言部分を編集>

① "set TOP_LEVEL_NAME" を検索します。(# Initialize variables セクションの方です。)

② ダブルクォーテーションのモジュール名を、テストベンチのモジュール名に変更します。

例えば

set TOP_LEVEL_NAME "work.testbench"このようになります。

4) msin_setup_edit.tcl を上書き保存し、編集内容を反映

[Note]

IP や Platform Designer のデザインを変更し再生成(Re-generate)した場合、各 msim_setup.tcl は上書き更新されます。

そのため、msim_setup_edit.tcl は更新された内容に都度編集してください。

msim_setup_edit.tcl の編集作業は以上です。

編集後の msim_setup_edit.tcl を ModelSim で実行

編集した msim_setup_edit.tcl を ModelSim で実行します。

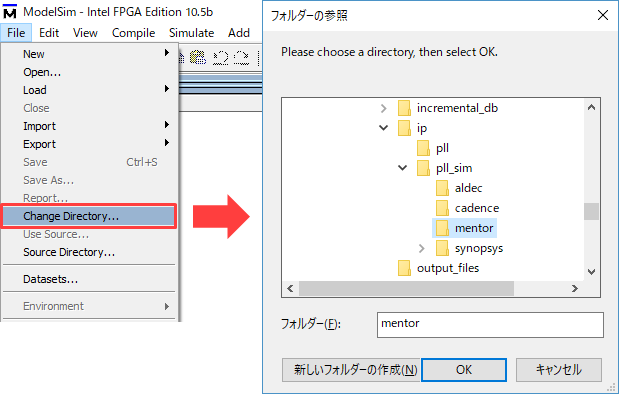

① ModelSim を起動し、File メニュー ➤ Change Directory (あるいは cd コマンド) により、

編集後の msim_setup_edit.tcl が保存されたフォルダーへ移動します。

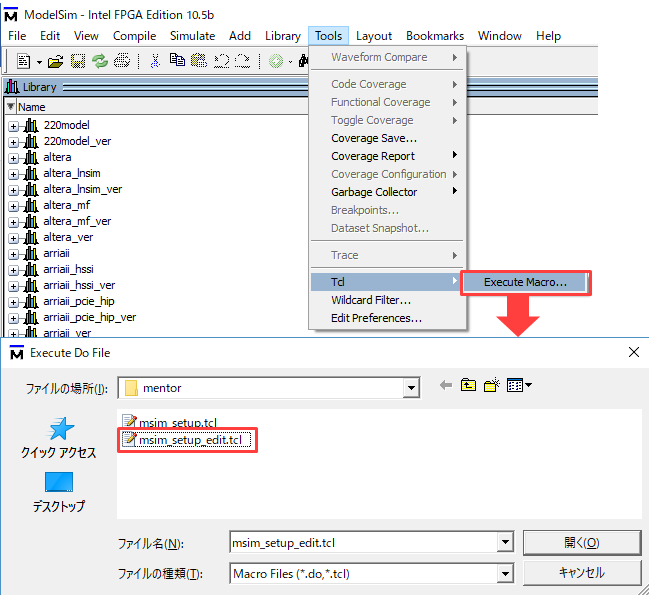

② Tools メニュー ➤ Tcl > Execute Macro… (あるいは do コマンド) により、スクリプトファイルを選択して実行します。

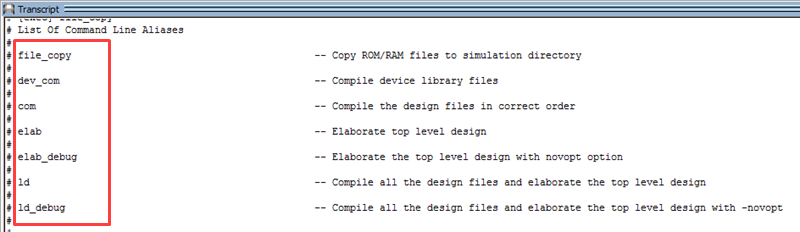

③ スクリプトが読み込まれ、Transcript ウィンドウにコマンドラインのエイリアスが表示されます。

④ 実行するエイリアスを Transcript ウィンドウに入力します。

例えば、ライブラリやデザインファイルのコンパイル、デザインのロードを一気に実行したい場合は

"ld" または "ld_debug" を入力します。

[Note]

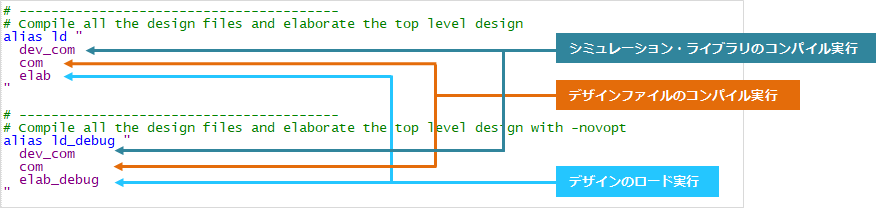

ld や ld_debug は、msim_setup_edit.tcl に alias xxx "…" で定義されている実行内容がすべて実行されます。

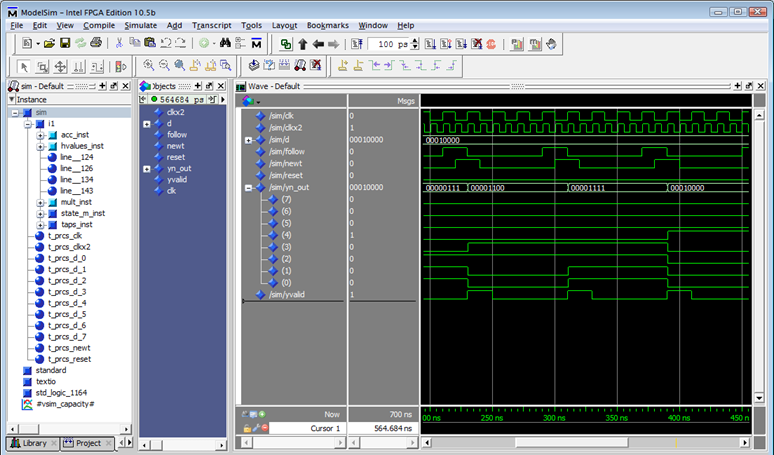

⑤ ld または ld_debug によりデザインのロードまで完了したら、観測する信号を Wave ウィンドウに追加し、通常通りシミュレーションを開始します。

Wave ウィンドウに表示された波形を検証してください。

ハナコ’s ポイント♪

ld あるいは ld_debug エイリアス実行後、波形を Wave ウィンドウへ追加(登録)し、シミュレーションを実行する操作も

コマンド化してしまいましょう!

すると、シミュレーションの一連の作業がスクリプトで一気に実行されて、非常に便利です。

① 新規にスクリプトファイルを作成します。ここでは、sim_all.do とし、msim_setup_edit.tcl と同じフォルダーに保存します。

② テキストエディタで開き、以下の内容を記述します。

・ msim_setup.tcl の実行コマンド (do コマンド)

・ ld あるいは ld_debug エアリアスを実行

・ テストベンチのポートを Wave ウィンドウへ追加するコマンド (add wave)

・ シミュレーション実行コマンド (run コマンド)

例えば、このようになります

do E:/fpga_design/ip/pll_sim/mentor/msim_setup_edit.tcl

ld_debug

add wave *

run 500ms③ ModelSim を起動し、File メニュー ➤ Change Directory により、sim_all.do があるフォルダーへ移動します。

④ Tools メニュー ➤ Tcl > Execute Macro… より、sim_all.do を選択して実行します。

⑤ 上記②の作業がすべて実行されます。Wave ウィンドウに表示された波形を検証してください。

今回はわかりやすく msim_setup.tcl が保存されているフォルダーに msim_setup_edit.tcl や sim_all.do を保存しましたが、シミュレーション・ライブラリやシミュレーション・モデル、デザインファイルなどのパスに整合性が取れれば、スクリプトファイルはどこに保存してもかまいません。

オリジナルのスクリプトを作成して、より効率良くシミュレーションを実施してください。

スクリプトファイルの説明

msim_setup.tcl で使用されているコマンドを一部紹介します。

|

コマンド |

概要および例 |

| vlib | ライブラリを作成する 例: vlib rtl_work |

| vmap |

論理ライブラリ名とファイルシステム上のライブラリのパスをマッピングする 例: vmap work rtl_work |

| vlog |

Verilog および SystemVerilog ファイルをライブラリにコンパイルする 例: vlog -work work ./sample.v |

| vcom |

VHDL ファイルをライブラリにコンパイルする 例: vcom -work work ./sample.vhd |

| vsim |

デザインをロードする 例: vsim work.sample_tb |

| add wave |

選択した信号を Wave ウィンドウへ追加する 例: add wave * |

| view |

指定のウィンドウを表示する 例: view structure |

| run |

シミュレーションを実行する 例: run 500ms |

生成されたスクリプトファイルのコマンドを追加あるいは編集して使用することも可能です。コメントアウトは、行の先頭に # をつけてください。

コマンド、およびコマンドのオプションの詳細は、ModelSim、Questa の 「Command Reference Manual」 を参照してください。

おすすめ記事/資料はこちら

ModelSim® 向けシミュレーション用スクリプトファイルを生成・実行してみよう

FPGA のファンクション・シミュレーションは NativeLink で解決しよう

Quartus® Prime Pro Edition で生成した IP を含むデザインを ModelSim でファンクション・シミュレーションする方法

ModelSim® - Intel® FPGA Edition - RTL シミュレーションの方法