旧タイトル『DS-5 活用テクニック~Flash Programming Alternative』のアップデート版です。

インテル® SoC FPGA 向けのソフトウェア統合開発環境として標準採用される Arm 純正ツールが Arm® DS-5 for Intel® SoC FPGA Edition (DS-5) から Arm® Development Studio for Intel® SoC FPGA Edition (Arm® DS) へと変更になりました。Arm® DS は DS-5 の後継製品となっており使い勝手は大きくは変わりません。このシリーズ記事の内容も Arm® DS / DS-5 両方に適用できるものが大半ですが、違いがある箇所はその旨明記する形でアップデートしています。

***

この記事では、インテル® SoC FPGA 向けのソフトウェア統合開発環境として利用可能な Arm® DS / DS-5 の使い方に関する補足情報を記載します。

今回は、RocketBoards.org に掲載される HPS ブート用 Flash への書き込み方法『 Arria 10 Flash Programming Alternative 』 を紹介します。

※注意:Rocketboards.org に掲載されるスクリプトは DS-5 を対象としたものになっています。Arm® DS で動作させるためには一部変更が必要です。

この記事には、参考として Arm® DS 向け改造版のスクリプトを添付しています。書き込みが行えることの確認は行っていますが動作を保証するものではありませんので、あくまで参考としてお客様の自己責任のもとご使用ください。(スクリプトの先頭に再配布および使用の条件も記載されています)

はじめに

この記事で紹介する方法では Arm® DS / DS-5 デバッガの直接的な操作は行いません。Python スクリプトを介して Arm® DS / DS-5 を動作させる仕組みとなっているため、デバッガの操作に不慣れなユーザーが Arm® DS / DS-5 を使用した Flash 書き込みを行うケースに最適な方法となっています。

また、Flash への書き込みには U-Boot に実装されているコマンド機能を利用します。U-Boot のコマンド機能には、HPS Flash Programmer (SoC EDS 付属の Flash 書き込みツール) と比べて「より高速な書き込みが可能」および「サポートしている Flash デバイスが充実している」という利点があるのですが、これらもまた、この方法を使用するメリットとなります。

U-Boot を使用した Flash 書き込みについては以下の記事も参照ください。

HPS Flash Programmer より高速!U-Boot で QSPI に書き込む方法

オリジナルページ(RocketBoards.org)

・ オリジナルページのURL:

https://rocketboards.org/foswiki/Documentation/Arria10NANDFlashProgramming

※詳細情報はオリジナルのページ(英文)をご確認ください。

オリジナルの記事は旧バージョンのツール環境を対象としています。

最新の開発ツール環境で使用される場合には、Rocketboards.org『 SoCEDS and ARM Development Studio 』を参照して下記項目を実施ください。

- Installation

- Running the Tools

- SoC EDS Licensing

※注意:Windows の場合は、別途Cygwinのインストールが必要になります。Cygwinのセットアップ手順も上記ページに記載されておりますが、記載の手順では Flash Programming 用スクリプトの実行に必要な python2 がインストールされません。

こちらで確認を行った際には、旧バージョン(v18.1)の SoC EDS に付属の Cygwin 環境と比較した上で、次のパッケージを追加インストールして対応しています。『python2,bcrypt,ccrypt,libprocps8,tcsh』

事前準備1:スクリプトのダウンロードなど

スクリプトを含むアーカイブ(flash_programmer.tgz)をダウンロード

オリジナルページに公開されているスクリプト「 flash_programmer.tgz 」をダウンロードします。

PC 上にファイルを展開

●「 flash_programmer.tgz 」を SoC EDS がインストールされたホスト PC 上に展開します。

1. Embedded Command Shell を起動。

2. Shell 上で TAR 展開コマンドを実行。

$ tar -xzvf ./flash_programmer.tgz

3. 展開先のディレクトリーへ移動します。

$ cd flash_programmer

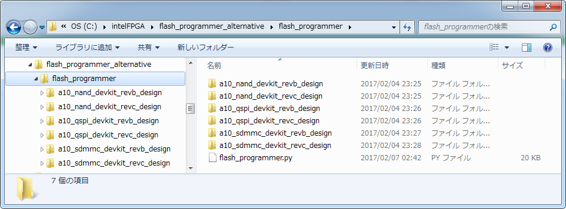

●展開後のディレクトリー以下は、下記のような構成になっています。

●flash_programmer.py が Flash 書き込み用のメインスクリプトです。

●その他は、Arria® 10 SoC Development Kit 向けのデザインファイルが、ブートソース(NAND / QSPI / SDMMC)、ボードリビジョン(Rev.B / Rev.C)毎に用意されています。

●各デザインには、以下の 3 つのファイルが含まれます。

‐ \output_files\ghrd_10as066n2.sof … FPGA コンフィグレーションデータ(.sof)

‐ \software\bootloader_extcfg_semihosting\devicetree.dtb … U-Boot 用デバイスツリーバイナリー(.dtb)

‐ \software\bootloader_extcfg_semihosting\uboot-socfpga\u-boot … U-Boot 本体(実行ファイル)

※ 標準で用意されているデザインファイルは Arria® 10 SoC Development Kit 向けのみとなっていますが、同じ構成のデザインファイルを用意することで各種ターゲットボードに同じ仕組みを適用することが可能になっています。

※ オリジナルページの情報によるとサポート対象のデバイスは Arria® 10 SoC のみとなっています。ただし、スクリプトの内容を確認する限りでは、Arria® 10 SoC 以外にも、Arria® V SoC、Cyclone® V SoC に対応するための記述が一部用意されている状態となっていますので、スクリプトの内容に手を加えることで Arria® V SoC、Cyclone® V SoC に対応できる可能性はありそうです。ご使用の際には flash_programmer.py の内容および動作を確認した上でご判断ください。

※ Arm® DS の場合は、この記事に添付されている flash_programmer_armds.zip をダウンロードおよび解凍した上で、flash_programmer.py と差し替えてご使用ください。

事前準備2:オリジナルターゲット向けデザインファイルの用意(任意)

デザイン・ディレクトリーの用意(ネーミングルール)

●flash_programmer 直下にオリジナルターゲット向けデザインファイルを格納するためのデザイン・ディレクトリーを用意します。

○ ネーミングルール: <device>_<bootsource>_<board_name>_design

‐ <device> = {a10 / av / cv}から選択

‐ <bootsource> = {qspi / sdmmc / nand}から選択

‐ <board_name> = ボード識別用に判り易い名前を指定

※ 例(Arria® 10, QSPIブート, ボード名:testboard01):a10_qspi_testboard01_design

デザインファイルの作成および格納

●作成したデザイン・ディレクトリーに、以下の3つのファイルを格納します。

‐ \output_files\ghrd_10as066n2.sof … FPGA コンフィグレーションデータ(.sof)

‐ \software\bootloader_extcfg_semihosting\devicetree.dtb … U-Boot 用デバイスツリー・バイナリー(.dtb)

‐ \software\bootloader_extcfg_semihosting\uboot-socfpga\u-boot … U-Boot 本体(実行ファイル)

※ FPGA コンフィグレーション・データ(.sof)は、オリジナルターゲット向けの Quartus® プロジェクトで生成されるファイルをそのまま使用します。

※ U-Boot 本体およびデバイスツリーには、以下のオプション指定が必要となるので、本番用とは別に作成する必要があります。

‐ External Configulation 有効 ( bsp-editor 上で external_fpga_config のチェックを ON )

‐ SemiHosting 有効 ( U-Boot ソースツリー以下の定義を編集 )

【編集前】 #undef CONFIG_SEMIHOSTING

【編集後】 #define CONFIG_SEMIHOSTING

Flash Programming 実行

ターゲットボードとの接続

ターゲットボードとホスト PC を、USB-Blaster (JTAG) ケーブルで接続。(接続はこの1本のみでOK)

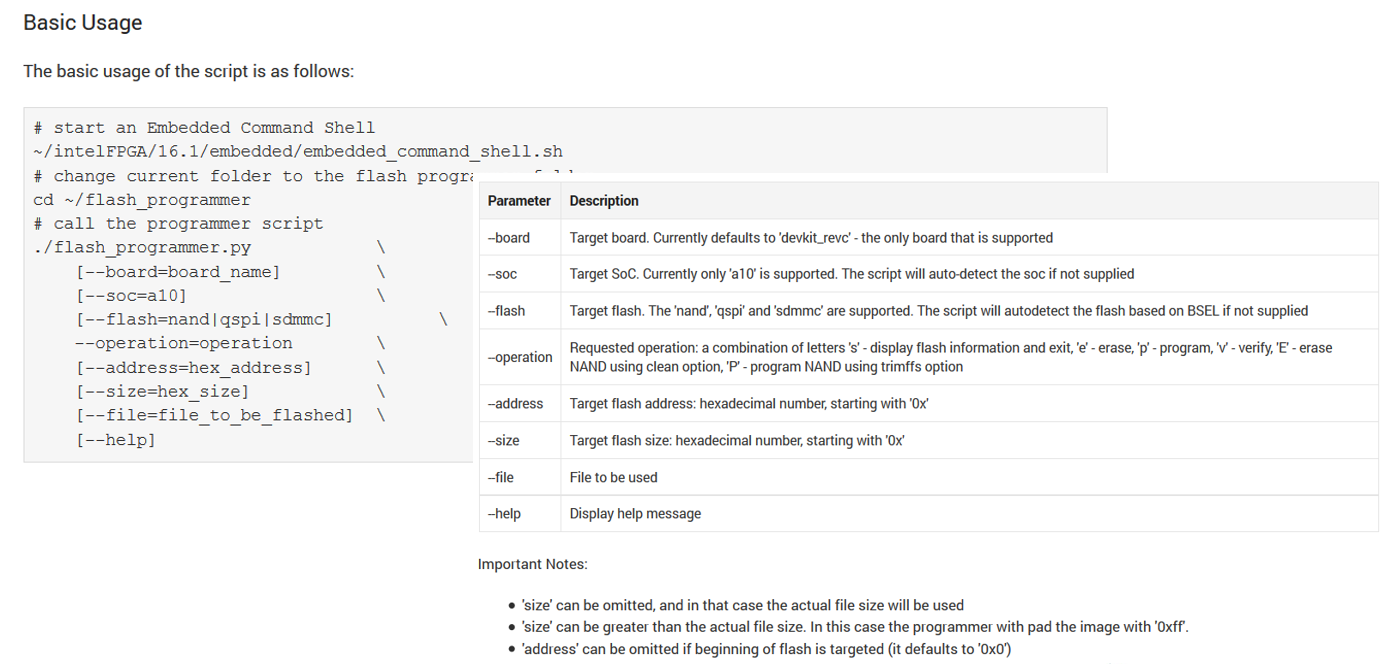

プログラミング実行

あとは、ターゲットボードの電源投入後、Embedded Command Shell 上で flash_programmer.py を実行するのみです。

1. Embedded Command Shell を起動。

2. スクリプト展開先のディレクトリーへ移動します。

‐ $ cd flash_programmer

3. スクリプト実行(例:Arria® 10, QSPI, ボード名:testboard01 )

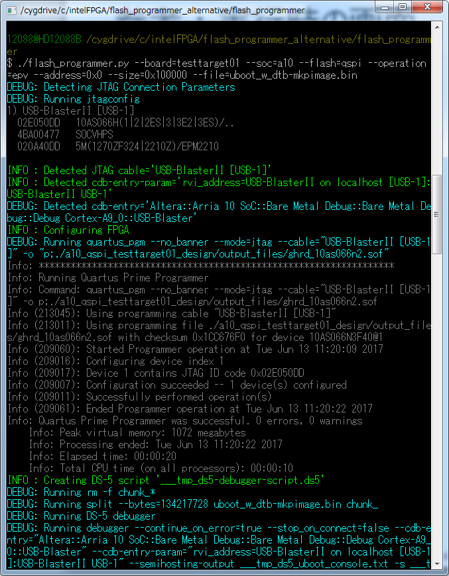

‐ $ ./flash_programmer.py --board=testtarget01 --soc=a10 --flash=qspi --operation=epv --address=0x0 --size=0x100000 --file=uboot_w_dtb-mkpimage.bin

※ flash_programmer.py のオプション詳細は RocketBoards.org の説明を参照ください。

(この記事では扱っていない、TFTP を用いた高速化手順も掲載されています。)

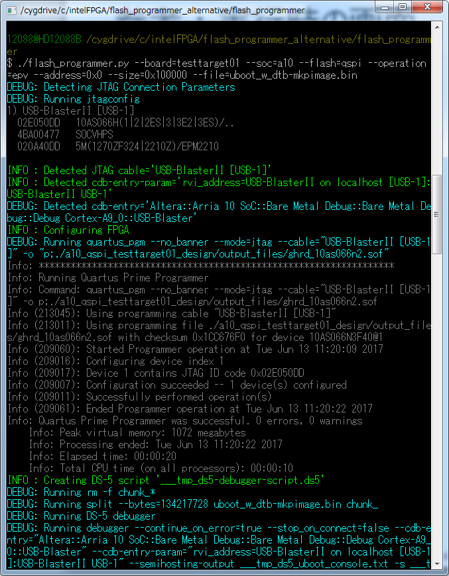

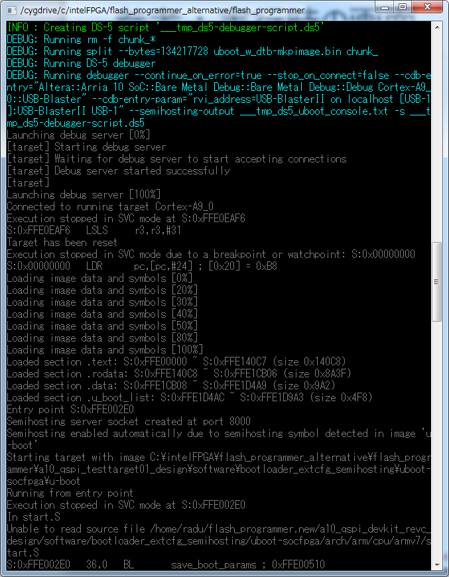

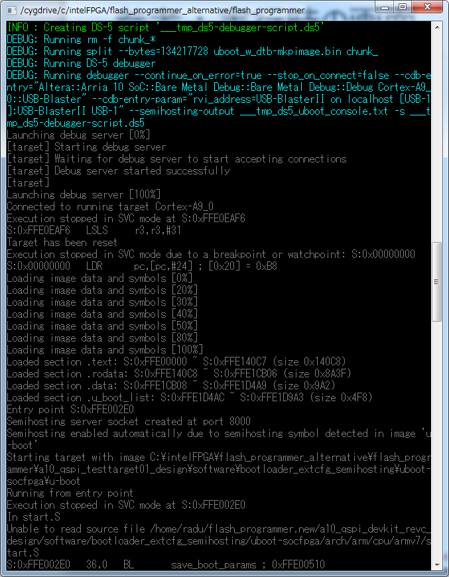

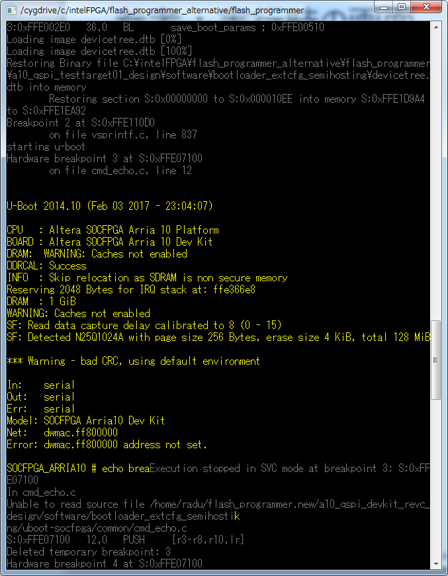

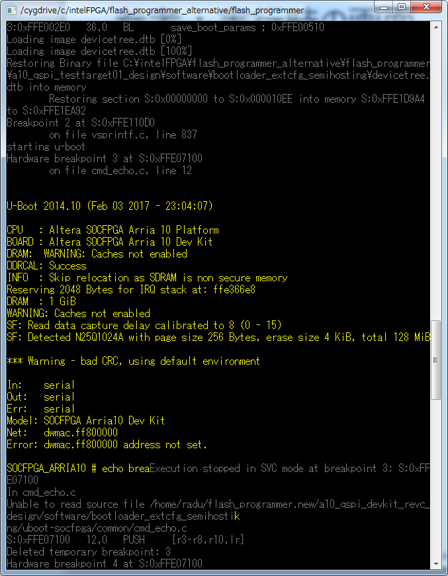

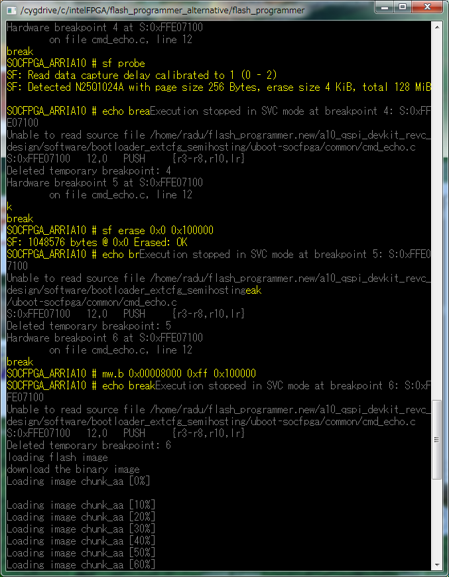

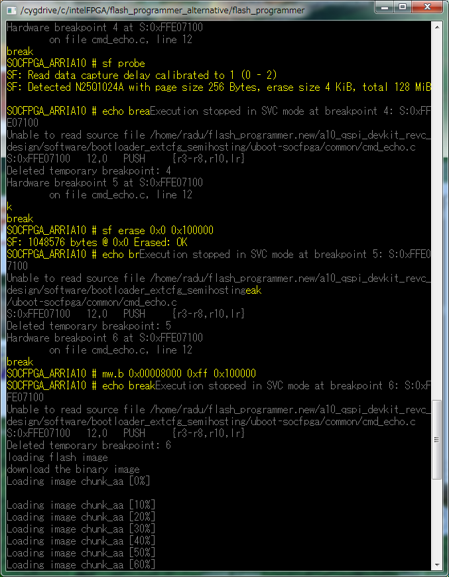

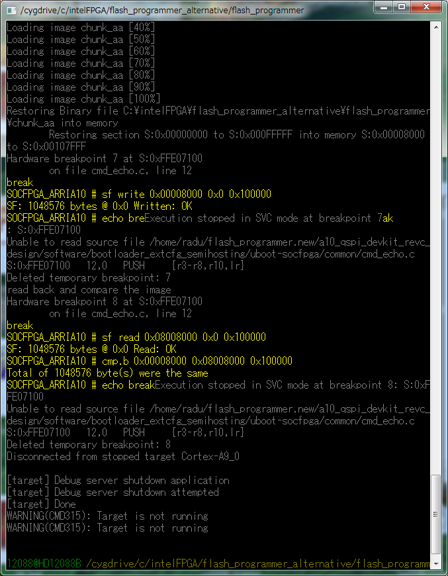

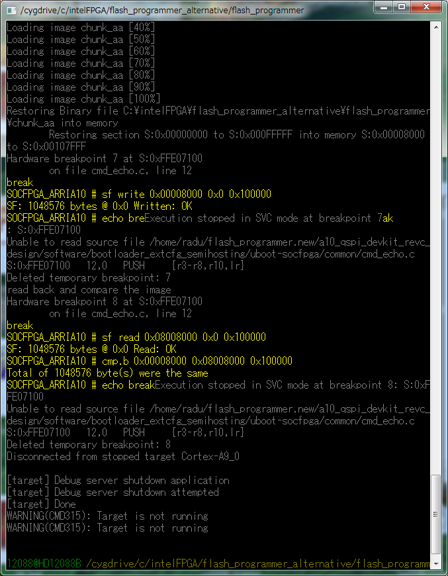

実行例

プログラミング実行時のコンソール表示内容を掲載しておきます。

Arm® DS 向け改造版スクリプト

改造内容は、オリジナルの flash_programmer.py と添付ファイルを比較ツールでご確認ください。

変更点は以下の通りです。

・デバッガーコマンド名の変更: debugger -> armdbg

・JTAG接続名(CDB_ENTRY)の変更: Altera -> Intel SoC FPGA

変更前)CDB_ENTRY = "Altera::Arria 10 SoC::Bare Metal Debug ...

変更後)CDB_ENTRY = "Intel SoC FPGA::Arria 10 SoC::Bare Metal Debug ...

・リセットコマンドの変更: reset system -> reset

補足:Arm® DS の場合は、書き込み完了(成功)後に以下のような Warning が表示されます。

------

INFO : WARNING: An illegal reflective access operation has occurred

WARNING: Illegal reflective access by org.python.netty.util.internal.PlatformDependent0 (file:/opt/arm/developmentstudio-2020.0/sw/ide/plugins/com.arm.tpip.jython_2.7.0.20200331_211023/lib/jython-2.7.0-standalone.jar) to field java.nio.Buffer.address

WARNING: Please consider reporting this to the maintainers of org.python.netty.util.internal.PlatformDependent0

WARNING: Use --illegal-access=warn to enable warnings of further illegal reflective access operations

WARNING: All illegal access operations will be denied in a future release

7月 21, 2020 2:03:47 午後 org.python.netty.util.internal.PlatformDependent <clinit>

情報: Your platform does not provide complete low-level API for accessing direct buffers reliably. Unless explicitly requested, heap buffer will always be preferred to avoid potential system unstability.

------

上記のWarningについては、Arm® DS に含まれる jython-2.7.0-standalone.jar の中の実装方法に起因するようです。該当の .jar の実装方法が、最近のJava環境で推奨外に変更となった方式で実装されているために表示されるもののようです。

Flash 書き込みには成功していますので、こちらの警告が表示される場合には無視してご使用頂く対応になるかと思います。

まとめ

今回は、python スクリプトにて Arm® DS / DS-5 を間接的に使用した Flash プログラミング方法について紹介しました。

最後に、今回の方法では Arm® DS / DS-5 デバッガーの GUI は起動しませんが Arm® DS / DS-5 のライセンスは通常通り必要となります。 Arm® DS / DS-5 のライセンス認証を行っていない PC で本スクリプトを実行しようとした場合にはライセンスエラーが発生しプログラミングを行うことができないのでご注意ください。

おすすめ記事/資料はこちら

Arm DS 活用に関する記事一覧

SoC FPGA 関連の記事や資料

インテル® FPGA の SoC FPGA

インテル® FPGA の開発フロー/FPGA トップページ