こんにちは。

マクニカでインテル® FPGA 製品の技術サポートをしている インテル・F・ハナコ です。

インテル FPGA 開発ソフトウェア Quartus® Prime には、様々なデバッグ機能が搭載されています。

その一つに、Signal Probe (シグナル・プローブ) があります。

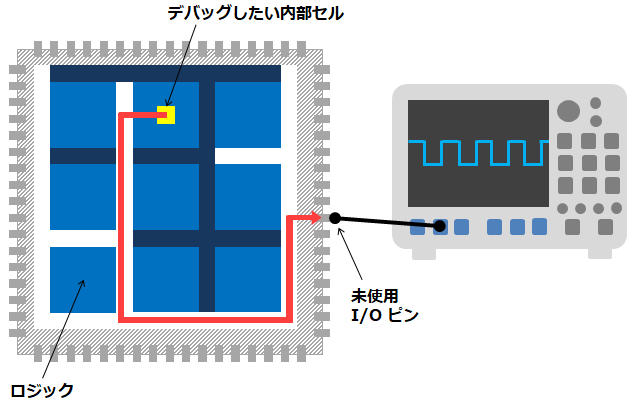

Signal Probe は、基板上で動作する FPGA の内部信号を未使用のユーザー I/O ピンに出力させ、外部機器 (オシロスコープやロジック・アナライザーなど) により信号を観測するデバッグ手法です。

しかも!

前回のコンパイル結果を保持しながら、デザインを編集することなく内部信号をピンに出力(配線)することができるため、

効率よくデバッグすることができます。

Signal Probe の特徴

Signal Probe には、以下の特徴があります。

・外部機器を使用する

・デザインを編集せずに内部信号をモニターピンへ配線可能

・デバイス内部のリソースをほとんど消費しない

・デバッグ用に予備のユーザー I/O ピンが必要

・JTAG 接続不要

・無償で使用できる

以下は、Signal Probe と Signal Tap ロジック・アナライザーを比較しています。

|

要件 |

Signal Probe |

Signal Tap ロジック・アナライザー |

| 外部機器が必要 |

〇 |

× |

| JTAG 接続が必要 |

×(1) |

〇 |

| ユーザー I/O ピンの追加 |

〇 |

×(2) |

|

未使用の内部ロジック および内部メモリーが必要 |

× |

〇 |

| 高度なトリガー機能 |

× |

〇 |

Notes:

(1) sof/pof データを書きこむ際は JTAG 接続が必要

(2) トリガー入力および出力を使用する際は、消費される

対象の Quartus Prime

Signal Probe は、以下の Quartus Prime でサポートしている機能です。

・Quartus Prime Pro Edition

・Quartus Prime Standard Edition

・Quartus Prime Lite Edition

対象のデバイス

利用する Quartus Prime がサポートするすべてのファミリーで、Signal Probe が使用可能です。

※ Arria® 10 は Quartus Prime Pro Edition をご利用ください。(Standard Edition は非サポートです。)

※ 内部メモリがない CPLD でも利用が可能です。

操作方法

Signal Probe を実施するには、事前にユーザー・デザインのコンパイルが完了している必要があります。

また、Quartus Prime のディションにより、操作方法が異なります。

|

Quartus Prime |

作業内容 |

対応方法 |

コンパイル |

| Pro Edition |

・Signal Probe 用のピンを作成する

・Signal Probe 用のピンに モニターする内部信号を割り当てる

|

スクリプトで設定 |

Rapid Recompile |

|

Signal Probe 専用の GUI で設定 |

Signal Probe Compilation (ECO※ コンパイル) |

※ ECO : Engineering Change Order

Quartus Prime Pro Edition による操作方法

Pro Edition では、下記の操作をスクリプトで設定します。

・ Signal Probe 用のピンを作成する

・ Signal Probe 用のピンにモニターする内部信号を割り当てる

以下の例では、Signal Probe 用のピン名を sp_moni としてご案内します。

なお、すでにプロジェクト・デザインはコンパイルが完了しているものとします。

① File メニュー > Open により、プロジェクトの .qsf ファイルをテキストで開きます。

② 以下のコマンドを .qsf ファイルに追記・保存し、Signal Probe ピンを予約します。

<pin_name> は、Signal Probe 用に作成したピンの名称を指定します。

set_global_assignment -name CREATE_SIGNALPROBE_PIN <pin_name>

(例) set_global_assignment -name CREATE_SIGNALPROBE_PIN sp_moni

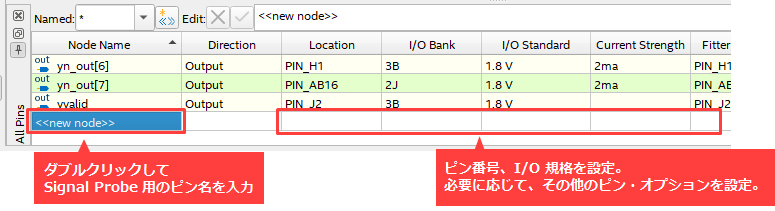

③ Pin Planner において、上記②で Signal Probe 用に作成したピン名を Node Name 欄の <<new node>> に登録し、

ピン番号、および I/O 規格などを指定します。

④ コンパイルを実行します。

⑤ 以下のコマンドを .qsf ファイルに追記・保存し、Signal Probe 用に作成したピンへ内部ノードを割り当てます。

set_instance_assignment -name CONNECT_SIGNALPROBE_PIN <pin_name> -to <node_name>

<pin_name> は、Signal Probe 用に作成したピンの名称を指定します。

<node_name> は、モニターしたい内部ノードを指定します。

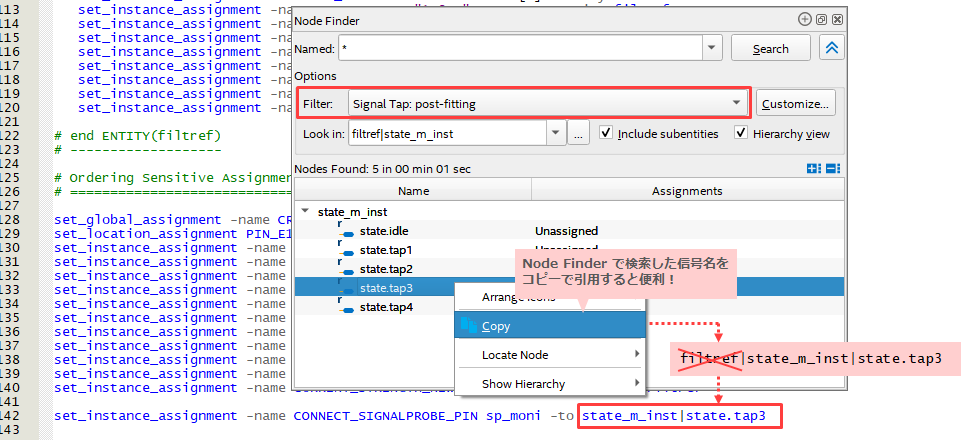

内部ノードは階層パスで記載しなければならないため、View メニュー > Node Finder において

Filter を "Signal Tap: post-fitting" にセットし、Search ボタンにより検出されたノード名を用います。

目的のノード名をコピーし、<node_name> 部分へペーストします。その際、最上位エンティティ名は不要なため、削除してください。

(例) set_instance_assignment -name CONNECT_SIGNALPROBE_PIN sp_moni -to state_m_inst|state.tap3

⑥ デザインを再コンパイルします。

このとき、デザインの変更がなく Signal Probe ピンを追加するだけであれば、通常のフルコンパイルではなく

Rapid Recompile の実行がお勧めです!

Processing メニュー > Start >Start Rapid Recompile

Pro Edition において Rapid Recompile を実行するには、Fitter において Snapshot が生成されていることが条件です。

Fitter の Snapshot を生成させるには、以下のオプションを有効にしてフルコンパイルが実行されている必要があります。

Enable Intermediate Fitter Snapshots = On (Assignments メニュー > Settings > Compiler Settings 内)

※ ver.18.0 Pro Edition ではこのオプションが存在しません。

(Rapid Recompile 実行時、"Rapid Recompile database does not exite." のメッセージや

"Rapid Recompile could not locate a design database from a previous compilation on disk." のエラーが発生しない場合は、

必須ではありません。)

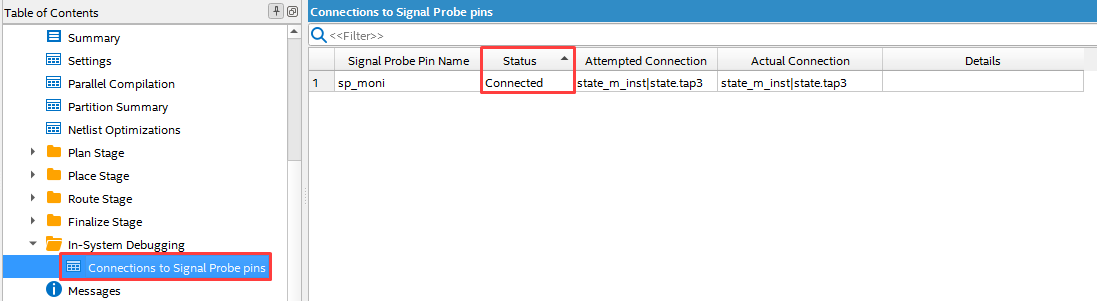

⑦ コンパイル・レポート (Processing メニュー > Compilation Report) において、

Fitter フォルダ > In-System Debugging フォルダ > Connections to Signal Probe pins をクリックし

内部信号が Signal Probe ピンへルーティングできたかを Status カラムの表記で確認します。

|

Status |

説明 |

| Connected | ルーティングは成功しました。 |

| Unconnected |

ルーティングは成功しませんでした。考えられる理由は次のとおりです。 ・ノードが I/O セル または 別のハード IP に属しているため、ルーティング不可能です。 ・デザインにノード階層パスが存在しません。 ・ノードが Signal Tap: post-fitting ではありません。 |

⑧ デバイスへファイルを書き込んだ後、Signal Probe を設定したピンを外部測定器(ロジック・アナライザー、オシロスコープなど)で観測します。

Pro Edition における Signal Probe の操作は以上です。

Quartus Prime Standard/Lite Edition による操作方法

Standard および Lite Edition では、下記の操作を Signal Probe 専用の GUI で設定します。

・ Signal Probe 用のピンを作成する

・ Signal Probe 用のピンにモニターする内部信号を割り当てる

以下の例では、Signal Probe 用のピン名を sp_moni としてご案内します。

なお、すでにプロジェクト・デザインはコンパイルが完了しているものとします。

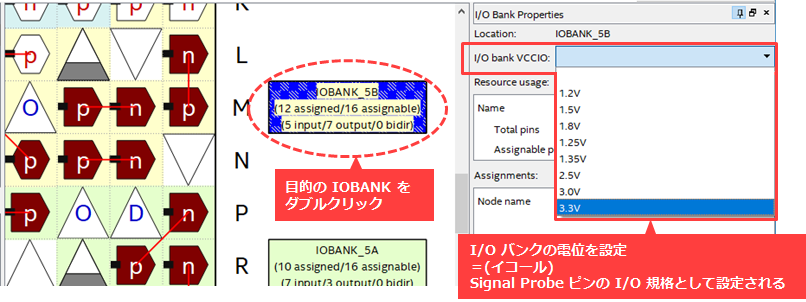

① Signal Probe 用のピンに、I/O 規格を事前に設定します。

Note:

Signal Probe 用のピンの I/O 規格 (I/O Standard)は、配置させるピン番号が属する I/O バンクの VCCIO 電位設定値に委ねられます。

もし、I/O バンクの VCCIO 電位を固有に設定していない場合は、Device and Pin Options (Assignmentsメニュー > Device) の Voltage で設定する

Default I/O Standard の電位設定値に委ねられます。

そのため、事前に Signal Probe 用のピンをアサインするピン番号が属する I/O バンクの電位を設定します。

[参考情報] I/O バンクとは? (リンク先ページの "I/O バンクとは?" をご覧ください。)

Assignments メニュー > Pin Planner を起動し、目的の IOBANK_XX をダブルクリックします。

表示された I/O Bank Properties ウィンドウにおいて、 I/O bank VCCIO を設定します。

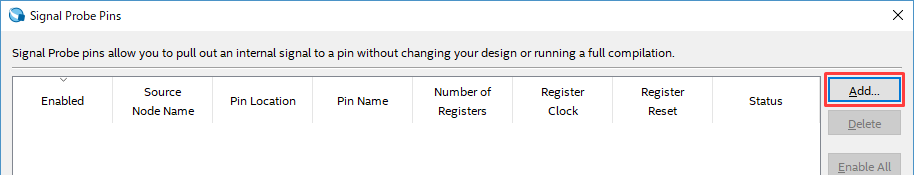

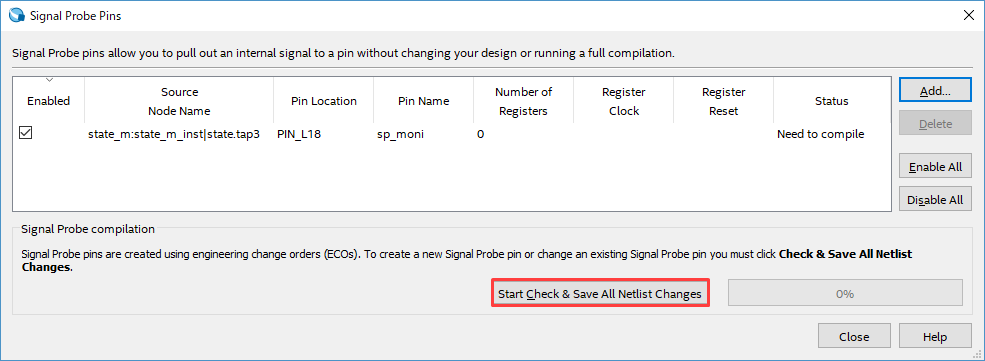

② Tools メニュー > Signal Probe Pins を起動します。

Add ボタンをクリックすると、Add Signal Probe Pin ダイアログボックスが表示されます。

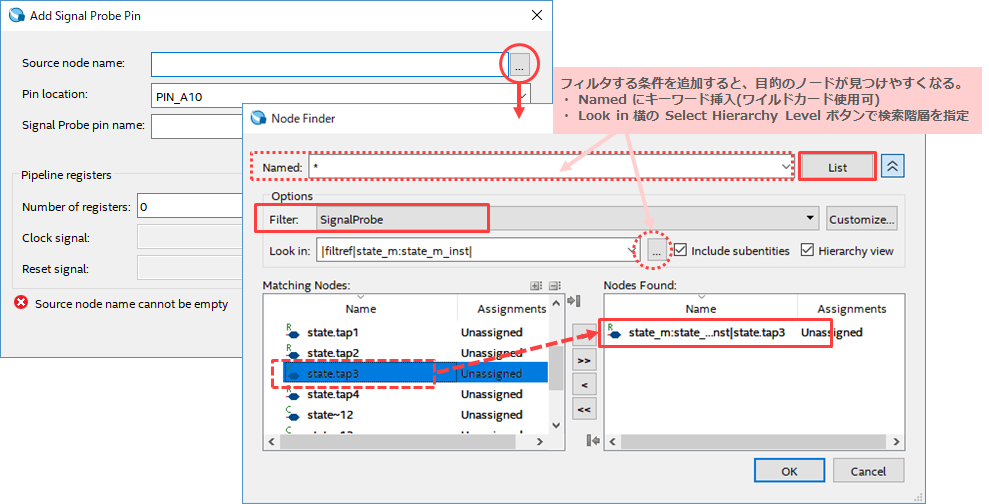

③ Add Signal Probe Pin ダイアログボックスの Source node name 右横のブラウズボタンをクリックし、Node Finderを起動します。

Filter を "SignalProbe" にセットし、List ボタンをクリックします。

検出されたノードから、モニターするノードを Matching Nodes 欄から Nodes Found 欄へ選出します。

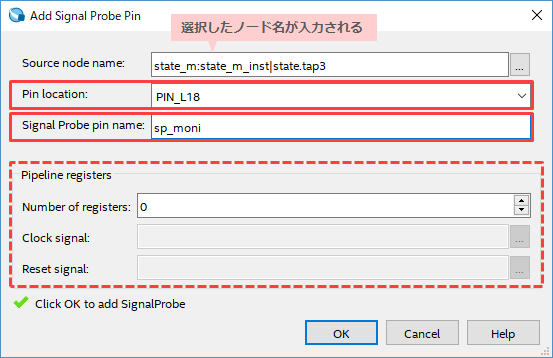

④ Add Signal Probe Pin ダイアログボックスにおいて、他の項目を設定します。

| Pin location |

Signal Probe 用のピンをアサインするピン番号を選択します。 (リストには、未使用のユーザー I/O ピンの番号のみが表示) |

| Signal Probe pin name |

Signal Probe 用のピン名を入力します。 (この例では、sp_moni と入力) |

| Pipeline registers |

Signal Probe で出力する信号にレジスタを挿入する場合は、以下を設定します。 ・挿入するレジスタ数 (Number of registers) ・レジスタを制御するクロック信号 (Clock signal) ・レジスタを制御するリセット信号 (Reset signal) |

設定後に内容を変更する場合は、各項目をダブルクリックし、編集してください。

⑤ Signal Probe Compilation を実行します。

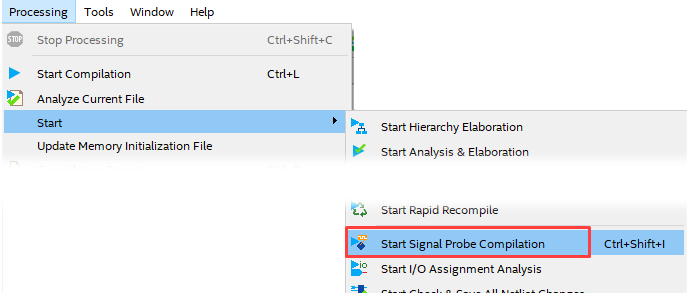

Processing メニュー > Start > Start Signal Probe Compilation

ECO (Engineering Change Order) コンパイルが実行されます。

もし、Start Signal Probe Compilation が非アクティブで選択できない場合は、Tools メニュー > Signal Probe Pin を起動し、

ダイアログボックス右下にある Start Check & Save All Netlist Changes ボタンをクリックします。

“ECO Fitting was successful” のメッセージを確認したら、Signal Probe Compile 完了です。

ハナコ’s ポイント♪

Signal Probe Compilation 実行中に以下のエラーになった場合は、Signal Probe Pin の I/O 規格が正しく設定されていない可能性があります。

ID:169026

Pin <name> with I/O standard assignment <name> is incompatible with I/O bank <name>. I/O standard <name>, has a VCCIO requirement of <number>, which incompatible with the I/O bank's VCCIO setting or with other output or bidirectional pins in the I/O bank using a VCCIO requirement of <number>. Assign output and bidirectional pins with different VCCIO requirements to different I/O banks, or change the I/O standard assignment for the specified pin to a compatible I/O standard. The Intel FPGA Knowledge Database contains many articles with specific details on how to resolve this error. Visit the Knowledge Database at https://www.altera.com/support/support-resources/knowledge-base/search.html and search for this specific error message number.

回避策はこちらをご覧ください。

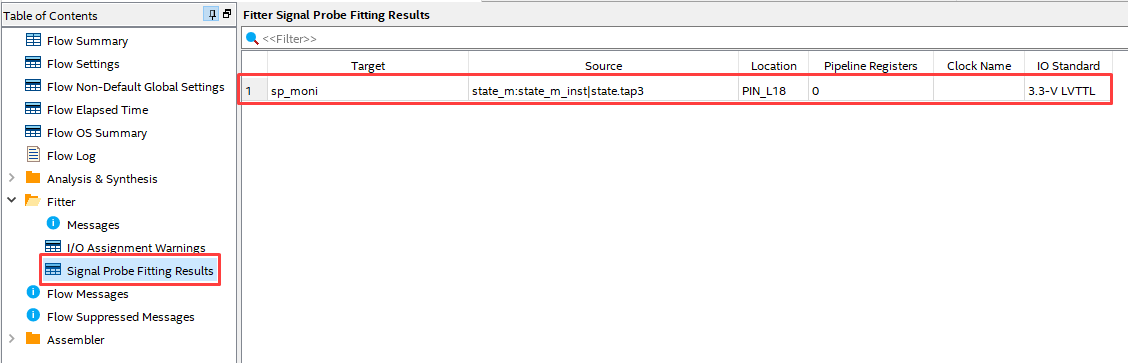

⑥ コンパイル・レポート (Processing メニュー > Compilation Report) において、

Fitter フォルダ > Signal Probe Fitting Results をクリックし、内部信号が Signal Probe ピンへルーティングできたかを確認します。

⑦ デバイスへファイルを書き込んだ後、Signal Probe を設定したピンを外部測定器(ロジック・アナライザー、オシロスコープなど)で観測します。

Standard および Lite Edition における Signal Probe の操作は以上です。

Signal Probe Compilation で Error ID: 169026 が発生したときの回避方法

(※ Standard および Lite Edition のみ)

Signal Probe Compilation 中に Error ID: 169026 が発生した要因は、

Signal Probe ピンに設定された I/O 規格の電位と、Signal Probe が属する I/O バンクの VCCIO 電位とが一致しないためです。

回避するには、以下の操作を行ってください。

- Signal Probe Pins において、該当する設定を削除 (Delete)

- 作業①のとおり、I/O バンクの電位を正しく設定

- Signal Probe Pins において、再びピンを設定

- Signal Probe Pins 内の Start Check & Save All Netlist Changes を実行

おすすめ記事/資料はこちら

FPGA オンチップ・デバッグ "Signal Tap" をやってみよう

Quartus® はじめてガイド - Signal Tap ロジック・アナライザの使い方