インテル® SoC FPGA では HPS (ハード・プロセッサー・システム) 側のブートローダーに U-Boot を採用していますが、U-Boot に実装されるコマンド機能を使用することで Ethernet の疎通チェックが行えます。ボード立ち上げ確認時など、本番用のソフトウェア、OS/ドライバーの準備が整う前の簡易テストに利用可能です。

準備 : U-Boot の設定

使用する U-Boot には特別なカスタマイズは必要ありません。

インテル® SoC FPGA エンベデッド開発スイート (SoC EDS) ツール付属の BSP-Editor で生成される Preloader/U-Boot プロジェクトをそのまま make するだけで大丈夫です。

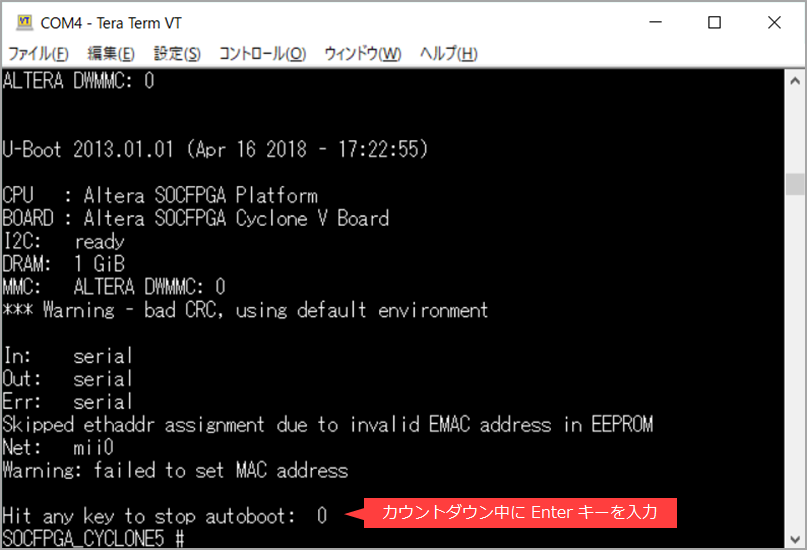

シリアルターミナルを接続した状態でターゲットボードの電源を投入。

U-Boot のカウントダウン表示中に Enter キーを入力して、コマンド待ち受けのプロンプトが表示された状態にします。

この記事では、Cyclone® V SoC ターゲットの U-Boot で試した内容を基にしていますが、他のデバイスファミリーでも同様の手順でご確認いただけるはずです。

あらかじめ U-Boot のビルドおよび書き込み方法については理解していることを前提として記載しています。

環境変数設定 (MAC アドレス)

Ethernet の確認を行う場合は、MAC アドレスの設定が必須となります。

U-Boot 実行中のターミナルログに “Warning: failed to set MAC address” と表示される場合は MAC アドレス未設定を意味するので、以下のように setenv および saveenv コマンドで MAC アドレス (ethaddr) を設定・保存します。

SOCFPGA_CYCLONE5 # setenv ethaddr 02:11:22:33:44:55

SOCFPGA_CYCLONE5 # saveenv

Saving Environment to MMC...

Writing to MMC(0)... doneIP アドレスの設定

同じように IPアドレス (ipaddr) および サブネットマスク (netmask) の設定も行います。

SOCFPGA_CYCLONE5 # setenv ipaddr 192.168.10.101

SOCFPGA_CYCLONE5 # setenv netmask 255.255.255.0※dhcp コマンドも用意されていますが、お勧めできません。

以下、参考までに dhcp 実行時のログを掲載します。

最初に IP アドレスの取得が行われますが、続けてイメージのロードが実行されてしまいます。(途中でキャンセル (Ctrl+C) することで、DHCP から IPアドレスを取得すること自体はできるようです。)

SOCFPGA_CYCLONE5 # dhcp

BOOTP broadcast 1

DHCP client bound to address 192.168.10.24

*** Warning: no boot file name; using '0AD92318.img'

Using mii0 device

TFTP from server 0.0.0.0; our IP address is 192.168.10.24

Filename '0AD92318.img'.

Load address: 0x8000

Loading: *T T T T

Abortping コマンド実行: 疎通チェック (ICMP パケット送受信)

宛先の IP アドレス (例:192.168.10.100) を指定して ping コマンドを実行します。

初回は Linkup を行う旨のログと Linkup 結果も表示されます。

応答が得られず疎通失敗した場合は、“ping failed; host XX.XX.XX.XX is not alive” の表示になります。

SOCFPGA_CYCLONE5 # ping 192.168.10.100

Waiting for PHY auto negotiation to complete..... done

ENET Speed is 1000 Mbps - FULL duplex connection

Using mii0 device

ping failed; host 192.168.10.100 is not alive疎通成功の場合は、“host XX.XX.XX.XX is alive” の表示になります。

SOCFPGA_CYCLONE5 # ping 192.168.10.100

Using mii0 device

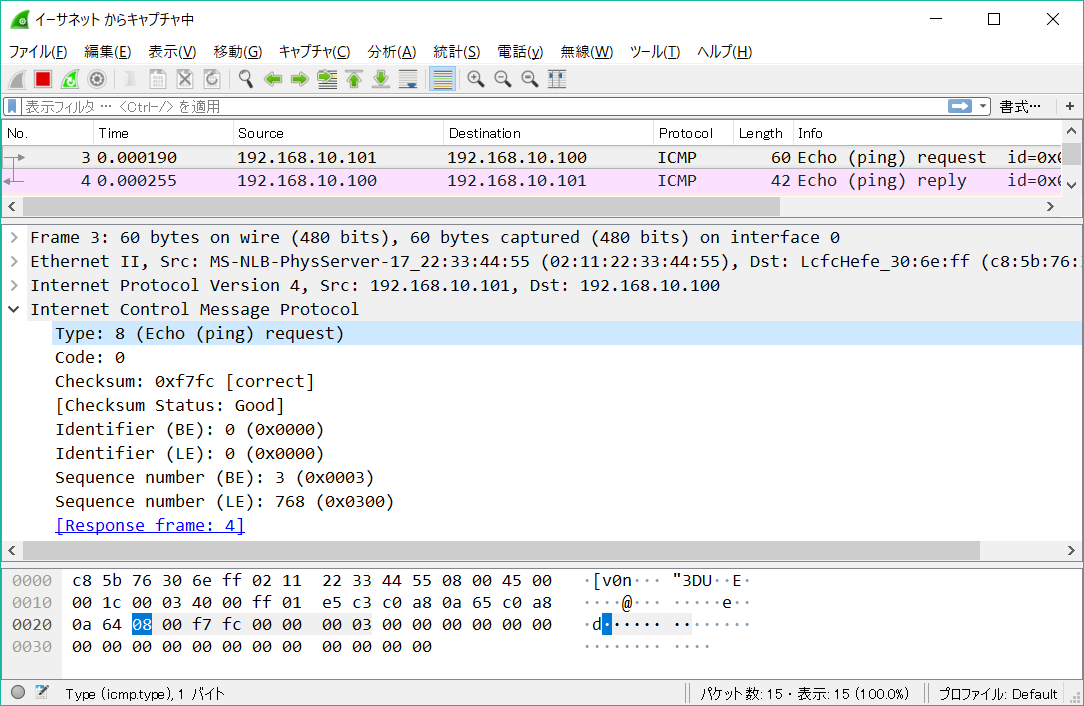

host 192.168.10.100 is alive宛先 (PC) 側でパケットモニターツールを使用すると、実際にパケット送受信が行われたことが確認できます。

(おまけ) mii, mdio コマンド: PHY レジスタの Read/Write

U-boot コマンドの一覧 (help コマンドで表示) には、ping 以外にも Ethernet 関連のコマンドが用意されているようです。

以下に mdio, mii というコマンドの help 表示を掲載しておきます。

<mii コマンド HELP>

SOCFPGA_CYCLONE5 # help mii

mii - MII utility commands

Usage:

mii device - list available devices

mii device <devname> - set current device

mii info <addr> - display MII PHY info

mii read <addr> <reg> - read MII PHY <addr> register <reg>

mii write <addr> <reg> <data> - write MII PHY <addr> register <reg>

mii dump <addr> <reg> - pretty-print <addr> <reg> (0-5 only)

Addr and/or reg may be ranges, e.g. 2-7.<mdio コマンド HELP>

SOCFPGA_CYCLONE5 # help mdio

mdio - MDIO utility commands

Usage:

mdio list - List MDIO buses

mdio read <phydev> [<devad>.]<reg> - read PHY's register at <devad>.<reg>

mdio write <phydev> [<devad>.]<reg> <data> - write PHY's register at <devad>.<reg>

<phydev> may be:

<busname> <addr>

<addr>

<eth name>

<addr> <devad>, and <reg> may be ranges, e.g. 1-5.4-0x1f.興味のある方は実際にコマンドを実行してお試しください。

以下に、試しに実行してみた結果のログを添付しておきます。

<mii コマンド 実行例>

SOCFPGA_CYCLONE5 # mii info 1

PHY 0x01: OUI = 0x0885, Model = 0x22, Rev = 0x02, 1000baseT, FDX

SOCFPGA_CYCLONE5 # mii dump 1 0

0. (1000) -- PHY control register --

(8000:0000) 0.15 = 0 reset

(4000:0000) 0.14 = 0 loopback

(2040:0000) 0. 6,13 = b00 speed selection = 10 Mbps

(1000:1000) 0.12 = 1 A/N enable

(0800:0000) 0.11 = 0 power-down

(0400:0000) 0.10 = 0 isolate

(0200:0000) 0. 9 = 0 restart A/N

(0100:0000) 0. 8 = 0 duplex = half

(0080:0000) 0. 7 = 0 collision test enable

(003f:0000) 0. 5- 0 = 0 (reserved)

SOCFPGA_CYCLONE5 # mii dump 1 1

1. (796d) -- PHY status register --

(8000:0000) 1.15 = 0 100BASE-T4 able

(4000:4000) 1.14 = 1 100BASE-X full duplex able

(2000:2000) 1.13 = 1 100BASE-X half duplex able

(1000:1000) 1.12 = 1 10 Mbps full duplex able

(0800:0800) 1.11 = 1 10 Mbps half duplex able

(0400:0000) 1.10 = 0 100BASE-T2 full duplex able

(0200:0000) 1. 9 = 0 100BASE-T2 half duplex able

(0100:0100) 1. 8 = 1 extended status

(0080:0000) 1. 7 = 0 (reserved)

(0040:0040) 1. 6 = 1 MF preamble suppression

(0020:0020) 1. 5 = 1 A/N complete

(0010:0000) 1. 4 = 0 remote fault

(0008:0008) 1. 3 = 1 A/N able

(0004:0004) 1. 2 = 1 link status

(0002:0000) 1. 1 = 0 jabber detect

(0001:0001) 1. 0 = 1 extended capabilities

SOCFPGA_CYCLONE5 # mii dump 1 2

2. (0022) -- PHY ID 1 register --

(ffff:0022) 2.15- 0 = 34 OUI portion

SOCFPGA_CYCLONE5 # mii dump 1 3

3. (1622) -- PHY ID 2 register --

(fc00:1400) 3.15-10 = 5 OUI portion

(03f0:0220) 3. 9- 4 = 34 manufacturer part number

(000f:0002) 3. 3- 0 = 2 manufacturer rev. number

SOCFPGA_CYCLONE5 # mii dump 1 4

4. (01e1) -- Autonegotiation advertisement register --

(8000:0000) 4.15 = 0 next page able

(4000:0000) 4.14 = 0 reserved

(2000:0000) 4.13 = 0 remote fault

(1000:0000) 4.12 = 0 reserved

(0800:0000) 4.11 = 0 asymmetric pause

(0400:0000) 4.10 = 0 pause enable

(0200:0000) 4. 9 = 0 100BASE-T4 able

(0100:0100) 4. 8 = 1 100BASE-TX full duplex able

(0080:0080) 4. 7 = 1 100BASE-TX able

(0040:0040) 4. 6 = 1 10BASE-T full duplex able

(0020:0020) 4. 5 = 1 10BASE-T able

(001f:0001) 4. 4- 0 = 1 selector = IEEE 802.3

SOCFPGA_CYCLONE5 # mii dump 1 5

5. (cde1) -- Autonegotiation partner abilities register --

(8000:8000) 5.15 = 1 next page able

(4000:4000) 5.14 = 1 acknowledge

(2000:0000) 5.13 = 0 remote fault

(1000:0000) 5.12 = 0 (reserved)

(0800:0800) 5.11 = 1 asymmetric pause able

(0400:0400) 5.10 = 1 pause able

(0200:0000) 5. 9 = 0 100BASE-T4 able

(0100:0100) 5. 8 = 1 100BASE-X full duplex able

(0080:0080) 5. 7 = 1 100BASE-TX able

(0040:0040) 5. 6 = 1 10BASE-T full duplex able

(0020:0020) 5. 5 = 1 10BASE-T able

(001f:0001) 5. 4- 0 = 1 selector = IEEE 802.3

SOCFPGA_CYCLONE5 # mii dump 1 6

The MII dump command only formats the standard MII registers, 0-5.

SOCFPGA_CYCLONE5 #<mdio コマンド 実行例>

SOCFPGA_CYCLONE5 # mdio list

mii0:

1 - Generic PHY <--> mii0

SOCFPGA_CYCLONE5 # mdio read mii0 0

Reading from bus mii0

PHY at address 1:

0 - 0x1000

SOCFPGA_CYCLONE5 # mdio read mii0 1

Reading from bus mii0

PHY at address 1:

1 - 0x796d

SOCFPGA_CYCLONE5 # mdio read mii0 2

Reading from bus mii0

PHY at address 1:

2 - 0x22

SOCFPGA_CYCLONE5 # mdio read mii0 3

Reading from bus mii0

PHY at address 1:

3 - 0x1622

SOCFPGA_CYCLONE5 #まとめ

最後に注意点です。

U-Boot に実装される Ethernet ドライバーは受信側の待ち受けを常時行っていないようです。

そのため、他の端末からの ping (ICMPリクエスト) には応答できません。

あくまでも U-Boot コマンドからの ping 送信を契機に、宛先端末からのレスポンスを待ち受けるのみの動作となっています。

このように、U-Boot に実装される Ethernet プログラムは非常に簡易的な物となっています。

U-Boot では疎通確認レベルの簡易テストに留め、詳細は本番用のソフトウェア環境で実施されることをお勧めいたします。

おすすめ記事/資料はこちら

インテルの SoC FPGA(SoC FPGA 関連情報まとめページ)

SoC FPGA 関連の記事や資料

インテル® FPGA の開発フロー/FPGA トップページ