こんにちは。

マクニカで Altera® FPGA 製品の技術サポートをしている アルテラ ハナコ です。

Questa* - Altera® FPGA Edition などでファンクション・シミュレーションを実施する際に、Altera® FPGA のピンレベルで信号を参照 (モニター) することはもちろんですが、同時に FPGA の内部信号も参照したいですよね?

シミュレーションで FPGA の内部信号を Wave ウィンドウに表示させるには、以下の方法があります。

[B] Questa* - Altera® FPGA Edition の GUI 操作で表示する

今回は [B] Questa* - Altera® FPGA Edition の GUI 操作で FPGA の内部信号を Wave ウィンドウに表示する方法 をご紹介します。

後半では、NativeLink シミュレーション・ユーザー向けの 「ハナコのちょこっとポイント ♪」 コーナー もあります。

この方法を使えば、シミュレーションの作業効率がアップしますよ~。お試しあれ!

サンプル・デザイン

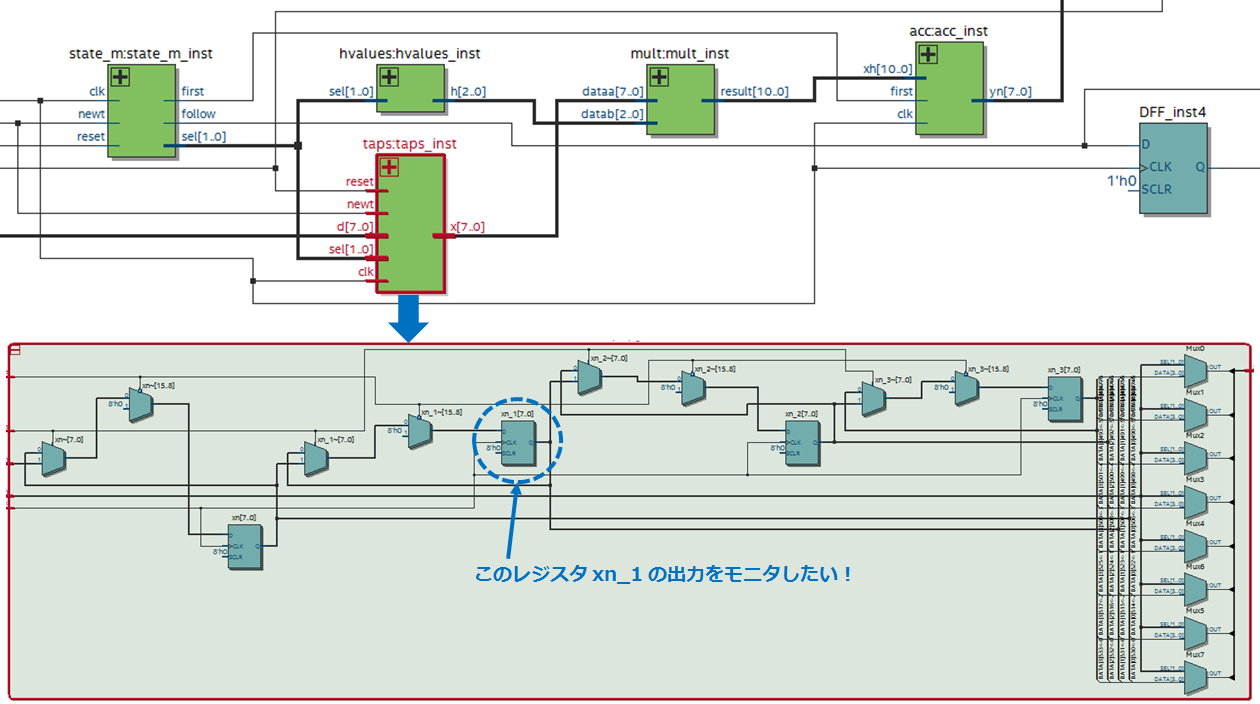

下図は、あるサンプル・デザインを Quartus® Prime の RTL Viewer で表示したものです。

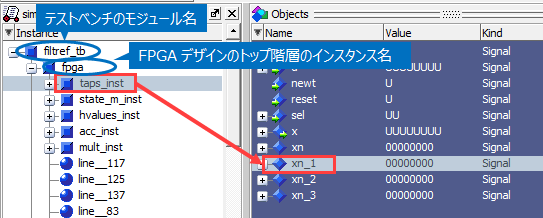

このデザインの下位モジュールに taps (インスタンス名: taps_inst) があります。

今回は、taps の内部のレジスタ xn_1 (7bit) の出力を参照する場合を例に挙げてご案内します。

なお、テストベンチにおける FPGA の最上位モジュールのインスタンス名は、fpga としています。

Questa* - Altera® FPGA Edition の GUI 操作

① Questa* - Altera® FPGA Edition において、ソースのコンパイルおよびロード (Start Simulation) の実行を完了させます。

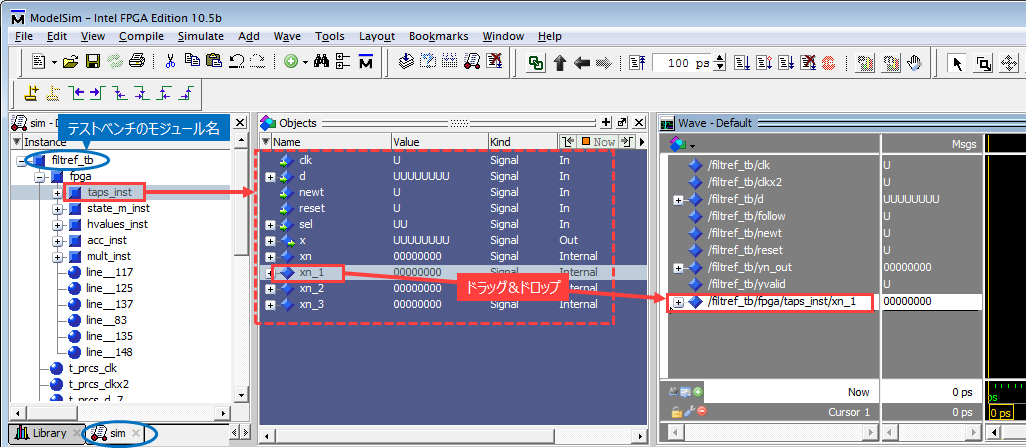

② Srtructure ウィンドウ (sim タブ) に表示されたデザインの階層ビューから目的のインスタンス (taps_inst) を選択します。

③ Objects ウィンドウに、指定したインスタンスのポートや内部レジスタが表示されます。

ここから目的の信号 (xn_1) をドラッグ&ドロップで、Wave ウィンドウにインポートします。

④ シミュレーションを実行(run)します。

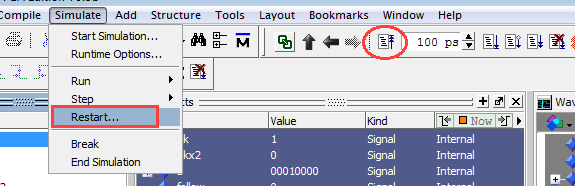

シミュレーション実行後に内部信号を追加した場合は、

シミュレーションをリセット (Simulation メニュー > Run > Restart、またはアイコン) し、再度 0ns から実行してください。

ハナコのちょこっとポイント♪

NativeLink でシミュレーションを実行している場合、自動的にシミュレーションまで実施されます。

内部信号を Wave ウィンドウに追加するとなると、NativeLink で一度シミュレーションを完了させた後にリセット (Restart) し、再度 0ns からシミュレーションするので、何か 2度手間 ですよね?

なので、事前に Wave ウィンドウに内部信号を追加するスクリプトを追加してしまいましょう!

その、信号を追加するオリジナル・スクリプトを作成し、Quartus Prime に登録します。

① テキスト・エディターを新規で開きます。

② Wave ウィンドウに登録する信号を、add wave コマンドで指定します。

* (アスタリスク)でテストベンチ上の全てのポートを指定します。

add wave *内部信号は、各階層のインスタンス名を使って、階層パスを指定します。

例えば、taps:taps_inst 内のレジスタ xn_1 の出力を参照したい場合には、以下のように記述します。

add wave /fpga/taps_inst/xn_1つまり、こういうことです。

③ シミュレーション実行を指示する run コマンドを記載します。

run -all実行時間を指定する場合は、rum 500 ms のように指示します。

④ スクリプト・ファイルの拡張子を .do として保存します。(これまでのコマンドをまとめて以下に掲載)

add wave *

add wave /fpga/taps_inst/xn_1

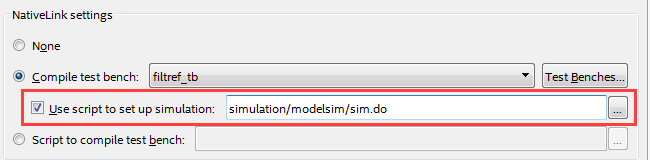

run -all⑤ Quartus Prime の Assignments メニュー > Settings > EDA Tool Settings > Simulation の NativeLink settings において、

Use script to set up simulation オプションを有効にし、ブラウズボタンから作成したオリジナルのスクリプトを追加登録します。

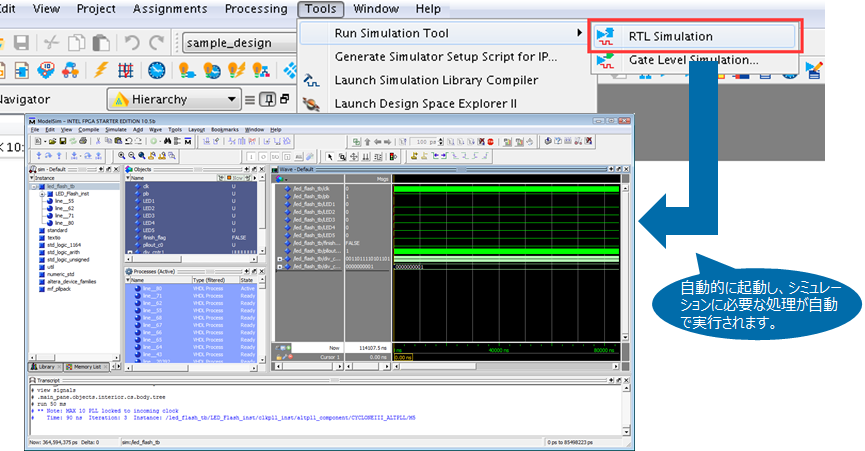

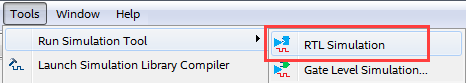

⑥ Tools メニュー > Run Simulation Tool > RTL Simulation を選択し、シミュレーションを実行します。

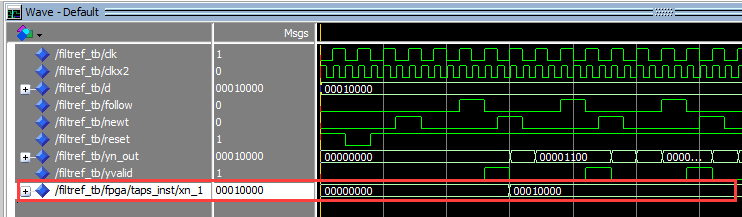

指定した内部信号が Wave ウィンドウに追加され、シミュレーションが実行されています。

ね!簡単ですよね。

皆さんも即実践してください。

今回は、Questa* - Altera® FPGA Edition でデザインの内部信号をモニターする方法をご紹介しました。

この一連の操作をテストベンチに書いてしまう方法もあります。

これなら GUI オペレーションいらずで内部信号をモニタできて、さらにデバッグ効率アップです!

詳細は、シミュレーションで Altera® FPGA の内部信号をモニターしよう (テストベンチの書き方) をご覧ください。

おすすめ記事/資料はこちら

FPGA のファンクション・シミュレーションは NativeLink で解決しよう