Nios® II プロセッサーはAltera® FPGA のために設計された 32 ビット組み込み用途向けプロセッサー・アーキテクチャーです。

Nios® II は、DSP からシステム制御までの幅広い組み込みコンピューター用途に適しています。

このページでは、Nios® II を使用するユーザー向けに、開発に必要な情報やコンテンツをご紹介します。

下記ボタンをクリックして、知りたい情報にアクセスしてください。

*Nios® II エンベデッド・デザイン・スイート(以下、Nios® II EDS)

*Nios® II Software Build Tools for Eclipse(以下、Nios® II SBT)

![]() 新着情報

新着情報

2023.06 [更新] Nios® II まとめページ に新しい記事が追加されました。

1. Nios® II とは?

全てのAltera® FPGA に搭載可能な 32 ビットの RISC ソフトコア・プロセッサーです。

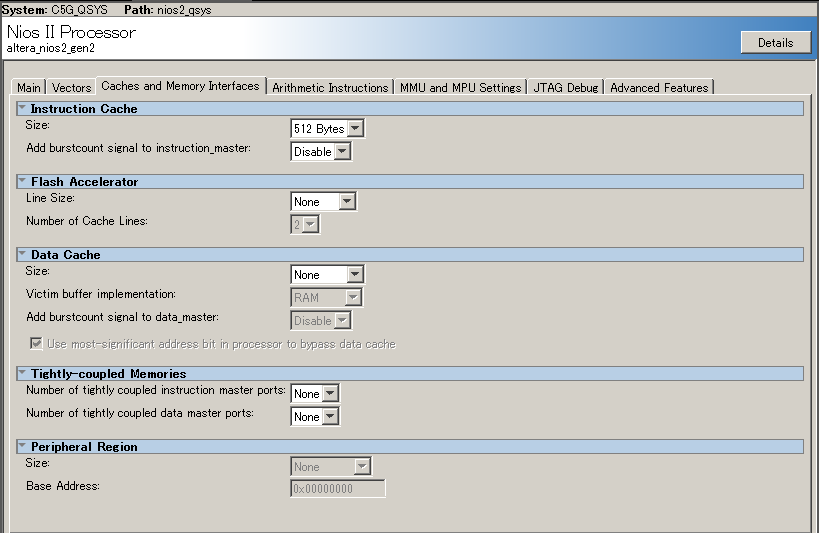

ソフトコアのため、システムの設計者が所望の Nios® II コア(Nios® II/f [Fast]、Nios® II/e [Economy])を選定して生成し、キャッシュのサイズや演算器の実装など通常のマイコンでは固定のものも設定が可能です。

※ Nios® II/e [Economy] は、無償で利用可能です。

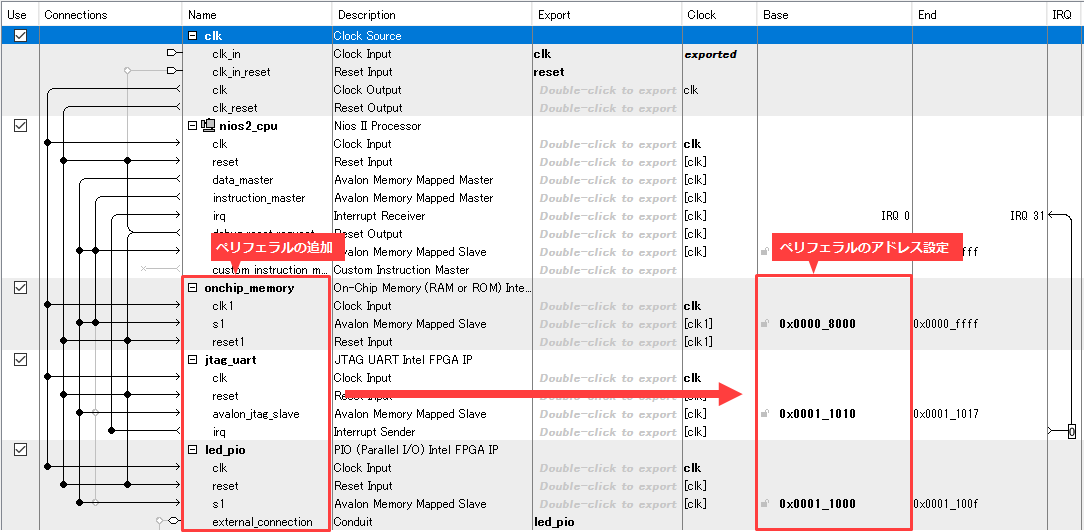

また、ペリフェラルも設計者自身で選択するため、アドレスマップも自由に決定することが可能です。

Nios® II の世代(Generation)について

Nios® II には、以下 2 つの世代(Generation)が存在します。

・ Nios® II Classic プロセッサー(または Nios® II Gen 1 プロセッサー)

・ Nios® II プロセッサー(または Nios® II Gen 2 プロセッサー)

Nios® II Classic プロセッサー機能の開発は、Quartus® II 14.0 のリリースをもって終了し、Nios® II Gen2 プロセッサーは、Quartus® II 14.1 リリース以降でのみ使用できます。

Classic プロセッサーは継続してサポートされますが、今後の設計においては Gen2 コアを使用することをメーカーではおすすめしています。

Web サイト上には、Classic プロセッサー用の資料も存在していますので、ご使用の Nios® II プロセッサーに適した資料やサンプルをご利用ください。

【参考】 Nios® II Gen2 プロセッサー・リファレンス・ガイド

⚠ 注記 :

※ 基本的に Nios® II Gen 2 は Nios® II Classic の上位互換になっていますが、一部機能で差異があるものがありますのでご注意ください。

※ 本ページでは主に Nios® II Gen 2 プロセッサーの情報を掲載しています。

2. Nios® II 開発に必要なツールと開発フロー

Nios® II の開発フローとしては、「ハードウェア開発プロセス」 と 「ソフトウェア開発プロセス」 に分けられます。

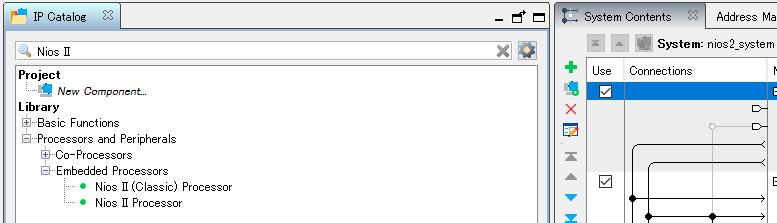

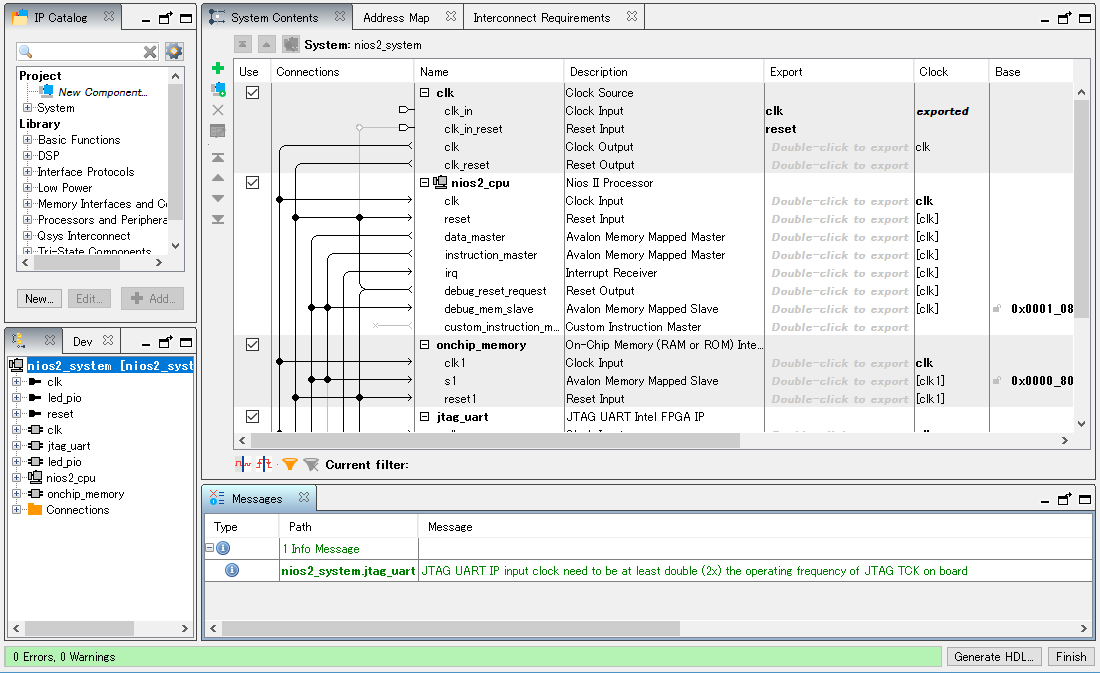

ハードウェア開発プロセスでは、Nios® II 自体の設定やペリフェラルの設定をAltera® Quartus® Prime 開発ソフトウェアに含まれるプラットフォーム・デザイナー(Platform Designer、旧 Qsys)で行います。

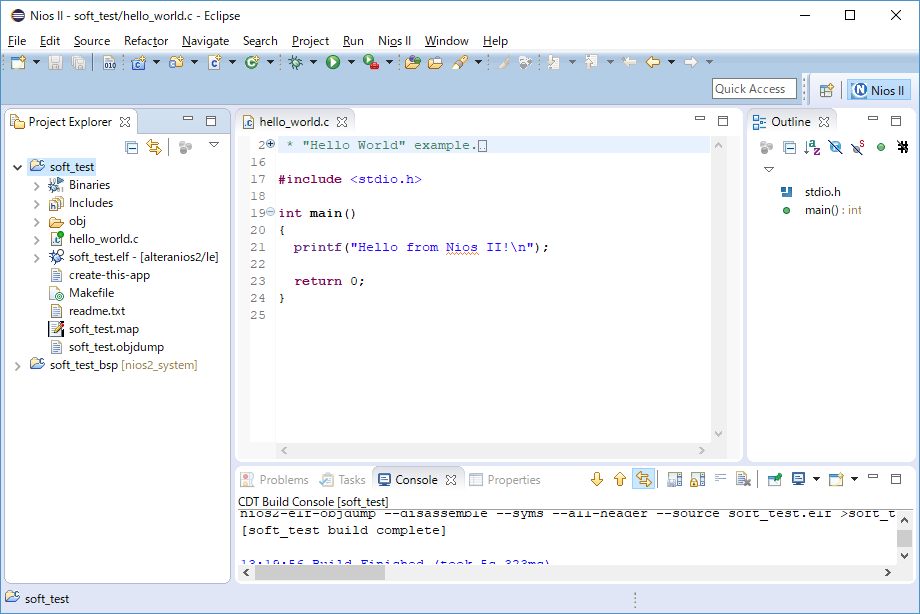

ソフトウェア開発プロセスでは、Nios® II EDS に含まれる一般的な Eclipse ベースの Nios® II SBT にて行います。

ハードウェア開発プロセス(Platform Designer)

・ Nios® II ハードウェアは、Platform Designer を使用してデザインします。

・ Quartus® Prime パッケージのコンポーネントを使用し Nios® II システムの設定と生成を行います。

Platform Designer でハードウェアの設定を生成を終えた後、Quartus® Prime は合成、ターゲットの FPGA システム全体の配置と接続の実装を行います。

・ 設定のための GUI によりユーザーは Nios® II の詳細な実装を選択することができ、ペリフェラルと I/O ブロック(タイマーやメモリー・コントローラー、シリアル・インターフェースなど)を組み込むことができます。

【参考】 Quartus® Prime Platform Designer (旧 Qsys) システム統合ツール

ソフトウェア開発プロセス(Nios® II SBT)

・ Nios® II EDS は、Nios® II ソフトウェア・デザイン用の包括的な開発パッケージです。

・ Nios® II EDS には開発ツールだけではなく、ソフトウェア、デバイスドライバー、ベアメタル・ハードウェア抽象化レイヤー(HAL)ライブラリーなどが含まれています。

・ Nios® II EDS に含まれる、Nios® II SBT は、編集、ビルド、デバッグなど、すべての Nios® II ソフトウェア開発作業を行うことができる統合環境です。

3. Nios® II のパートナー・リンク

エンベデッド・オペレーティング・システム(OS)

下表に、Nios® II をサポートしているオペレーティング・システム(OS)をご案内します。

|

オペレーティング・システム |

ベンダー |

| eCosPro® | eCosCentric |

| eCos® | Zylin |

| embOS | Segger |

| Euros® | Euros |

| FreeRTOS™ | FreeRTOS |

| Linux™ |

(オープンソース・コミュニティー) |

|

(Nios® II EDS に含まれる評価版で、ライセンスは別扱いです) |

(日本代理店: テクノ・ロジックより提供) |

| TargetOS™ | Blunk Microsystems |

| ThreadX® |

(日本代理店: グレープシステムより提供) |

| Toppers | Toppers |

| µCLinux |

(オープンソース・コミュニティー) |

| µC3® | イー・フォース |

| Zephyr™ |

(Linux™ Foundation プロジェクト) |

表3-1: Nios® II をサポートしているオペレーティング・システム

ミドルウェアとグラフィックス・ライブラリー

下表に、Nios® II をサポートしているミドルウェアとグラフィックス・ライブラリーをご案内します。

|

会社名 |

OS サポート |

ネットワーク・スタック |

ファイルシステム |

グラフィックス ・ライブラリー |

USB スタック |

その他 |

| eCosCentric | eCosPro® |

内蔵 |

内蔵 |

----- |

----- |

----- |

| Express Logic (日本代理店: グレープシステムより提供) |

ThreadX® | NetX™ | FileX® | GUIX | USBX |

----- |

| InterNiche |

任意 |

NicheStack TCP/IP ネットワーク・スタック – Nios® II エディション (Nios® II EDS に含まれますが、ライセンスは別扱いです) |

----- |

----- |

----- |

----- |

| Mentor Graphics | Nucleus® | Nucleus Networking | Nucleus Storage | Nucleus UI | Nucleus USB |

----- |

| Micrium (日本代理店: テクノ・ロジックより提供) |

µC/OS-II™ | Micrium TCP/IP | µC/OS-FS | µC/OS GUI | Micrium USB | µC/OS CAN |

| Micro Digital |

任意 |

----- |

----- |

----- |

----- |

GoFast® 浮動小数点ライブラリー |

| Altera® FPGA |

任意 |

Design Store | 読み取り専用 Zip ファイルシステム (Nios® II EDS に含まれます) |

Design Store |

----- |

----- |

| TES |

任意 |

----- |

----- |

DAVE 2D & 3D |

----- |

----- |

| uGFX |

任意 |

----- |

----- |

uGFX |

----- |

----- |

表3-2: Nios® II をサポートしているミドルウェアとグラフィックス・ライブラリー

ソフトウェア開発ツール

下表に、Nios® II をサポートしているソフトウェア開発ツールをご案内します。

|

供給ベンダー |

製品 |

詳細 |

| Mentor Embedded | Sourcery CodeBench™ | Nios® II プロセッサー・ベースのエンベデッド Linux™ 向けに GNU ツールチェーンをサポートします。 |

| Altium | Tasking* Toolset | C コンパイラー、アセンブラー、リンカー、ロケーターを最適化します。 |

| MIPS (旧 FS2) | System Navigator | Nios® II プロセッサー向け System Navigator プローブは、Altera® FPGA に組み込まれた Nios® II コアの特別な機能やペリフェラルをサポートします。 |

| RocketBoard.org (オープンソース・コミュニティー) |

Linux™ ツールチェーン | RocketBoard.org(オープンソース・コミュニティー)が提供する Linux™ ツールチェーンです。 |

|

(オープンソース・コミュニティー) |

µCLinux ツールチェーン | Altera® FPGA Wiki(オープンソース・コミュニティー)が提供する µLinux ツールチェーンです。 |

表3-3: Nios® II をサポートしているソフトウェア開発ツール

4. 公開されているサイトおよびサンプルデザイン

下表に、Nios® II システム関連情報ポータルページへのリンク先をご案内します。

|

公開元 |

名称 |

概要 |

|

Nios® II Processors Support |

Altera® の Nios® II 関連資料ページ | |

|

Nios® II Embedded Design Suite |

Nios® II EDS ページ | |

| Altera® FPGA & SoC / 資料 / 資料一覧 ページ | Altera® FPGA & SoC 製品の資料一覧ページ | |

| デザイン例 | Altera® の デザイン例ページ。 このページのカテゴリで "エンベデッド・プロセッサー" をクリックすると、Nios® II のデザイン例が表示されます。 ただし、対応する Quartus® Prime (Quartus® II)のバージョンが古いサンプルが多いです(ver.7.2 ~ ver.13.1)。 Altera® MAX 10 FPGA ファミリーおよびその開発キットをターゲットにしたデザインは、Design Store で入手可能です。 |

|

| Design Store | Altera® の Design Store ページ。 条件を設定して Design Examples を探せるページです(デザインのダウンロードは無償)。 |

|

| Knowledge Base | Altera® FPGA 製品を使いこなすためのヒントや問題解決の方法などが公開されています。 | |

| マクニカ Web サイトの Nios® II 関連 技術情報 ページ | ||

| マクニカ Web サイトの Nios® II 関連 FAQ ページ | ||

| アルティマカンパニー技術サポート 技術コンテンツ: Nios® II | アルティマカンパニー技術サポート Nios® II 関連 技術コンテンツページ |

表4-1: Nios® II 関連情報のポータル