この「Quartus® ガイド」シリーズは、インテル® Quartus® Prime / Quartus® II 開発ソフトウェアをご利用になるユーザ向けの資料です。

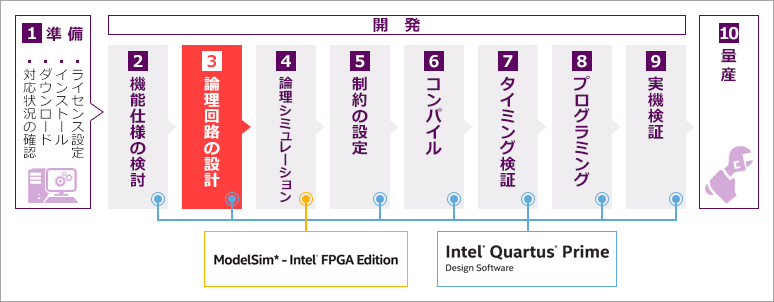

FPGA / CPLD の開発フローについては、こちら を参照してください。

説明

この資料は、FPGA / CPLD 開発の『3. 論理回路の設計』フェーズで参考になります。

Platform Designer(旧 Qsys)システム統合ツールの使い方を易しく紹介しています。

※ Qsys は v17.1 から Platform Designer へ名称変更されました。

Platform Designer システム統合ツールは、各コンポーネント(Intellectual Property (IP) ファンクションやサブシステム、ユーザ・ロジックなど)を接続するインタコネクト・ロジック(アドレス/データ・バスの接続やバス幅整合ロジック、アドレス・デコーダ・ロジック、アービトレーション・ロジックなど)を自動的に生成して、FPGA デザイン・プロセスの時間と労力を大幅に節約します。Platform Designer は FPGA に最適化されたネットワーク・オン・チップ(NoC)の新しい技術で開発されており 前世代ツールの SOPC Builder と比べて、性能の向上やデザインの再利用のしやすさ、そして検証の迅速化を実現しています。

Nios® II プロセッサ(以下、Nios® II)や FPGA デバイスに内蔵された ARM® コアを FPGA デザインに組み込む場合など最近では Platform Designer を使用することが多くあるため、本資料では簡単な使い方を説明します。

資料

「Quartus Prime ガイド - Qsys システム統合ツールの使い方 ver.16」(ツール・バージョン:Ver 16.0 向けドキュメント)

おすすめ記事/資料はこちら

Quartus® Prime 関連の記事や資料

IP 関連の記事や資料

Nios® II 関連の記事や資料

SoC FPGA 関連の記事や資料

インテル® FPGA の開発フロー/FPGA トップページ

おすすめ FAQ はこちら

おすすめセミナー/ワークショップはこちら

Quartus®Prime 入門編トライアル・コース <無料>

Nios® II入門編トライアル・コース <無料>

SoCスタートアップ・トライアル <無料>

カスタムマイコン設計トライアル ~MAX® 10 FPGA を使った組込み設計を体感!~ <無料>